Fターム[5B125EK08]の内容

リードオンリーメモリ (43,397) | 外部接続構成、外部出力情報 (1,198) | メモリの状態情報の出力 (341) | 書込状態、消去状態情報 (37)

Fターム[5B125EK08]に分類される特許

1 - 20 / 37

不揮発性半導体記憶装置

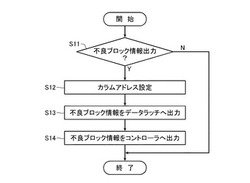

【課題】不良ブロック情報を適切に管理することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は不揮発にデータを記憶する複数のメモリセルを配列してなる複数のブロック、並びにメモリセルと接続されるワード線、及びビット線を有するメモリセルアレイと、メモリセルアレイ内に設けられ、ブロックが不良ブロックであること示す不良ブロック情報を不揮発に記憶可能に構成された不良ブロック格納領域と、ワード線を選択するロウデコーダと、メモリセルに対するデータの書き込み、消去及び読み出しを制御する制御回路とを備える。制御回路は、不良ブロック格納領域に書き込まれた不良ブロック情報をビット線を介して外部へ出力する出力動作を実行可能に構成されるとともに、外部から入力された不良ブロック情報をビット線を介して不良ブロック格納領域に書き込む第1の書き込み動作を実行可能に構成される。

(もっと読む)

半導体メモリシステム

【課題】プログラムを並列化したときに消費電流のピーク期間の重なりを防止する。

【解決手段】実施形態に係わる半導体メモリシステムにおいて、複数の半導体メモリ1の各々は、連続する複数の動作を含む内部シーケンスを実行すると共に各動作の終了後に待機期間を有し、待機期間中に次の動作の開始を予告する2ビット以上の予告信号STAをメモリコントローラ28へ通知すると共に、メモリコントローラ28から内部シーケンスの再開命令を受けたときに次の動作を開始する。メモリコントローラ28は、複数の動作の各々について、動作期間及び消費電流のピーク期間に関する管理テーブルを備え、複数の半導体メモリ1のうち所定の半導体メモリから予告信号STAを受けたとき、管理テーブルに基づいて、所定の半導体メモリに対して再開命令を通知する。

(もっと読む)

半導体装置

【課題】メモリセルの劣化がある程度進行している状態と、要求仕様を満たさなくなるまで劣化が進行した状態とを外部で認識できるようにする。

【解決手段】半導体装置1において、メモリセルMCは、閾値電圧の相違を利用してデータを不揮発的に記憶する。制御回路11は、データ消去時、メモリセルの閾値電圧が第1ベリファイ電圧以下でない場合にはメモリセルに閾値電圧を小さくするための消去電圧を印加する。制御回路は、消去電圧の印加時間が第1の判定値を超えると第1の劣化状態を表わす信号を出力し、消去電圧の印加時間が第1の判定値より大きい第2の判定値を超えると第2の劣化状態を表わす信号を出力する。

(もっと読む)

複数の独立したシリアルリンクメモリ

【課題】半導体メモリにおけるシリアルデータリンクインターフェイスとメモリバンクとの間のデータ転送を制御する装置、システム、および方法が開示される。

【解決手段】一例では、リンクがバンクと独立している、複数のシリアルデータリンクおよび複数のメモリバンクを備えるフラッシュメモリ装置が開示される。エコー信号ラインを使用して、フラッシュメモリ装置をデイジーチェーン構成においてカスケードし、メモリ装置間で連続的に通信してもよい。さらに、単一リンクを使用して複数のリンクをエミュレートする仮想複数リンク構成が記載されている。

(もっと読む)

集積化埋込型フラッシュ及びSRAMメモリを有する移動通信装置

【課題】フラッシュ及びSRAMのアクセス時間を改善し、ASICを使用する移動電話機のパワー消費を低減する。

【解決手段】改善されたアクセス時間を備えるフラッシュ及びSRAMメモリを特定用途集積回路(ASIC)の中に埋込む。フラッシュメモリシステムは、個々のフラッシュマクロの組及びフラッシュマクロにアクセスするためのフラッシュメモリコントローラ132を備えるように構成されたフラッシュメモリ列130を含む。フラッシュメモリコントローラは、フラッシュマクロの一つへ、同時にフラッシュマクロの他の一つから読出している間に、書込むための読出し間書込みユニット144,146を含む。フラッシュメモリコントローラは、また、プログラム可能な待機状態レジスタ138及びフラッシュメモリ列の異なる部分のための別々のパスワードを提供するパスワードレジスタ140を含む。

(もっと読む)

半導体集積回路装置およびメモリの管理方法

【課題】製造コストを抑制し、小型化が可能な半導体集積回路装置およびメモリの管理方法を提供する。

【解決手段】半導体集積回路装置は、不揮発性メモリと、記憶部と、演算部と、を備える。不揮発性メモリは、第1および第2の領域を有する。記憶部は、前記第1の領域に外部からプログラムをダウンロードするための第1のプログラムを記憶した。演算部は、前記第1のプログラム、および、前記第1のプログラムにより前記第1の領域にダウンロードされたプログラムを実行する。前記第1の領域は、前記ダウンロードされたプログラムにより書き込みおよび消去可能であるが、前記第2の領域は、前記ダウンロードされたプログラムにより消去できない。

(もっと読む)

不揮発性半導体記憶装置、不揮発性半導体記憶システム、および不揮発性半導体記憶装置のデータ書き換え方法

【課題】不揮発性半導体記憶装置のデータの書き換え時間を短縮する。

【解決手段】ブロック毎にデータの書き換えが可能な記憶領域と、データを退避するためのRAM4と、コントローラ3とを備えた不揮発性半導体記憶装置1において、ブロック2内の各セルの状態がイレース状態であればプログラム電圧をかけるプリプログラム過程と、ブロック内の全セルをイレースするイレース過程と、閾値電圧を均一化するポストプログラム過程とを有していて、プリプログラム過程で、ブロック内の各セルの状態を判別するのと同時にRAMへコピーし、ポストプログラム過程で、セルの書き換え後のデータがイレース状態に対応するデータであればセルのイレース後の閾値電圧を均一化するためセルにポストプログラム電圧をかけ、セルの書き換え後のデータがプログラム状態に対応するデータであればセルをプログラム状態にするためセルにプログラム電圧をかけることを特徴とする。

(もっと読む)

NANDフラッシュメモリおよびNANDフラッシュメモリへのデータ書込方法

【課題】ソケットとの接触不良によるインバリッドマークへの意図しない書き込みを防止する。

【解決手段】I/Oライン8−1〜8−Nにスイッチ11−1〜11−Nを介して抵抗(プルアップ抵抗)12−1〜12−Nの一端を接続し、プルアップ抵抗12−1〜12−Nの他端を所定の電源電位Vccに接続する。コントローラ1に、スイッチ11−1〜11−NのON/OFFモードを設定するROM書きモード設定用レジスタ10を設け、ソケットを使用してのメモリアレイ2へのプログラムの書き込み時に、スイッチ11−1〜11−NをONモードとする。

(もっと読む)

記憶装置

【課題】多値メモリセルアレイの端部において信頼性を向上させるとともに、クラスタ単位での書き込みにおける性能を向上させる記憶装置を提供する。

【解決手段】複数のメモリセルブロックを有し、メモリセルブロックはmビット(mは2以上の自然数)のデータを記憶可能に構成された複数の多値メモリセルがp行(pは3以上の自然数)のワード線と、q列(qは2以上の自然数)のビット線の交差部に配置されており、ワード線はそれぞれ第1ページ〜第mページのm個のページを有し、メモリセルブロックはn個(nは n<m×p を満たす自然数)のページを有し、すくなくとも1以上の端部ではないワード線には、m個のページの全てにページ番号が割り当てられると共にワード線の少なくとも一方の端部のワード線にページ番号が割り当てられた第1ページと、ページ番号が割り当てられない第mページとを有する記憶装置。

(もっと読む)

半導体装置

【課題】消去時間の短縮を行なうとともにデータアクセスを効率的に実行することのできる不揮発性メモリ機能を有する半導体装置を提供する。

【解決手段】コマンドレジスタ/制御回路(24)の制御のもとに、メモリセル境界領域に配置される埋込消去ゲート配線(4)に対して消去電圧を印加し、フローティングゲート(FG)と埋込消去ゲートEGの間で電荷を移動させて消去動作を行なうとき、消去電圧印加中にメモリゲート線(MGL)およびアシストゲート線(AGL)に読出選択電圧を印加してデータの読出を実行する。

(もっと読む)

情報記憶装置

【課題】 不揮発性半導体記憶手段の劣化状況を検出して、記憶情報の消失を防ぐ。

【解決手段】 不揮発性半導体記憶手段において、消去時間と消去時間の基準となる基準値とを比較し、その大小関係に応じて前記不揮発性半導体記憶手段への書込み/消去を制御する。

(もっと読む)

フラッシュメモリのデータ処理方法及び記憶装置

【課題】データコピー及び元ブロックデータ消去に伴うデータ書き込み時間の遅延を抑制できるフラッシュメモリのデータ処理方法及び記憶装置を提供する。

【解決手段】フラッシュメモリのデータ処理方法であって、データ書き込みとは異なるタイミングで、ブロックにおけるデータ書き込み状態を検出し、検出した書き込み状態が、予め設定された所定の書き込み状態に対応するデータ移行条件と合致する場合、ブロックに対応するアプリケーションの実行手段に、該当するブロックのレコードのうち、有効なレコードのデータのみを、ブロックとは別の記憶媒体に移行するタイミングである旨を通知する。そして、通知を受け、アプリケーションの移行条件と合致することでなされる実行手段からの指示に基づき、該当するブロックの有効なレコードのデータのみを、記憶媒体にコピーするとともに、データコピー元のブロックのデータを消去する。

(もっと読む)

半導体メモリ装置

【課題】不揮発性メモリにおける電源遮断時の異常を迅速に解消できるようにする。

【解決手段】半導体メモリ装置1を、フラッシュメモリ等の不揮発性メモリ2と、データの書き込みおよび消去等の制御を行う制御部3と、データの入出力を行うためのインタフェース4とにより構成する。不揮発性メモリ2の記憶領域を第1および第2のバンクB1,B2に分け、各バンクB1の状態を表すフラグをバンクB2に、バンクB2の状態を表すフラグをバンクB1に書き込む。

(もっと読む)

不揮発性半導体記憶装置及びその制御方法

【課題】 メモリセルの書き換え動作を高速に行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】 不揮発性メモリセルの複数をマトリクス状に配列してなる第1サブバンク及び第2サブバンクを備えてなるメモリセルアレイと、第1サブバンク及び第2サブバンクに共通して設けられた行デコーダと、第1サブバンク及び第2サブバンクに各別に設けられた第1列デコーダ及び第2列デコーダと、第1サブバンクに対する書き込み動作及び第2サブバンクに対する書き込みベリファイ動作のための読み出し動作を行う第1動作サイクルと、第1サブバンクに対する書き込みベリファイ動作のための読み出し動作及び第2サブバンクに対する書き込み動作を行う第2動作サイクルと、を交互に実行する制御回路を備える。

(もっと読む)

半導体記憶装置

【課題】 チップサイズの増大を抑制しつつ、任意のプロテクト領域を設定することが可能な半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、独立してデータ消去可能な最小単位であるブロックを複数有する不揮発性メモリと、前記不揮発性メモリのバッファとして機能する揮発性メモリと、各々の前記ブロックに対して実行可能な動作を制限するプロテクト情報を保持することが可能なプロテクト用SRAMと、外部から入力されたブロックアドレスに対応する前記プロテクト情報を、前記プロテクト用SRAMから読み出して設定することが可能なレジスタと、前記レジスタに設定された前記プロテクト情報に基づき、前記ブロック対して要求された動作を制限するか否かを決定する制御部と、を具備する。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積の増加を最小限に抑制しつつ消去/書込動作を十分小さな分割単位で実現するとともに、消去時間を短縮することのできる不揮発性メモリを提供する。

【解決手段】メモリセルのしきい値電圧分布状態として、物理的消去状態および論理的消去状態の2つを設ける。論理的消去状態は、メモリセルのしきい値電圧判定基準が、物理的消去状態よりも高い状態にシフトされる。物理的消去状態のメモリセルのデータ書換を行なう場合、論理的消去を行ない、そのしきい値電圧判定基準を高い電圧レベルにシフトする。論理的消去は、単にしきい値電圧判定基準の電圧レベルをシフトさせるだけであり、メモリセルの蓄積電荷は移動しないため、高速でかつ短時間に消去を行なうことができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み方法の最適化などに関する設計に利用できるデータを入手するための不揮発性半導体記憶装置を提供する。

【解決手段】データの書き換えが可能な複数の不揮発性メモリセルを書き込みの単位で配置したメモリセルアレイと、前記書き込み単位を構成する前記不揮発性メモリセルが保持するべきデータと前記不揮発性メモリセルへの書き込みのベリファイの結果とを保持するラッチと、前記書き込み単位を構成する前記不揮発性メモリセルへの書き込みと前記書き込みのベリファイとを行うシーケンスを実行する制御を行い、前回の前記シーケンスの実行により前記ラッチに保持された前記ベリファイの結果を外部に出力する制御が可能な制御部と、を有することを特徴とする不揮発性半導体記憶装置を提供する。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性メモリを搭載した半導体装置において、簡易な構成によって、外部からの電力供給の安定性が阻害された場合であっても書き込み動作等を確実に実行可能にする。

【解決手段】半導体装置1は、不揮発性メモリを含む不揮発性メモリコア10と、不揮発性メモリコア10への電力供給のモードを、外部電源から電力供給を行う第1モードと、バックアップ電源として用いられる蓄電デバイス31から電力供給を行う第2モードとで切り替えるスイッチ20とを備えている。不揮発性メモリコア10は、その動作状態を示すステータス信号を出力し、スイッチ20は、ステータス信号が示す不揮発性メモリコア10の動作状態に応じて、電力供給モードの切替を行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ固有の識別番号のように、セキュリティが必要なデータを格納できる不

揮発性半導体記憶装置を実現する。

【解決手段】記憶領域の一部または全部の領域内の、消去単位領域の管理情報領域に、前記消去単位領域の消去回数を示す情報を有し、前記情報が所定の値であるとき、チップ内の動作制御装置により、前記一部または全部の領域のワード線またはデータ線またはソース線に対して、消去に必要な電圧を印加しない。また、書き込みについても同様な制御を行う。

(もっと読む)

二重機能データレジスタ

統合されたプログラム検証の機能性を有する二重機能データレジスタを提供する。二重機能データレジスタのマスタ及びスレーブラッチ回路は、2つの異なるデータのワードを同時に保存し得る。プログラム検証動作において、マスタラッチはプログラムデータを保存し、スレーブラッチは読み取りデータを受け取り保存する。各レジスタステージの比較ロジックは、双方のラッチのデータを比較し、比較結果を前段のレジスタステージの比較結果に統合する。最後の1ビットの結果は、プログラムされなかった少なくとも1ビットの存在を示す。各ステージ内の自動プログラム抑制ロジックは、首尾よくプログラムされたビットが次の再プログラムサイクルにおいて再プログラムされることを防止する。クロック信号のロウまたはハイのアクティブ状態の論理レベルにおいて、選択的にシフト動作を開始することで、いずれかのデータワードが連続してクロックに従い出力される。  (もっと読む)

(もっと読む)

1 - 20 / 37

[ Back to top ]