Fターム[5B125FA06]の内容

リードオンリーメモリ (43,397) | 図面、表情報 (5,864) | 動作別電圧設定図、設定表 (490)

Fターム[5B125FA06]に分類される特許

1 - 20 / 490

半導体記憶装置

半導体記憶装置

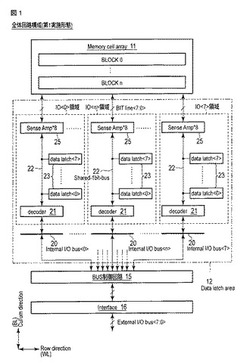

【課題】微細化に対して有利な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルが配置されるメモリセルアレイ11と、前記複数のメモリセルのデータをラッチし、前記メモリセルアレイのデータの入力または出力(I/O)ごとに分割して配置される複数のアドレス領域(IO<0>領域〜IO<7>領域)と、前記複数のアドレス領域に対応して配置され、それぞれが前記複数のアドレス領域と電気的に直列に接続される内部バス配線20と、前記内部バス配線のデータ転送を制御する制御回路15とを具備する。

(もっと読む)

不揮発性プログラマブルスイッチ

【課題】セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【解決手段】第1配線に接続される第1端子と第2配線に接続される第2端子と第3配線に接続される第3端子とを有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と第2配線に接続される第5端子と第3配線に接続される第6端子とを有する第2不揮発性メモリトランジスタと、第2配線にゲート電極が接続されたパストランジスタと、を備え、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも高い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が増加し、第2不揮発性メモリトランジスタの閾値電圧が低下し、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも低い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が低下し、第2不揮発性メモリトランジスタの閾値電圧が増加する。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

不揮発性メモリーセル

【課題】種々の回路ブロックを単一の集積回路(IC)に集約するために、不揮発性メモリーブロックをロジック機能ブロックにまとめる。

【解決手段】結合素子と第一のセレクトトランジスターを有している。結合素子は第一の伝導領域において形成されている。第一のセレクトトランジスターは、第一の浮遊ゲートトランジスターおよび第二のセレクトトランジスターに直列的に接続されており、それらは全て第二の伝導領域に形成されている。結合素子の電極および第一の浮遊ゲートトランジスターのゲートは、モノリシックに形成された浮遊ゲートである。第二の伝導領域は第一の伝導領域と第三の伝導領域の間に形成され、第一の伝導領域、第二の伝導領域、および第三の伝導領域は、ウェルである。

(もっと読む)

半導体記憶装置

【課題】インタリーブ動作を実行可能に構成され且つLMアドレススキャン動作を実行する半導体記憶装置における消費電力の削減、及び動作の高速化を図る。

【解決手段】複数のカラムのうちの少なくとも1つは、複数ビットのデータの書き込み動作の進行状況を示すLMフラグデータを記憶するためのLMカラムである。カラム制御回路の各々は、対応するメモリコアにLMカラムが存在するか否かを確認するためのLMアドレススキャン動作をする。そのLMアドレススキャン動作の結果をレジスタに格納し、その後の各種動作においては、前記データラッチ回路に保持されたデータが第1のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行する一方、前記レジスタに保持されたデータが第2のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行しない。

(もっと読む)

メモリのプログラミング方法及びメモリアレイ

【課題】クリティカル・ディメンションの変動に鈍感であり且つ高速なメモリプログラミング方法等を提供する。

【解決手段】メモリの複数のメモリセルの夫々は、ウェルと、ソース及びドレイン領域と、記憶レイヤと、ゲートとを有する。メモリセルはマトリクス状である。同じ列ドレイン領域は同じビットラインへ接続し、同じ行ゲートは同じワードラインへ接続し、同じ列ソース領域は同じソースラインへ接続する。メモリは、いずれかのメモリセルへ電気的に接続されたワードラインへ第1の電圧を印加し、そのメモリセルへ電気的に接続されたビットラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第2の電圧を印加し、そのメモリセルへ電気的に接続されたソースラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第3の電圧を印加し、複数のメモリセルへ基板電圧を印加することによって、プログラミングされる。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体メモリの情報書き換え方法

【課題】不揮発性半導体メモリの書き換え時に、適切なパルス電圧および適切なパルス幅を備える信号を印加可能な不揮発性半導体記憶装置を提供することである。

【解決手段】本発明にかかる不揮発性半導体記憶装置は、記録されている情報を所定のパルス電圧および所定のパルス幅を備える信号を印加することで書き換え可能な不揮発性半導体メモリ11と、不揮発性半導体メモリ11の書き換えを制御する書き換え制御部12と、を備える。書き換え制御部12は、不揮発性半導体メモリの総書き換え回数に基づき仮のパルス電圧および仮のパルス幅の少なくとも一つを決定する。更に、決定された仮のパルス電圧および仮のパルス幅の少なくとも一つを不揮発性半導体メモリ11の温度に基づいて補正することで、書き換え時に不揮発性半導体メモリ11に印加する信号のパルス電圧およびパルス幅の少なくとも一つを決定する。

(もっと読む)

不揮発性メモリ装置のデータリード方法、及びそれを行う装置

【課題】新たなリードパラメータで不揮発性メモリ装置をリードするリードリトライを行う方法、該方法を行う装置を提供する。

【解決手段】リードリトライ動作及び/またはその部属的なリードリトライ動作は、リードリトライ動作が保証(warranted)されるか否かを判断する前に初期化されるか、完了することができる。例えば、NANDフラッシュメモリ装置のページは、新たなリード電圧レベルをページのワードラインに印加して、リードリトライ動作でリードされうる。例えば、リードリトライ動作は、エラー訂正動作でターゲットページのデータの以前リードページのエラーを訂正不能と判断される前に、ターゲットページで行われる。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置のデータ書き込み方法

【課題】セル間干渉によるしきい値電圧の変動を低減させる。

【解決手段】不揮発性半導体記憶装置は、第1及び第2の選択ゲートトランジスタ、並びに第1及び第2の選択ゲートトランジスタ間に設けられ電気的に書き換え可能なデータを記憶する複数のメモリセルが直列接続されたメモリストリングからなるセルユニットと、メモリセルに第1の選択ゲートトランジスタ側から第2の選択ゲートトランジスタ側へ下位ページデータ及び下位ページデータに応じた上位ページデータを順次書き込むデータ書き込み手段とを備える。データ書き込み手段は、選択メモリセルに対して下位ページデータを書き込む第1の書き込み動作と、選択メモリセルに対して第2の選択ゲートトランジスタ側に隣接するn個(nは2以上の整数)の非選択メモリセルに対する第1の書き込み動作が終了した後に、選択メモリセルに対して上位ページデータを書き込む第2の書き込み動作とを行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ書き込みを高速化した不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、メモリセルアレイと、プログラム動作並びにベリファイ動作を有する書き込みループを繰り返し実行する制御回路とを備え、ベリファイ動作は、メモリセルの閾値電圧が、メモリセルの所望の閾値電圧の下限を示す本ベリファイ電圧よりも低い値で設定された予備ベリファイ電圧まで遷移したことを確認する予備ベリファイステップ、並びに、メモリセルの閾値電圧が本ベリファイ電圧まで遷移したことを確認する本ベリファイステップからなり、書き込みループは、各データに対応した1又は2以上のベリファイ動作からなり、制御回路は、所定の第1条件を具備した後、所定のデータに対応したベリファイ動作の予備ベリファイステップを省略させた書き込みループを実行する。

(もっと読む)

不揮発性半導体記憶装置

【課題】周辺回路の面積を縮小する。

【解決手段】

複数のメモリブロックの各々には、基板に対し垂直な方向に延びるように複数のメモリストリングが配列される。各メモリストリングは、複数のメモリトランジスタ及びダミートランジスタを直列接続してなる。ドレイン側選択ゲート線及びソース側選択ゲート線は、メモリブロックが選択されるときには転送トランジスタが導通することにより電圧を制御回路から供給される一方、メモリブロックが非選択とされるときは転送トランジスタが非導通状態となることによりフローティング状態とされる。ダミーワード線は、メモリブロックが選択されるときには第1の転送トランジスタが導通することにより制御回路から電圧を供給される一方、メモリブロックが非選択とされるときは第1の転送トランジスタとは別の第2の転送トランジスタにより電圧を供給される。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルに与える影響を緩和し、正確にデータを書き込むことのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、メモリセルアレイと、選択メモリセルに書き込みパルス電圧を印加するとともに非選択メモリセルに中間電圧を印加する書き込み動作、書き込みベリファイ動作及び書き込みパルス電圧を第1のステップアップ値だけ上昇させるステップアップ動作を繰り返す制御を実行する制御部とを備える。制御部は、書き込みパルス電圧の印加回数が第1の回数より少ない第1期間では中間電圧を一定の値に保ち、書き込みパルス電圧の印加回数が第1の回数以上である第2期間では中間電圧を第2のステップアップ値だけ上昇させるようにステップアップ動作を制御し、且つ、第2のステップアップ値に基づき第1のステップアップ値を決定する。

(もっと読む)

半導体記憶装置

【課題】信頼性を向上することが出来る半導体記憶装置を提供すること。

【解決手段】第1メモリセルMCと、第1ワード線WLと、第1ビット線BLに流れる第1電流を検知する第1センスアンプ12と、を具備し前記第1センスアンプ12は、第1供給部と、検出器と、前記検出器からの出力をカウントするカウンタと、を含み、前記カウンタは、第2供給部(22、31、33)と、第2蓄積部と、検知部とを具備する。

(もっと読む)

半導体記憶装置

【課題】動作信頼性を向上出来る半導体記憶装置を提供すること。

【解決手段】実施形態の半導体記憶装置1は、メモリセルMTと、複数のワード線WLと、ドライバ回路12と、制御回路15とを備える。メモリセルMTは、半導体基板20上に積層されると共に、電流経路が直列接続され、電荷蓄積層25bと制御ゲート23a〜23dとを含む。ワード線WLは、制御ゲートにそれぞれ接続される。ドライバ回路12は、選択ワード線に第1電圧VPGMを印加すると共に、第1非選択ワード線に第2電圧VPASSAを印加し、第2非選択ワード線に第3電圧VPASS、VISOを印加するプログラム動作を繰り返すことにより、選択ワード線に接続されたメモリセルMTにデータを書き込む。制御回路15は、プログラム動作が繰り返される過程において、第1電圧VPGMを上昇させ、第2電圧VPASSAを低下させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】高集積化を図ることができる不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、セルの書き込みにおいて、制御装置は複数の第2の選択ゲートトランジスタに第1電位を与えた後、第1電位よりも低い第2電位を与える。複数のビット線のうち、書き込み不十分のセルに第3電位を与え、書き込み終了に間近のセルに第3電位より高い第4電位を与え、書き込みが終わったセルに第4電位より高い第5電位を与える。制御装置は、第2電位を与えた後、複数のワード線のうち選択されたワード線に書き込み電位を与え、第1電位は、第2の選択ゲートトランジスタをオンすることにより第3電位をNANDストリングに転送する電位であり、第2電位は、第3電位をNANDストリングに転送した後、前記第2の選択ゲートトランジスタをオフする電位である。

(もっと読む)

メモリ装置およびメモリ装置の制御方法

【課題】メモリセル31が劣化した場合にも、誤り訂正回路20の回路面積を増大させることなく誤り訂正を行うことができるメモリ装置2を提供する。

【解決手段】実施の形態のメモリ装置2は、メモリ部30と、制御部11と、補正部41と、誤り検出訂正部40とを具備する。メモリ部30は、データを記憶する複数のメモリセル31からなる。制御部11は、電荷量に対応した閾値電圧を読み出すためにメモリセル31にHB読出電圧HVと、補間読出電圧AVと、を印加する制御を行う。補正部41は読み出された、閾値電圧Vthから決定されたビットデータを反転する。誤り検出訂正部40は、補正部41で反転されたビットデータを含めた所定長のデータ列を、硬判定復号符号により復号処理を行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】電源電圧の供給停止を検出せずに、かつメモリセルからデータを読み出すことなく、書き換え動作中の電源遮断が容易に検出できる不揮発性半導体記憶装置を提供する。

【解決手段】行列上にフラッシュメモリセルが配置されたメモリアレイ99は、メモリブロック8_0〜8_3に分割される。メモリブロック8_0〜8_3は、データを記憶するノーマルメモリセルNCと、消去動作の完了の有無表わすためのフラグメモリセルFCを含む。制御回路6は、メモリブロックの消去動作が終了後に、フラグメモリセルFCを書込状態に設定する。

(もっと読む)

不揮発性半導体記憶装置

【課題】高速で動作し得る不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタMTとを有するメモリセルMCがマトリクス状に配列されて成るメモリセルアレイ10と、ビット線BLの電位を制御する列デコーダ12と、第1のワード線WL1の電位を制御する電圧印加回路14と、第2のワード線WL2の電位を制御する第1の行デコーダ16と、ソース線SLの電位を制御する第2の行デコーダ18とを有し、列デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されており、第1の行デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されている。ビット線と第2のワード線とが高速で制御され得るため、メモリセルトランジスタに書き込まれた情報を高速で読み出すことができる。

(もっと読む)

半導体記憶装置及びその試験方法

【課題】ローデコーダ側に配置される転送トランジスタの特性評価を実施する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、切り替え部、第一の転送トランジスタ、第一のトランジスタ、及び第二のトランジスタが設けられる。切り替え部が第一の状態のときに第一及び第二のトランジスタがオフし、第一の転送トランジスタがオンし、切り替え部が第二の状態のとき第一及び第二のトランジスタがオンする。

(もっと読む)

1 - 20 / 490

[ Back to top ]