Fターム[5B125FA10]の内容

リードオンリーメモリ (43,397) | 図面、表情報 (5,864) | 具体的な応用機器 (416)

Fターム[5B125FA10]に分類される特許

1 - 20 / 416

メモリシステム及びそれのブロック複写方法

ホスト装置、装置、システム

メモリカード、ストレージメディア、及びコントローラ

暗号化演算装置を搭載する不揮発性半導体記憶装置

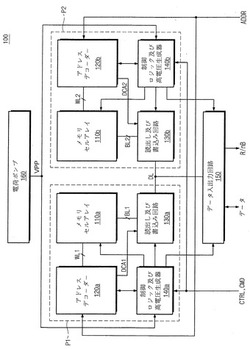

不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法

【課題】向上された動作速度を有する不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法を提供する。

【解決手段】本発明の不揮発性メモリ装置は、データのプログラム、読出し又は消去を遂行する第1プレーン、データのプログラム、読出し又は消去を遂行する第2プレーン、及び第1プレーン又は第2プレーンから共通バスを通じて伝送されるデータを外部へ出力し、外部から受信されるデータを、共通バスを通じて第1プレーン又は第2プレーンへ伝送するデータ入出力回路を含む。第1プレーンでプログラム、読出し又は消去が遂行される時、データ入出力回路は共通バスを通じて第2プレーンとデータを交換する。

(もっと読む)

メモリシステム及びそれの動作方法

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

メモリ装置

【課題】、復号効率のよいメモリカード3を提供する。

【解決手段】メモリカード3は、複数のメモリセル13Dと、HB読み出し電圧とSB読み出し電圧とを、メモリセル13Dに印加する制御を行うCPUコア11と、閾値電圧をもとにLLRテーブルから取得したLLRに基づき軟判定復号を行うECC部1と、を具備し、第1のLLRテーブル20Aから取得したLLRに基づいた復号が失敗した場合に、最高電圧の第1のHB読み出し電圧H07を中心とする閾値電圧分布を測定し、閾値電圧分布の最小頻度電圧VMと第1のHB読み出し電圧H07との差である第1のシフト値ΔV1が「負」の場合には、第2のLLRテーブル20Bから取得したLLRに基づき復号を行い、第1のシフト値ΔV1が「正」の場合には、第3のLLRテーブル20Cから取得したLLRに基づき復号を行う。

(もっと読む)

不揮発性メモリ装置のデータリード方法、及びそれを行う装置

【課題】新たなリードパラメータで不揮発性メモリ装置をリードするリードリトライを行う方法、該方法を行う装置を提供する。

【解決手段】リードリトライ動作及び/またはその部属的なリードリトライ動作は、リードリトライ動作が保証(warranted)されるか否かを判断する前に初期化されるか、完了することができる。例えば、NANDフラッシュメモリ装置のページは、新たなリード電圧レベルをページのワードラインに印加して、リードリトライ動作でリードされうる。例えば、リードリトライ動作は、エラー訂正動作でターゲットページのデータの以前リードページのエラーを訂正不能と判断される前に、ターゲットページで行われる。

(もっと読む)

記憶装置及び印刷装置

【課題】効率的なメモリーアクセスができる記憶装置及び印刷装置等を提供すること。

【解決手段】記憶装置100は、バスBSを介して接続されるホスト装置400との通信処理を行う制御部110と、ホスト装置400からのデータがシーケンシャルに書き込まれる記憶部120と、記憶部120のアクセス制御を行う記憶制御部130と、クロック信号が入力されるクロック端子TCKと、データ信号が入力されるデータ端子TDAと、リセット信号が入力されるリセット端子TRSTとを含む。制御部110は、クロック信号及びリセット信号の電圧レベルに基づいて、記憶部120に対するアクセスを制御するモードであるアクセス制御モードが通常モードであるか、或いはスキップモードであるかを判断する。記憶制御部130は、アクセス制御モードがスキップモードである場合には、スキップアドレスを開始アドレスとして記憶部120のアクセス制御を行う。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置の消去方法、不揮発性メモリ装置の動作方法、不揮発性メモリ装置を含むメモリシステム、メモリシステムの動作方法、不揮発性メモリ装置を含むメモリカード、及びソリッドステートドライブ

【課題】向上された信頼性を有する不揮発性メモリ装置、不揮発性メモリ装置の消去方法、不揮発性メモリ装置の動作方法、不揮発性メモリ装置を含むメモリシステム、及びメモリシステムの動作方法が提供される。

【解決手段】本発明の消去方法は複数のメモリセルに消去電圧を供給する段階、複数のメモリセルのワードラインに読出し電圧に読出し動作を遂行する段階、及び複数のメモリセルのワードラインの少なくとも1つのワードラインに消去検証電圧を利用して消去検証動作を遂行する段階を含む。消去検証電圧は読出し電圧より低い。

(もっと読む)

不揮発性メモリ装置

【課題】信頼性を向上させることができる不揮発性メモリ装置の提供。

【解決手段】メモリセルアレイの選択されたページからデータを読み出すか、或いはメモリセルアレイの選択されたページへ書き込むように構成されたページバッファ回路と、選択されたページに割り当てられたシードに基づいて、ページバッファ回路へ伝送されるか、或いはページバッファ回路から伝送されるデータをランダム化及びデランダム化するように構成されたランダム化及びデランダム化回路と、を有し、選択されたページは複数のセグメントで構成され、ランダム化及びデランダム化回路は、選択されたページに割り当てられたシードに基づいて選択されたページのアクセス要請されたセグメントの各々に対するランダムシークェンスを生成するように構成され、シードにしたがって反復的に生成されたランダムシークェンスに基づいて各アクセス要請されたセグメントのデータをランダム化及びデランダム化するように構成される。

(もっと読む)

不揮発性メモリ装置

【課題】 パストランジスタ間の空間確保が可能な不揮発性メモリ装置を提供する

【解決手段】 不揮発性メモリ装置100が備える行デコーダ120は、パストランジスタ部123_L、123_Rを含む。パストランジスタ部123_L、123_Rは、メモリブロック110の左右に配列される。ブロック選択信号BLKWL1によって共通ゲートを形成するパストランジスタ端Pass TR 0とパストランジスタ端Pass TR 8とは、選択的に活性化される第1駆動信号ラインSI1及び第2駆動信号ラインSI2によって独立して駆動される。互に異なるブロック選択信号BLKWLによって駆動されるパストランジスタは、1つの活性領域の上に形成され得る。これにより、1つの活性領域の上に2つのパストランジスタを形成する場合、パストランジスタ部123_L、123_Rのチャンネル方向の大きさを減らすことができる。

(もっと読む)

メモリシステム

【課題】

実施形態は、動作効率の低減を防止可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムによれば、半導体チップの内部温度とアクセス可否とを対応づけたデータを保持する第1記憶部と、前記半導体チップの内部温度を計測する温度計測部と、前記データから、計測された内部温度に対応するアクセス可否を算出し、アクセス可の半導体チップに対して、シーケンスを実行し、アクセス否の半導体チップに対して、シーケンスを実行しない制御部とを備えることを特徴とする。

(もっと読む)

メモリシステム

【課題】読み出し動作開始から読み出し動作完了までの処理時間を可及的に低減する。

【解決手段】制御部は、不揮発性メモリに格納されているデータを読み出す際、読み出し電圧管理情報に記録されている読み出し電圧の値を用いて不揮発性メモリからデータを読み出して、誤り検出部が読み出されたデータに誤りを検出したとき、誤り検出部が読み出されたデータに誤りを検出しなくなるまで読み出し電圧を変更して前記不揮発性メモリからデータの再読み出しを行い、誤り検出部が読み出されたデータに誤りを検出しなくなったとき、読み出し電圧管理情報に記録されている読み出し電圧を更新する。

(もっと読む)

不揮発性半導体記憶装置及びICカード

【課題】ピーク電流を低減する。

【解決手段】不揮発性半導体記憶装置10は、不揮発性メモリ11と、電圧発生回路24と、検知回路25とを含む。電圧発生回路24は、チャージポンプ30と、チャージポンプ30を動作させるクロックを生成するオシレータ32とを有し、かつ不揮発性メモリ11に電圧を供給する。検知回路25は、外部からの電源電圧を監視し、電源電圧が特定のレベルより低くなったことを検知する。電圧発生回路24は、電源電圧が特定のレベルより低くなった場合に、クロックの周波数を低くする。

(もっと読む)

不揮発プログラマブルロジックスイッチ

【課題】 誤動作を防ぐとともに、サイズが小さい不揮発プログラマブルロジックスイッチを提供すること。

【解決手段】 本発明の実施形態による不揮発プログラマブルロジックスイッチは、制御ゲートが第1の配線に接続され、第1のソースドレイン端が第2の配線に接続され、電荷を蓄積する膜を有する第1のメモリセルトランジスタと、制御ゲートが前記第1の配線に接続され、第3のソースドレイン端が前記第1のメモリセルトランジスタの第2のソースドレイン端に接続され、第4のソースドレイン端が第3の配線に接続され、電荷を蓄積する膜を有する第2のメモリセルトランジスタと、前記第1のメモリセルトランジスタの前記第2のソースドレイン端と前記第2のメモリセルトランジスタの前記第3のソースドレイン端にゲート電極が接続されたパストランジスタと、前記パストランジスタのウェルに基板電圧を印加する第1の基板電極を有する。

(もっと読む)

半導体記憶装置

【課題】1つの実施形態は、例えば、出荷後においてメモリセルの動作特性を変更できる半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、メモリセルアレイと記憶部と選択部と起動処理部と動作制御部とを有することを特徴とする半導体記憶装置が提供される。メモリセルアレイでは、複数のメモリセルが配列されている。記憶部は、選択される候補となる複数の動作パラメータを予め記憶する。選択部は、ユーザからの変更指示に応じて、前記複数の動作パラメータのうち前記メモリセルを動作させるために使用すべき動作パラメータを選択する。起動処理部は、ユーザからの起動指示に応じて、電源を起動するとともに、前記選択部により選択された動作パラメータを前記記憶部から読み出して使用可能な状態に設定する。動作制御部は、前記起動処理部により使用可能な状態に設定された動作パラメータを使用して、前記メモリセルを動作させる。

(もっと読む)

半導体メモリおよびシステム

【課題】 1つをメモリブロックの書き込み動作中に、別のメモリブロックの読み出し動作を実行することで、アクセス効率を向上する。

【解決手段】 半導体メモリは、複数ビットの書き込みデータおよび書き込みデータのパリティデータをビット毎に保持する複数のメモリ領域を有する複数のメモリブロックを有している。書き込みコマンドに応答して、メモリブロックの1つである書き込みメモリブロックのメモリ領域に、書き込みデータおよびパリティデータが順に書き込まれる。読み出しコマンドに応答して、書き込みメモリブロックを除くメモリブロックの1つにおいて、書き込みデータおよびパリティデータが供給されていないデータ線に対応するメモリ領域からデータが読み出され、書き込み動作により読み出させないデータが再生される。これにより、書き込み動作と並行して読み出し動作を実行できる。

(もっと読む)

半導体装置

【課題】メモリセルの劣化がある程度進行している状態と、要求仕様を満たさなくなるまで劣化が進行した状態とを外部で認識できるようにする。

【解決手段】半導体装置1において、メモリセルMCは、閾値電圧の相違を利用してデータを不揮発的に記憶する。制御回路11は、データ消去時、メモリセルの閾値電圧が第1ベリファイ電圧以下でない場合にはメモリセルに閾値電圧を小さくするための消去電圧を印加する。制御回路は、消去電圧の印加時間が第1の判定値を超えると第1の劣化状態を表わす信号を出力し、消去電圧の印加時間が第1の判定値より大きい第2の判定値を超えると第2の劣化状態を表わす信号を出力する。

(もっと読む)

ページフラッグを有する不揮発性メモリ装置、それを含む駆動方法、及びメモリシステム

【課題】データをランダム化させて格納する不揮発性メモリ装置、それのプログラム方法及び読出し方法、及びそれを含むメモリシステムが提供される。

【解決手段】本発明による不揮発性メモリ装置のプログラム方法は、第1ページプログラム動作の時、前記第1ページプログラムの可否に関連された情報を有する第1ページフラッグをプログラムする段階及び第2ページプログラム動作の時、前記第2ページプログラムの可否に関連された情報を有する第2ページフラッグをプログラムする段階を含む。上述したように本発明による不揮発性メモリ装置は、データをランダム化させて格納することによって、データの信頼性を向上させる。また、本発明による不揮発性メモリ装置は、読出し動作の時、ページのプログラムの可否にしたがってランダム化の可否を決定することによって、読出しエラーを減らし得る。

(もっと読む)

1 - 20 / 416

[ Back to top ]