Fターム[5C580BB04]の内容

ガス放電表示管の制御 (14,416) | 駆動回路構成の特徴 (1,593) | レベルシフト回路 (26)

Fターム[5C580BB04]に分類される特許

1 - 20 / 26

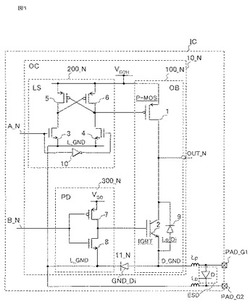

半導体集積回路

【課題】絶縁ゲート電界効果トランジスタ構造を有するトランジスタのスクリーニングを可能として、出力端子にサージ電圧が印加された場合のサージ電圧のエネルギー吸収能力を改善する。

【解決手段】集積回路ICは、トランジスタ2を含む出力バッファ回路100とプリドライバ300とを具備する出力回路10を内蔵する。出力バッファ回路100の出力OUTは、IC外部と接続可能である。プリドライバ300の出力はトランジスタ2の絶縁ゲート電界効果トランジスタ構造の制御ゲートに接続され、ソース領域と基板領域は第1接地線D_GNDに接続され、プリドライバ300は第2接地線L_GNDに接続される。第1と第2の接地線D_GND、L_GNDは第1と第2の接地端子PAD_G1、G2を介してIC外部と接続可能とされる。出力回路10は、第1と第2の接地線D_GND、L_GNDの間に接続された出力保護ダイオード11を更に具備する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】高耐圧回路の素子破壊を防止する際、半導体チップ面積の増大を軽減する。

【解決手段】半導体集積回路ICは、高電源電圧で動作する高耐圧回路100、200と低電源電圧で動作する低耐圧回路300、400を内蔵する。入力信号Aに応答して、高耐圧回路の第1素子5と第2素子3はオン状態とオフ状態に、低耐圧回路の第3素子7と第4素子8はオフ状態とオン状態に制御される。この状態において、高電源電圧供給端子に所定レベルのサージ電圧が供給される。この状態で、初期サージ電流が第1素子5と第2素子3の容量を介して低耐圧回路の出力端子Yに流入する。出力端子Yの電圧降下は、高耐圧回路の第2素子3のターンオン電圧に設定される。第2素子3はオフ状態からオン状態に制御されて、サージ電圧のエネルギーを吸収するサージ吸収電流が第1素子5と第2素子3に流入する。

(もっと読む)

プッシュプル型駆動回路

【課題】レベルシフト回路を多数必要としない高電圧出力のプッシュプル型駆動回路を実現する。

【解決手段】プッシュプル型駆動回路は、ハイサイドの複数のトランジスタ(11,12)のスイッチング動作を制御する制御回路(3)と、制御回路(3)が複数のトランジスタ(11,12)をオフ制御するときに出力する制御信号を複数のトランジスタ(11,12)がオフ可能な第1の電圧にシフトして複数のトランジスタのいずれか一つ(11)のゲートに入力するレベルシフト回路(4)と、レベルシフト回路(4)の出力が第1の電圧のときには当該出力を残りのトランジスタ(12)のゲートに入力する一方、それ以外のときには制御回路(3)の制御に従って残りのトランジスタ(12)の各ゲート入力をハイインピーダンスおよび複数のトランジスタ(11,12)がオン可能な第2の電圧のいずれか一方に設定する導電選択回路(5)とを備えている。

(もっと読む)

レベルシフト出力回路

【課題】レベルシフタによる面積の増加や電力の増加がなく、高耐圧P型FETの電流能力を分散させるレベルシフト出力回路を提供すること。

【解決手段】レベルシフタ40は、電源NVDD3と電源NGND間に接続され、入力信号Sin1“L”に応じて出力信号“L”を出力し、入力信号Sin2“H”に応じて出力信号“H”を出力する。高圧インバータ50−1〜50−zは、電源NVDD3と電源NGND間に接続され、制御信号Sctr1“L”とレベルシフタ40からの出力信号“L”とに応じて出力信号“H”を出力し、制御信号Sctr2“H”とレベルシフタ40からの出力信号“H”とに応じて出力信号“L”を出力する。高耐圧P型FET60−1〜60−zは、電源NVDD3と電源出力ノードNVDD2間に接続され、それぞれ、高圧インバータ50−1〜50−zからの出力信号“L”に応じて電圧VDD3を供給する。

(もっと読む)

表示駆動装置、モジュールパッケージ、及び画像表示装置

【課題】半導体チップの箇所による電気的特性ばらつきを判別できるようにする。

【解決手段】駆動信号を出力する複数の出力パッド16を、半導体チップ10の一辺に沿って配置する。また、PN接合ダイオード20aで互いに接続された2つの第1及び第2測定パッド20b,20cをそれぞれ有した複数の観測端子部20を形成する。そして、少なくとも2つの観測端子部20は、互いに離間して、出力パッド16が配置された一辺に沿って配置する。

(もっと読む)

プラズマディスプレイ装置

【課題】大幅な設計変更を必要とせず、簡単な回路の付加と制御信号のタイミング変更だけで、下り傾斜波形電圧の到達電圧を切換えて安定した書込み放電を発生させる。

【解決手段】維持パルス発生回路52は、電力回収用のコンデンサC76から走査電極へ向かう電流経路を形成する第1のスイッチQ77と、高圧側の電圧にクランプする第2のスイッチQ71と、走査電極から電力回収用のコンデンサC76へ向かう電流経路を形成する第3のスイッチQ78と、低圧側の電圧にクランプする第4のスイッチQ74とを有し、初期化波形発生回路60は、緩やかに下降する傾斜波形電圧を発生する下り傾斜波形発生回路66と、第3のスイッチQ78の制御信号および第4のスイッチQ74の制御信号の少なくとも1つに依存して決まる所定の電圧を発生する電圧発生回路67と、下り傾斜波形発生回路66の出力と所定の電圧とを比較する比較回路68とを有する。

(もっと読む)

半導体集積回路

【課題】電力回収用スイッチの電流能力の低下を抑える。

【解決手段】電力回収用スイッチ1は、PchFET1aと、NchFET1bとが直列接続される。また、PchFET1aとNchFET1bとは、同時にオンまたはオフされる。出力の立ち上がり時には、出力端子4に接続するNchFET1bのソース電極はGND電位、ゲート電極にはVDHが印加され、初期段階でゲート・ソース間の電圧をVDHとすることができる。出力の立ち下がり時には、初期段階でPchFET1aのソース電極はVDH電位、ゲート電極はGND電位となり、初期段階でゲート・ソース間の電圧をVDHとすることができる。いずれの場合も初期段階において、ゲート・ソース間にはVDHが印加されるので、FETの最大の電流能力を得ることができる。

(もっと読む)

プラズマディプレイ装置、及び半導体装置

【課題】片側駆動で使用するアドレスドライバICを一部低耐圧化することでチップサイズを小型化し、低コスト化する。

【解決手段】複数の表示セルを含むプラズマディスプレイ装置であって、Y電極と、隣接するY電極との間で、維持放電を行う電極であって、基準電位に接続されたX電極と、アドレス電極と、を備え、アドレス電極を駆動するアドレスドライバのハイレベルを出力する第2のスイッチ素子(Q1)の耐圧を、ローレベルを出力する第1のスイッチ素子(Q2)より低くする。このため、第2のスイッチ素子(Q1)とアドレス電極との間にダイオード(Di)を挿入する。

(もっと読む)

プラズマディスプレイ装置

【課題】プラズマディスプレイ装置の維持パルスの立上り時間を精度よく制御するとともに誤った制御信号を禁止する保護機能を付加する。

【解決手段】維持パルス発生回路は、維持電源の高電圧側に表示電極を接続する第1のクランプスイッチQ51と、維持電源の低電圧側に表示電極を接続する第2のクランプスイッチQ54とを有し、第1のクランプスイッチQ51を制御する第1のクランプ制御信号Sig51と第2のクランプスイッチQ54を制御する第2のクランプ制御信号Sig54との少なくとも1つはフォトカプラ87を介して伝達され、フォトカプラ87の発光ダイオードD87の一方の端子に第1のクランプ制御信号Sig51を入力し発光ダイオードD87の他方の端子に第2のクランプ制御信号Sig54を入力する。

(もっと読む)

表示駆動装置、表示装置および表示駆動方法

【課題】表示セルを駆動する際に、無駄な信号出力に要する時間を削減するとともに消費電力を低減する。

【解決手段】表示画像に応じたハイレベルまたはローレベルの入力信号が、所定のタイミングでラッチ回路130に取り込まれ、その信号レベルが保持される。そして、ラッチ回路130からの出力信号は、遅延/レベルシフト回路150によって、より大きな振幅の信号に変換されて、表示セルを駆動するための駆動信号が生成される。また、ラッチ回路130により保持された信号レベルに応じた駆動信号が出力された後、ラッチ回路130により次の入力信号が取り込まれてその信号レベルが保持されるまでの期間において、データクリア部131によって、ラッチ回路130に保持された信号レベルがクリアされて、ラッチ回路130からの出力信号がローレベルに設定される。

(もっと読む)

半導体集積回路

【課題】スイッチングノイズや電磁波ノイズの発生を抑制可能で回路面積の小さい半導体集積回路を提供する。

【解決手段】比較回路CP1〜CP4により、自身のラッチ回路LT1〜LT4の出力状態と両隣の出力ビット回路部1〜4におけるラッチ回路LT1〜LT4の出力状態とを比較し、その比較結果と、次のデータにおける比較回路CP1〜CP4の比較結果とを比較回路M1〜M4で比較し、1つおきの出力ビット回路部1〜4でのみ有効になる遅延切替回路D1〜D4は、比較回路M1〜M4の比較結果より、自身のラッチ回路LT1〜LT4の出力状態と、両隣の出力ビット回路部1〜4におけるラッチ回路LT1〜LT4の出力状態とが同一の出力状態で揃って遷移したことを検出した場合、自身の出力信号の伝達遅延時間を両隣の出力ビット回路部1〜4よりも長くする。

(もっと読む)

PDP駆動回路及びPDP駆動用半導体集積回路

【課題】回路規模及び制御配線の増大を回避し、PDP駆動回路の一斉動作時の雑音やそれに伴うEMIを低減する。

【解決手段】PDP駆動用半導体集積回路は、入力信号を入力信号の振幅よりも大きい振幅を有する高電圧パルスに変換して出力するPDP駆動回路を複数備える。複数のPDP駆動回路の各々が、互いに異なるタイミングで動作して高電圧パルスを順次出力する順次動作機能と、複数のPDP駆動回路の各々が全て同じタイミングで動作して高電圧パルスを一斉に出力する一斉動作機能とを有する。順次動作時及び一斉動作時の双方において、高電圧パルスの電圧レベルがロウレベルからハイレベルに変化する速度及びロウレベルからハイレベルに変化する速度のうちの少なくとも1つを制御する。

(もっと読む)

プラズマディスプレイ装置

【課題】安全性を考慮し、かつ大画面パネルであっても駆動でき、比較的簡単な回路構成で維持電極に第1の電圧および第2の電圧を印加する維持電極駆動回路を備えたプラズマディスプレイ装置を提供する。

【解決手段】維持電極駆動回路は、維持電源の電圧よりも低い第1の電圧および第2の電圧を発生する電圧発生回路60を備え、電圧発生回路60は、第1のインダクタL62を有するダウンコンバータで構成されかつ第1の電圧を発生する第1電圧発生部62と、この第1電圧発生部62の第1のインダクタL62と誘導結合した第2のインダクタL64を有しかつ第1の電圧に出力電圧を重畳して第2の電圧を発生させる第2電圧発生部64とを備えた。

(もっと読む)

出力回路及び多出力回路

【課題】出力端子からツェナーダイオードを通してレベルシフト回路へ負荷電流が流れる経路を遮断して、出力端子を完全にハイインピーダンスにする出力回路を提供する。

【解決手段】出力回路は、ハイサイドトランジスタ13と、ローサイドトランジスタ14と、ゲート保護回路10と、レベルシフト回路8と、プリドライバ回路7とを備える。レベルシフト回路8は、ハイサイドトランジスタ13をオフさせてから所定時間経過後に、出力端子4からレベルシフト回路8への電流径路を遮断状態にする。

(もっと読む)

プラズマ表示装置及びその駆動装置

【課題】プラズマ表示装置及びその駆動装置を提供する。

【解決手段】スイッチング制御信号を出力するスイッチング制御部512、スイッチング制御部512の出力端に連結され、スイッチング制御信号によりオン/オフされる第1スイッチングトランジスタ514、第1端が維持電圧を供給する第1電圧入力端と連結され、第1スイッチングトランジスタのオン/オフに対応して、オン/オフ制御される第2スイッチングトランジスタ516、及び一端が第2スイッチングトランジスタ516の第2端及び第1電極の接続点に連結され、第2スイッチングトランジスタの導通時維持電圧に対応して、充電される電圧を第1電極に供給するキャパシタを含む駆動装置を提供する。これにより、一つの電圧変換装置で維持電圧から所望のレベルの電圧を生成することはもちろん所定期間の間だけ電極に供給するように制御できる。

(もっと読む)

半導体集積回路装置

【課題】高集積化及び高信頼性を実現した半導体集積回路装置を提供する。

【解決手段】第1電圧電源で動作するCMOS回路により形成された信号で、上記第1電圧電源よりも高い第2電圧電源に対応した出力信号を形成する出力回路を制御する半導体集積回路装置である。上記CMOS回路のうち、そのラッチアップ状態によって上記出力MOSFETを同時にオン状態にさせる可能性を持つ回路部分のPチャネルMOSFETとNチャネルMOSFETは、絶縁性分離手段により互いに電気的に分離された半導体領域に振り分けて形成する。上記第1回路部分を除く第2回路部分は、PチャネルMOSFETとNチャネルMOSFETとが絶縁性分離手段により電気的に分離された同じ半導体領域内に形成する。

(もっと読む)

PDPの駆動装置

【課題】PDPの駆動装置の電力回収率を向上する。

【解決手段】出力バッファ回路10は、2つのNchMOSトランジスタQ1、Q2を縦続接続したトーテムポール回路で構成され、2つのMOSトランジスタの接続点(VOUT)を表示セルのデータ電極C0に接続する。レベルシフト回路11は、CMOS回路で構成され、出力バッファ回路10を駆動する。電荷回収回路13は、出力バッファ回路10の電源VDD2に接続され、表示セルの放電後のデータ電極C0に残存する電荷を回収して再利用する。電源制御回路12は、電荷回収回路13における回収・再利用のサイクルの一部期間において、レベルシフト回路11の電源電圧が出力バッファ回路10の電源電圧とMOSトランジスタの閾値電圧との和を超えるように制御する。

(もっと読む)

プラズマディスプレイパネルの駆動装置及びその方法

【課題】アドレス放電特性を改善できるプラズマディスプレイパネルの駆動装置及びその方法を提供する。

【解決手段】前記スキャンバイアス電圧のバイアスレベルを傾斜的に変化させるレベル変換部20と、前記変化されたバイアスレベルを有する前記スキャンバイアス電圧をスキャン電極に順次印加するスキャン駆動部22と、を含んでプラズマディスプレイパネルの駆動装置を構成する。

(もっと読む)

駆動回路および表示装置

【課題】 容量性負荷を駆動する出力回路のスイッチング素子の駆動能力、特に低電圧領域での駆動能力を改善して電力回収効率を向上させ得ること。

【解決手段】 駆動回路は、正の制御電圧に応じて導通する第1スイッチング素子NT1と第2スイッチング素子NT2とが直列接続されたトーテムポール構造を有するトーテムポール回路22と、第1スイッチング素子NT1の他方の被制御電極に接続されておりトーテムポール回路22を介して容量性負荷Cpを充放電する電力回収回路19と、第1スイッチング素子NT1および第2スイッチング素子NT2の各々のスイッチングを制御する出力制御回路20,21とを備える。

(もっと読む)

プラズマディスプレイ装置および半導体集積回路装置

【課題】隣接アドレス信号の変化方向に影響されることなくアドレス信号の遷移時間をほぼ一定にし、画素の誤点灯および電磁放射の発生を防止するとともに消費電力が少なくて済むプラズマディスプレイ装置のアドレス電極駆動回路を提供する。

【解決手段】2つの直列形態の出力MOSFETQ11とQ12を備え、プラズマディスプレイ装置の信号線のいずれかに接続される出力回路(64A)と、定電流用トランジスタQ1を含み、入力信号に応じて上記出力MOSFETの一方(Q11)をオフ状態からオン状態にさせるときに該出力MOSFETのゲート容量に定電流を流す駆動回路63Aを設ける。

(もっと読む)

1 - 20 / 26

[ Back to top ]