Fターム[5D044EF01]の内容

デジタル記録再生の信号処理 (102,243) | 記録信号処理 (4,772) | AD変換 (26)

Fターム[5D044EF01]に分類される特許

21 - 26 / 26

記録装置

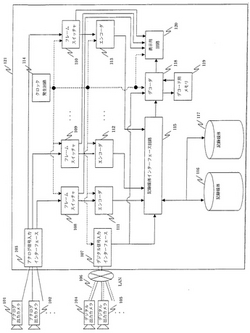

【課題】 既存のアナログ方式の記録装置を活用することができ、コスト削減及びアナログ・デジタル混合記録の性能向上を図ることができる記録装置を提供する。

【解決手段】 フレームスイッチャ108は、アナログ信号入力インターフェース103からの信号とクロックとの同期をとる。エンコーダ111は、フレームスイッチャ108からの信号をデジタル信号に変換する。変換されたデジタル信号及びデジタル信号入力インターフェース107からのデジタル信号は、記録媒体インターフェース回路115を通じて記録媒体116,117に転送されてデジタル記録される。アナログ信号は表示器用回路120で処理されアナログ表示され、デジタル信号はデコーダ118でデコードされる際にデコード用メモリ119で一時的にバッファリングされ、アナログカメラからの信号よりも遅れて表示される。

(もっと読む)

ディジタル信号記録装置及びディジタル信号記録再生装置

【課題】

ディジタル信号を受信して記録再生するシステムにおける記録装置、記録再生装置及び受信記録装置において、アナログ信号のテレビジョン信号をディジタル信号に変換して記録再生する機能も持つディジタル信号の記録再生装置を提供する。

【解決手段】

アナログ映像信号とアナログ音声信号のA/Dコンバータ、圧縮するためのエンコーダ、圧縮映像信号と圧縮音声信号の多重化回路、受信したディジタル信号か圧縮された多重化信号かを選択する選択回路を設ける。

(もっと読む)

信号記録装置および信号記録方法

【課題】復数のテレビ番組を同時に、電波形式を保持したまま記録再生することができる放送波の記録再生方式を提供すること。

【解決手段】記録する複数のテレビチャネルの放送信号をバンドパスフィルタで切り出し、各々を周波数変換して周波数軸上の0Hzから順に周波数軸上に重ならないように配置する。この信号をA/D変換し、HDD等に記録する。チャネル情報および時刻情報も同時に記録する。再生する際は、チャネルと時刻を指定することにより、記録されているデータから所望のチャネル・時刻のデータを取り出して、D/A変換器を介して出力し、これを所望のチャネルの周波数帯に変換する。この信号をテレビで視聴する。波形等化処理など記録データの加工も可能である。簡単な構成で複数チャネルを同時に記録可能である。

(もっと読む)

記録再生装置

【課題】

ディジタル放送系とアナログ放送系両方の記録再生を行える記録再生装置において、既存の構成を効率的に活用することにより、システム変更によるコスト負担等を最小限にすることを実現する。

【解決手段】

上記課題を解決するために、例えば、デジタル放送系とアナログ放送系双方が接続部により接続され、両方の放送系を受信可能な記録再生装置において、該接続部を介して入力されたアナログ放送系の信号をデジタル放送系に備わったデジタル放送系記録部への記録する際に、デジタル放送系側の制御部により制御させるように構成する。

(もっと読む)

光ディスクシステムの信号処理装置

【課題】光ディスク再生処理に適した光ディスクシステムの信号処理装置を提供する。

【解決手段】アナログ信号処理部とデジタル信号処理部とを有した光ディスクシステムの信号処理装置において、前記アナログ信号処理部は、光ディスクから得られる再生処理を行うための光検出信号のレベルを、所定の基準レベルへと一致させるべく可変利得に基づいて増幅する利得可変増幅部を有しており、前記デジタル信号処理部は、前記利得可変増幅部により増幅された光検出信号をサンプリングしてA/D変換を行うA/D変換部と、前記A/D変換後の光検出信号のレベルと前記基準レベルとの比較を行う比較部と、前記比較の結果に応じてカウンタクロックをもとにカウントアップ又はカウントダウンを行うカウンタによって構成され、前記カウンタのカウント値に基づいて前記可変利得を調整する利得調整部と、を有しており、前記A/D変換におけるサンプリング周波数と前記カウンタクロックのクロック周波数の比率を可変させること、とする。

(もっと読む)

再生装置及び再生方法

【課題】 HFMグルーブを再生するときに生じるノイズの影響を低減する。

【解決手段】 HFMグルーブに光を照射することによって得られたRF信号を、A/D変換回路42が、ウォブルPLL部32からwck3が供給される毎にA/D変換して、加算器61に出力する。加算器61は、ミュート回路63の制御に応じて、A/D変換回路42から供給されたディスクデータ0.5ビット分に相当するの信号のうち、積分区間として設定された範囲の信号について、サンプリングクロックが供給される毎に信号値を累算することにより、積分区間の信号を積分する。加算器61によって加算された値は、累算器62に供給される。積分区間の積分が終了すると、レジスタ53が、累算器62に記憶されている値を、アドレスECCデコーダ回路24に供給する。

(もっと読む)

21 - 26 / 26

[ Back to top ]