Fターム[5E336BB15]の内容

プリント板への電気部品等の実装構造 (16,219) | プリント板の種類 (1,572) | 材料又は性質限定されたプリント板 (698) | 材料限定されたプリント板 (529) | 合成樹脂を主体とするもの (388)

Fターム[5E336BB15]の下位に属するFターム

合成樹脂組成の特定 (62)

Fターム[5E336BB15]に分類される特許

321 - 326 / 326

プリント配線板およびコンデンサ

【課題】 コンデンサを内蔵すると共に内蔵コンデンサとの接続を適切に取ることができるプリント配線板を提供する。

【解決手段】 チップコンデンサ20をコア基板30内に収容する。チップコンデンサ20は、銅めっき膜29を被覆した第1、第2電極21,22に銅めっきによりなるバイアホール46で電気的接続を取ってある。銅めっき膜29により第1、第2電極21,22の表面が平滑になり、接続層40に非貫通孔43を穿設した際に樹脂残さが残らず、バイアホール46とチップコンデンサ20との接続信頼性を高めることができる。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】 ループインダクタンスを低減できるプリント配線板及び該プリント配線板の製造方法を提供する。

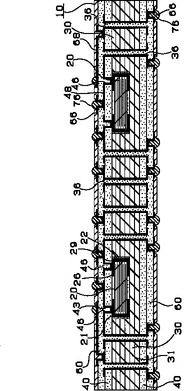

【解決手段】 プリント配線板10内にチップコンデンサ20を配置するため、ICチップ90とチップコンデンサ20との距離が短くなり、ループインダクタンスを低減することができる。また、厚いコア基板30内にチップコンデンサ20を収容するためプリント配線板を厚くすることがない。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】 ループインダクタンスを低減できるプリント配線板及びプリント配線板の製造方法を提供する。

【解決手段】 プリント配線板10内にチップコンデンサ20Aを配置するため、ICチップ90とチップコンデンサ20Aとの距離が短くなり、ループインダクタンスを低減することができる。また、厚いコア基板30内にチップコンデンサ20A、チップ抵抗20B、チップコイル20Cを収容するためプリント配線板を厚くすることがない。コア基板30内にチップ抵抗20B、チップコイル20Cを収容するため、プリント配線板の高集積化を実現できる。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】 ループインダクタンスを低減できるプリント配線板及びプリント配線板の製造方法を提供する。

【解決手段】 プリント配線板10内にチップコンデンサ20Aを配置するため、ICチップ90とチップコンデンサ20Aとの距離が短くなり、ループインダクタンスを低減することができる。また、厚いコア基板30内にチップコンデンサ20A、チップ抵抗20Bを収容するためプリント配線板を厚くすることがない。コア基板30内にチップ抵抗20Bを収容するため、プリント配線板の高集積化を実現できる。

(もっと読む)

高周波半導体装置及びその装置を用いた無線装置

【課題】 フリップチップ実装した高周波回路チップの特性劣化を防止すると共に、低損失を実現できる高周波半導体装置及びその装置を用いた無線装置を提供する。

【解決手段】シリコン基板11上に誘電体薄膜層13を積層してなる実装基板10を設ける。前記実装基板10のシリコン基板11にエッチング孔部18を設ける。前記シリコン基板11に接する誘電体薄膜層13に接地用導体層12を形成する。前記誘電体薄膜層13の上面にマイクロストリップ線路部(伝送線路部)14を形成する。前記マイクロストリップ線路部14上にバンプ16を介してフリップチップ実装し、エッチング孔部18に対応する位置に高周波回路チップ15を配置した。

(もっと読む)

回路基板

【課題】 内部配線パターンを電源/グランド層によりシールドすることにより特性インピーダンスやクロストークノイズの影響を改善でき、また厚さを薄く形成できる回路基板を提供する。

【解決手段】 コア基板1の両面に内部配線パターン2が形成されており、該内部配線パターン2の上に絶縁樹脂層3を介して電源/グランド層5が各々形成されてなる回路基板4であって、表層の絶縁樹脂層3がドライエッチングにより除去されて形成された凹部6に露出する内部配線パターン2に電子部品7が表面実装可能になっている。

(もっと読む)

321 - 326 / 326

[ Back to top ]