Fターム[5F003BS00]の内容

バイポーラトランジスタ (11,930) | セルファライン (117)

Fターム[5F003BS00]の下位に属するFターム

Fターム[5F003BS00]に分類される特許

1 - 6 / 6

半導体装置の製造方法

【課題】本発明の実施形態は、ベース層の幅を狭く形成しエミッタ層の不純物濃度を高くした低雑音特性を有する半導体装置の製造方法を提供することを目的とする。

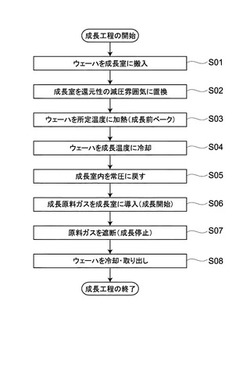

【解決手段】一実施形態に係る半導体装置の製造方法は、第1導電型の第1半導体層の上に第2導電型の第2半導体層を成長する半導体装置の製造方法であって、前記第1半導体層の表面を常圧よりも低い圧力の還元性雰囲気に曝して熱処理する工程(S02〜S04)と、前記第1半導体層の表面上に、前記第2半導体層を常圧の雰囲気でエピタキシャル成長する工程(S05〜S07)と、を備えたことを特徴とする。

(もっと読む)

選択的エピタキシまたは選択的注入の使用による、炭化ケイ素におけるセルフアライントランジスタおよびダイオードトポロジー

【課題】SiC内に縦型ダイオードおよびトランジスタを作る方法が提供される。

【解決手段】この発明に従った方法は、マスク(たとえば機構を素子にエッチングするために以前使用されたマスク)を選択的エピタキシャル成長または選択的イオン注入用に使用する。このように、静電誘導トランジスタおよびバイポーラ接合トランジスタのゲート領域およびベース領域が、セルフアラインプロセスで形成可能である。プレーナダイオードおよびプレーナエッジ終端構造(たとえばガードリング)を作る方法も提供される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板の表面をトレンチ構造にしてベース領域及びベース電極を設け、デバイスサイズを小型化、高集積化することができる半導体装置及び該半導体装置の製造方法を提供する。

【解決手段】シリコン基板10は、N型不純物として、例えば、アンチモンが含有され、コレクタ領域RCを形成している。シリコン基板10の表面には、複数の凹部10a、10a、…を形成してある。各凹部10aを除くシリコン基板10の表面の一部には、エミッタ領域REが各凹部10aで離隔されるように形成してあり、コレクタ領域RCの上側であって、各凹部10aの底面及び側面、並びにエミッタ領域REの下側には、ベース領域RBを形成してある。エミッタ領域REにはN型不純物としてのリンが、ベース領域RBにはP型不純物としてのボロンが含有されている。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】ベース抵抗が小さく、最大発振周波数などの高周波特性が優れ、低雑音なバイポーラトランジスタおよびその製造方法を提供する。

【解決手段】Siコレクタ層3a上に、SiGeスペーサ層4a、傾斜SiGeベース層4b、Siキャップ層5が形成され、Siキャップ層5上にエミッタ引き出し電極7が形成され、エミッタ引き出し電極7およびそのサイドウォール直下を除いたSiGeスペーサ層4a、傾斜SiGeベース層4b、Siキャップ層5にボロン注入でベース引き出し電極11が形成され、リンをSiキャップ層5中に拡散してエミッタ拡散層5aが形成され、ボロンをSiコレクタ層3a中に拡散して外部ベース拡散層1cが形成され、エミッタ拡散層5aの直下の真性ベース領域Bint に対して、ベース引き出し電極11と外部ベース拡散層1cで構成される外部ベース注入領域Bexを自己整合的に形成し、ベースリンク領域を削除し、ベース抵抗を低減できる。

(もっと読む)

バイポーラトランジスタ及びその製造方法

本発明は、低減したコレクタ直列抵抗及び低減したコレクタと基板間の静電容量のために、改良された性能を有するバイポーラトランジスタを提供するものである。該バイポーラトランジスタは、リソグラフィ技術で達成し得ない寸法に大きさを低減することができる突起部(5)を含む。突起部(5)は、コレクタ領域(21)及びベース領域(22)を備え、該コレクタ領域(21)は、第一コレクタ接続領域(3)の第一部分を覆い且つ電気的に接続する。第二コレクタ接続領域(13)は、第一コレクタ接続領域(3)の第二部分を覆い、突起部(5)の側壁を覆う絶縁層(10,11)により突起部(5)から分離される。ベース領域(22)との接触は、突起部(5)に隣接して、絶縁層(14)で第二コレクタ接続領域(13)から分離されるベース接続領域(15)により提供される。コレクタコンタクト(31)とベースコンタクト(32)が、第二コレクタ接続領域(13)の露出部分上と、除去されない一部のベース接続領域(15)上に同時に形成される。  (もっと読む)

(もっと読む)

バイポーラ半導体構成要素、特にバイポーラ・トランジスタ、および対応するバイポーラ半導体構成要素の製造方法

本発明は、バイポーラ半導体素子、特にバイポーラ・トランジスタ、および対応するバイポーラ半導体構成要素の製造方法に関する。本発明の方法は、下記のステップ、すなわち、半導体基板(1)上に第1の導電型(p)の第1の半導体エリア(32,34)を形成するステップと、前記半導体エリア(32,34)上に前記第1の導電型(p+)の接続エリア(40)を形成するステップと、前記接続エリア(40)上に第1の絶縁エリア(35”)を形成するステップと、前記半導体エリア(32,34)の少なくとも一部を露出するために、前記第1の絶縁エリア(35”)および接続エリア(40)内にウィンドウ(F)を形成するステップと、前記接続領域(40)を絶縁するために、前記ウィンドウ(F)内に側壁スペーサ(80)を形成するステップと、前記側壁スペーサ(80)および前記周囲の第1の絶縁エリア(35”)の一部をカバーするために、第2の導電型(n+)の第2の半導体エリア(60)を形成するステップと、前記接続エリア(40)と前記第2の半導体エリア(60)との間にギャップ(LS)を形成するために、前記周囲の第1の絶縁エリア(35”)および前記側壁スペーサ(80)を除去するステップと、第2の絶縁エリア(100)により前記ギャップ(LS)を封止し、一方、前記封止したギャップ(LS)内に気体雰囲気または真空雰囲気を導入するステップとを含む方法。  (もっと読む)

(もっと読む)

1 - 6 / 6

[ Back to top ]