Fターム[5F003BS04]の内容

バイポーラトランジスタ (11,930) | セルファライン (117) | サイドエッチ (17)

Fターム[5F003BS04]に分類される特許

1 - 17 / 17

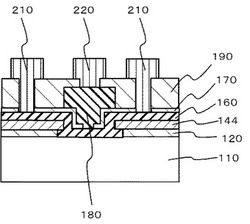

半導体装置の製造方法

【課題】パターン形成不良が発生することを抑制する。

【解決手段】まず、N型コレクタとなる基板110上に、第1開口部(不図示)を有するシリコン酸化膜120を形成する。次いで、シリコン酸化膜120及び第1開口部に露出した基板110の表面上に第1絶縁膜を形成する。次いで、第1絶縁膜をエッチバックすることにより、シリコン酸化膜120の第1開口部における側壁のみに、第1絶縁膜を残存させて、側壁部を形成する。次いで、シリコン酸化膜120等の上に、ベース引出部144となるポリシリコン膜を形成する。次いで、ポリシリコン膜上に、第2開口部(不図示)を有する第2絶縁膜を形成する。次いで、第2絶縁膜をマスクとして、ポリシリコン膜のうち、第2開口部により露出している部分を酸化してシリコン酸化膜に変化させる。次いで、シリコン酸化膜に変化させた部分を選択的に除去する。次いで、側壁部と第2絶縁膜を選択的に除去する。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの動作速度を高速化できるようにした半導体装置の製造方法を提供する。

【解決手段】単結晶Si基板1に設けられたn型のコレクタ層20と、コレクタ層20の表面の周辺部上に設けられたSiO2膜21と、SiO2膜21を覆ってコレクタ層20の表面の中央部に接合するp型のベース層30と、を有し、ベース層30は、コレクタ層20の表面の中央部上に設けられた単結晶SiGe膜31aと、SiO2膜21を覆うように単結晶SiGe膜21上に積層された単結晶Si膜35aとを含む。ベース層30とコレクタ層20との接合領域60がコレクタ層20の表面の中央部に限定されるため、接合面積を小さくすることができ、ベース層とコレクタ層との間の容量CBCを低減することができる。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】ヘテロ接合バイポーラトランジスタのエミッタメサがより正確に形成できるようにする。

【解決手段】第1エミッタ電極107bの側部には、例えば酸化シリコンからなる庇部108が形成され、また、少なくともキャップ層106を含んで構成されたエミッタメサの露出している側面から庇部108の下部の領域のレッジ構造部105aにかけて形成された、例えば窒化シリコンからなる被覆層109が形成されている。被覆層109が、庇部108の側面,庇部108の下面,エミッタメサの側部,およびレッジ構造部105aの上にかけて形成されている。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】エミッタメサの加工精度を損ねることなく、HBTの高速性および信頼性が向上できるようにする。

【解決手段】エミッタメサの部分の側面およびレッジ構造部105aの表面には、これらを被覆するように、SiNからなる第1絶縁層108が形成されている。また、第1絶縁層108の周囲には、酸化シリコンからなる第2絶縁層109が形成されている。第2絶縁層の下端部には、レッジ構造部1105aが形成されている領域より外側に延在し、第1絶縁層108およびレッジ構造部105aの側方のベース層104との間に空間を形成する庇部109aが形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】寄生容量を低減しつつ、トランジスタが形成される半導体層に歪応力を与える。

【解決手段】半導体層3に形成されたコレクタ層3aの表面および裏面にストレス印加層5を形成し、ストレス印加層5を介して埋め込み絶縁層6上に配置されたベース層9をコレクタ層3aの側壁に選択的に形成し、ベース層9の側壁を絶縁膜10から露出させる開口部12を形成し、開口部12を介してベース層9の側壁に接続されたエミッタ層13aを埋め込み絶縁層6上に形成する。

(もっと読む)

半導体素子の製造方法

【課題】 偶発的に生成される層を異方性エッチングすることにより、エッチングを行う時間によるエッチングのばらつきを改善し、かつ任意の層を異方性エッチングで一定量エッチングすることにより、回り込みエッチングの制御性の向上を図ることを実現する。

【解決手段】 第1の層の表面に第2の層を積層したものに、前記第1の層を横方向にエッチングする半導体素子の製造方法において、前記第2の層側から前記第1の層側に向かって縦方向に異方性エッチングを行うステップと前記第1の層を横方向に等方性エッチングを行うステップとを有することを特徴とする。

(もっと読む)

バイポーラ型トランジスタ及びバイポーラ型トランジスタの製造方法

【課題】ベース引き出し用電極とベース領域との接続抵抗を低抵抗化できる技術の提供。

【解決手段】半導体基板上に、第1導電型のコレクタ領域、第1絶縁膜、第2導電型を有するベース引き出し用電極、及び第2絶縁膜をこの順で設け、第2絶縁膜及びベース引き出し用電極の一部をエッチングして、第1絶縁膜の表面を露出させ、開口部の側壁に、成長防止用絶縁膜を形成する。露出した第1絶縁膜をエッチングして、前記コレクタ領域の表面を露出させる。露出したコレクタ領域上に、ベース領域を選択エピタキシャル成長により形成する。ベース領域形成工程の後、前記成長防止用絶縁膜を除去する。その後、開口部の側壁に、第2導電型の不純物が高濃度でドープされた低抵抗化用側壁を形成する。低抵抗化用側壁を被覆するように絶縁性の分離膜を形成し、エミッタ層を、開口部の底部でベース領域と接する様に、開口部に埋めこむエミッタ層形成工程と、を具備する。

(もっと読む)

バイポーラトランジスタの製造方法

【課題】コレクタ層、ベース層、エミッタ層およびエミッタコンタクト層となるべき各半導膜を含む半導体多層膜を成長した後に、炭素添加ベース層の正孔濃度を増加できるバイポーラトランジスタの製造方法を提供する。

【解決手段】OMVPE装置内のサセプタSに基板2を載置し、基板2上にサブコレクタ膜30、コレクタ膜50、およびベース膜60をエピタキシャル成長する。ベース膜60に炭素が添加される。次に、基板2を温度Tに維持し、エミッタ膜70およびエミッタコンタクト膜80を成長する。次いで、原料ガスの供給を停止し基板2を温度TAに維持する。ここで、T<TA≦600℃といった関係が成り立つ。これにより、ベース膜60内の水素原子が気相中へと脱離し、同膜60内の炭素原子の活性化率が向上する。

(もっと読む)

バイポーラ半導体構成要素、特にバイポーラ・トランジスタ、および対応するバイポーラ半導体構成要素の製造方法

本発明は、バイポーラ半導体素子、特にバイポーラ・トランジスタ、および対応するバイポーラ半導体構成要素の製造方法に関する。本発明の方法は、下記のステップ、すなわち、半導体基板(1)上に第1の導電型(p)の第1の半導体エリア(32,34)を形成するステップと、前記半導体エリア(32,34)上に前記第1の導電型(p+)の接続エリア(40)を形成するステップと、前記接続エリア(40)上に第1の絶縁エリア(35”)を形成するステップと、前記半導体エリア(32,34)の少なくとも一部を露出するために、前記第1の絶縁エリア(35”)および接続エリア(40)内にウィンドウ(F)を形成するステップと、前記接続領域(40)を絶縁するために、前記ウィンドウ(F)内に側壁スペーサ(80)を形成するステップと、前記側壁スペーサ(80)および前記周囲の第1の絶縁エリア(35”)の一部をカバーするために、第2の導電型(n+)の第2の半導体エリア(60)を形成するステップと、前記接続エリア(40)と前記第2の半導体エリア(60)との間にギャップ(LS)を形成するために、前記周囲の第1の絶縁エリア(35”)および前記側壁スペーサ(80)を除去するステップと、第2の絶縁エリア(100)により前記ギャップ(LS)を封止し、一方、前記封止したギャップ(LS)内に気体雰囲気または真空雰囲気を導入するステップとを含む方法。  (もっと読む)

(もっと読む)

ヘテロ接合型バイポーラトランジスタとその製造方法

【課題】 ヘテロ接合型バイポーラトランジスタにおいて、ベース面積ないしはベース・コレクタメサ面積の縮小化を図って高速性を高めることができるようにする。

【解決手段】 ベースメサないしはベース・コレクタメサ4の上面に、ベース電極とエミッタメサとが平面的に配置形成されて、エミッタメサ7上のエミッタ電極8の周縁部8eとベースメサないしはベース・コレクタメサ4の周縁部4eを自己整合する構成とする。

(もっと読む)

ヘテロ接合半導体装置及びその製造方法

【課題】 半導体層間の接合の端面におけるリーク電流を抑え、かつ、水分の侵入や放熱不足の問題を解消できるパッシベーション膜を備えたヘテロ接合半導体装置及びその製造方法を提供すること。

【解決手段】 半絶縁性基板1の上にメサ構造に加工した半導体層2〜6を形成する。エミッタメサおよびベース・コレクタメサの端部に凹部11および12を形成し、これらの凹部にそれぞれ絶縁性有機膜13および14を形成して、エミッタ層5の端面とベース層4との界面、およびベース層4とコレクタ層3との界面を絶縁性有機膜で被覆する。さらに、半導体層2〜6を被覆する緻密な無機パッシベーション膜15を、例えばプラズマCVD法による窒化シリコン膜によって形成し、開口部に電極7〜9を形成する。HBT10では、接合の端面が絶縁性有機膜13および14によって被覆されているので、接合部にプラズマダメージが生じることはない。

(もっと読む)

バイポーラトランジスタの形成方法

本発明はバイポーラトランジスタを形成する方法に関するものであり、この方法は次の工程を含む。すなわち、この方法は、第1導電型(n)のコレクタ領域(25)を含む半導体基板(1)を設ける工程であって、このコレクタ領域が基板に埋め込まれ、かつコレクタ領域の上面が露出する構成の工程と、単結晶ベース領域(30;32;120)を設ける工程と、第2導電型(p)のベース接続領域(40;160)をベース領域(30;32;34;120,130)の上に設ける工程と、絶縁領域(35;35’’;170)をベース接続領域(40;160)の上に設ける工程と、開口(F)を絶縁領域(35;35’’;170)及びベース接続領域(40;160)に形成してベース領域(30;32;34;120,130)を少なくとも一部露出させる工程と、絶縁サイドウォールスペーサ(55’;80;180)を開口に設けてベース接続領域(40;160)を絶縁する工程と、単結晶エミッタ層(60a)がベース領域(30;32;34;120,130)の上に、そして多結晶エミッタ層(60a)が絶縁領域(35;35’’;170)及びサイドウォールスペーサ(55’;80;180)の上に形成される構成のエミッタ層(60a,60b)を異なる構造に成長させてパターニングする工程と、そして熱処理工程を実施する工程と、を含む。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置の製造方法として、縦型バイポーラトランジスタの底部に、形状良く低抵抗層を設ける方法を提供する。

【解決手段】2重SOI基板を用意する工程と、ディープトレンチを形成する工程と、ディープトレンチを埋め込む工程と、開口部54を設ける工程と、空孔部56を設ける工程と、多結晶シリコン層80を堆積する工程と、バイポーラトランジスタを形成する工程とを有している。開口部を設ける工程では、ドライエッチングを行って、バイポーラトランジスタ被形成領域55の、第2埋め込み酸化膜40を露出させる。空孔部を設ける工程では、ウェットエッチングにより、バイポーラトランジスタ被形成領域内の第2埋め込み酸化膜を除去する。多結晶シリコン層を堆積する工程では、上述の工程で形成された、互いに連通している開口部及び空孔部に多結晶シリコン層を堆積する。

(もっと読む)

半導体装置

【課題】 バイポーラトランジスタの高速動作を可能にする。

【解決手段】 半導体基板2に設けられた第1導電型のコレクタ領域と、コレクタ領域上に設けられた第2導電型のエピタキシャル層を含む第2導電型のベース層16と、ベース層の表面領域に設けられた第1導電型のエミッタ領域28と、半導体基板上にベース層の側面を覆うように設けられベース層と同層であってかつベース層の膜厚の2乃至6倍の膜厚を有するベース引き出し電極20と、を備えている。

(もっと読む)

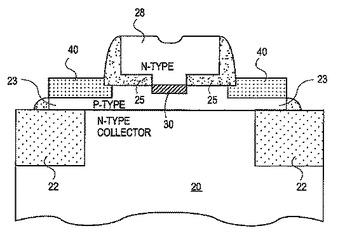

改善された外部ベース領域を備えたバイポーラ接合形トランジスタ及びその製造方法

バイポーラトランジスタ及びその製造方法に関する。第1のエピタキシャル層(23)上への第2の、より高濃度にドープされたエピタキシャル層の成長によって、外部ベース領域(40)が形成される。第2のエピタキシャル層は上にあるポリシリコンエミッタ台座(28)の下まで広がり、かつ、この台座(28)から絶縁される。  (もっと読む)

(もっと読む)

HBTの製造方法

【課題】 オーバエッチングがべ一ス層まで及ぶことがなく、高速化を図ったHBTの製造方法を提供する。

【解決手段】 コレクタ層とベース層が同じエッチング液でエッチングされる材質で形成されている場合において、

を含んでいる。

(もっと読む)

半導体装置およびその製造方法ならびに不純物注入方法

【課題】 高周波特性の優れた半導体装置を提供する。

【解決手段】 コレクタ層10と、コレクタ層10上に形成された真性ベース層20と、真性ベース層20の一部と接触するようにして形成された外部ベース層30と、真性ベース層30上に形成されたエミッタ層40と、エミッタ層40上に形成されたエミッタ引出し部42とを備え、外部ベース層30が含有する第2導電型不純物の濃度は、外部ベース層30のうちのエミッタ引出し部42に近い領域36よりも、真性ベース層20の一部と接触している領域32の方が高いことを特徴とする、半導体装置100である。

(もっと読む)

1 - 17 / 17

[ Back to top ]