Fターム[5F003BS06]の内容

バイポーラトランジスタ (11,930) | セルファライン (117) | 多結晶利用 (51)

Fターム[5F003BS06]に分類される特許

1 - 20 / 51

半導体装置の製造方法

【課題】バイポーラトランジスタの動作速度を高速化できるようにした半導体装置の製造方法を提供する。

【解決手段】単結晶Si基板1に設けられたn型のコレクタ層20と、コレクタ層20の表面の周辺部上に設けられたSiO2膜21と、SiO2膜21を覆ってコレクタ層20の表面の中央部に接合するp型のベース層30と、を有し、ベース層30は、コレクタ層20の表面の中央部上に設けられた単結晶SiGe膜31aと、SiO2膜21を覆うように単結晶SiGe膜21上に積層された単結晶Si膜35aとを含む。ベース層30とコレクタ層20との接合領域60がコレクタ層20の表面の中央部に限定されるため、接合面積を小さくすることができ、ベース層とコレクタ層との間の容量CBCを低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSプロセスへの導入が容易で、エミッタ−ベース間のリーク電流(電界強度)を低減し、ノイズやサージ電圧の影響を受けにくい高性能な半導体装置とその製造方法の提供。

【解決手段】導電膜をマスクとして、2回のイオン注入を行ってエミッタを形成する。第2エミッタ領域111bは、低濃度の不純物イオン注入によって形成し、第1エミッタ領域111aは、高濃度の不純物イオン注入によって形成する。その結果、エミッタの周縁部に低濃度の第2エミッタ領域が形成され、電界が緩和され、リーク電流が低減する。また、導電膜とエミッタ電極116とが接続され、ノイズの影響を受けにくくなる。

(もっと読む)

半導体装置の製造方法及び半導体集積回路装置

【課題】本発明は、簡素な工程で、デバイスの特性を均一化することができる半導体装置の製造方法及び半導体集積回路装置を提供することを目的とする。

【解決手段】半導体基板40の表面の所定領域41に、LOCOS酸化膜70を形成するLOCOS酸化膜形成工程と、

該LOCOS酸化膜70と前記半導体基板40の表面の境界を覆うように、ポリシリコン膜90を形成するポリシリコン形成工程と、

該ポリシリコン膜90をマスクとして、前記半導体基板40の表面にイオンの打ち込みを行い、前記半導体基板40の表面に、不純物領域60を形成するイオン打ち込み工程と、を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

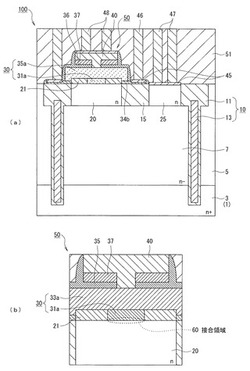

【課題】非選択エピタキシャル法により半導体層を形成しても、エミッタとベースとを確実に接続して高い信頼性を確保することができる半導体装置及びその製造方法を提供する。

【解決手段】非選択エピタキシャル成長法により、ベース開口部8の内壁を覆うようにシリコン酸化膜7の全面にSiGe膜9を成長させる。このときの成膜条件としては、ベース開口部8内において、底部9aが単結晶からなり、側壁部9b等のその他の部位が多結晶となると共に、側壁部9bの膜厚が底部9aの膜厚の1.5倍以下になる成膜条件を選択する。このような非選択エピタキシャル成長では、原料ガスとして、モノシラン、水素、ジボラン及びゲルマンを用いる。このとき、モノシラン及び水素の各流量は、夫々20sccm、20slmとする。また、成長温度を650℃、ジボランの流量を75sccmに設定し、ゲルマンの流量を35sccmに設定する。

(もっと読む)

半導体装置およびその製造方法

【課題】 CMOS製造プロセスを使用しても、バイポーラトランジスタの適切な駆動能力や温度特性を得ることが可能な半導体装置を提供する。

【解決手段】 縦型バイポーラトランジスタ90aとMOSトランジスタ90bからなる構成であって、縦型バイポーラトランジスタの少なくともベース領域は、エッチングにより表面から掘り下げることでMOSトランジスタ90bのウェル20b深さよりも浅くなっている。このためバイポーラトランジスタに必要とされる特性を独立さえて作り込むことが可能である。

(もっと読む)

半導体装置の製造方法

【課題】高精度のセルフアライメント構造を形成して半導体層に拡散層を形成する不純物元素のイオン注入を行うことにより、特性の向上を図る半導体装置を製造する半導体装置の製造方法を提供する。

【解決手段】各拡散層形成領域7〜9を相互に位置決めするイオン注入制御開口部13〜14を形成する工程を施した後に、各拡散層毎にイオン注入開口部29,30を形成するイオン注入マスク層形成工程と、各イオン注入開口部から不純物元素をイオン注入して各拡散層を形成する拡散層形成工程を実施する。イオン注入制御開口部が各拡散層形成工程におけるセルフアライメント構造を構成して各拡散層が形成される。

(もっと読む)

第二のポリ層の形成後に二重ポリバイポーラトランジスタの2つのレベルをドーピングするプロセス

【課題】

単結晶半導体材料よりエミッタドーパントに対して少なくとも1桁大きい材料の層の速い横方向拡散特性を用いる減少されたマスクの組とインプラントの複雑さを有する(高周波数応用)相補的バイポーラトランジスタ構造の製造プロセスを提供する。

【解決手段】

別のベースとエミッタポリ層がドープされずに形成される。それからあるデバイスのエミッタポリと他のデバイスのベースポリのエッジとはドーパントマスクを介して露出され、同時にドープされる。エミッタドーパントはエミッタポリの表面内に直接入り、ここでそれはベース上に位置し、それと接触している。ベース接触ドーパントは外因性ベースを形成するために高い拡散係数を有する材料の層を含むベースポリのエッジ内に入り、その層を通り抜けて迅速に横方向に拡散し、それからコレクタ材料(例えばアイランド)表面内に下方に拡散する。第二のマスクは第二のデバイスのエミッタと第一のデバイスのベースポリのエッジを露出するようパターン化され、それからドープされる。

(もっと読む)

半導体装置の製造方法

【課題】外部ベース層に起因する製造歩留まりの低下を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1上にコレクタ層2を形成する。このコレクタ層2の表面にLOCOS膜からなる素子分離層3に周囲を囲まれた活性領域A1を形成する。この素子分離層3は、平坦部3bと、この平坦部3bと活性領域A1との間の傾斜部3aとを有する。そして、素子分離層3の平坦部3b上にシリコン酸化膜4と多結晶シリコン膜5とからなる保護膜9を形成する。この保護膜9は素子分離層3の平坦部3b上に端部を有するように形成される。そして、その一部を外部ベース層として用いるSiGe層6aおよびシリコン膜7aを活性領域A1の表面上から保護膜9の上に跨って形成する。

(もっと読む)

選択エピタキシープロセス制御

【課題】 プロセスチャンバ内に含む基板表面上にシリコン含有物質を選択的に且つエピタキシャル的に形成する方法が提供される。

【解決手段】 一つ以上の実施形態において、プロセスチャンバの圧力を、基板上に物質を堆積させる間では下げ、基板から物質をエッチングする間では上げる。実施形態によれば、第1ゾーンに流されるガス量と第2ゾーンに流されるガス量の比を得るようにプロセスガスが第1ゾーンと第2ゾーンを通ってチャンバへ流される。一つ以上の実施形態において、第1ゾーンは内部半径方向ゾーンであり、第2ゾーンは外部半径方向ゾーンであり、内部ゾーンガス流と外部ゾーンガス流との比はエッチングの間より堆積の間の方が小さい。一つ以上の実施形態によれば、選択的エピタキシャルプロセスは、エピタキシャル層の所望の厚さが成長するまで、堆積と、その後のエッチングプロセスと、所望によるパージのサイクルを繰り返すステップを含む。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの製造歩留まりを向上する。

【解決手段】半導体基板Subの主面上に、バイポーラトランジスタのコレクタを構成するコレクタ層CL、ベースを構成するベース層BLおよびキャップSi層BCL、およびエミッタを構成するエミッタ層ELが設けられている。このうち、ベース層BLとしてSiGe層を選択性エピタキシャル成長によって形成した後、キャップSi層BCLとしてSi層を非選択性エピタキシャル成長によって形成する。

(もっと読む)

接合型電界効果トランジスタ及びその製造方法及び半導体装置

【課題】コレクタエピタキシャル層を薄膜化した高速バイポーラトランジスタを搭載した集積回路中に所望の高耐圧J−FETを混載可能とした半導体装置及びその製法を提供すること。

【解決手段】P型の単結晶Si基体などの第1導電型の半導体基体2上にシリコン半導体層などの第2導電型の半導体層3を積層し、この半導体層3中にAs(ヒ素)等の第2導電型の不純物によってソース領域12及びドレイン領域13を形成し、さらにこの半導体層3上に、シリコン・ゲルマニウム層によってP型の第1導電型不純物(例えば、ホウ素など)を有するゲート領域14を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】金属膜を必要以上に薄く形成しなくても、LOCOSエッジ付近での金属膜とベース絶縁膜との過度な合金化を防止できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】エミッタ領域の基板1上からLOCOS層15B上にかけてシリコンゲルマニウム層51を連続して形成する。次に、エミッタ59領域のシリコンゲルマニウム層51上にエミッタ59を形成する。そして、エミッタ59が形成された基板1上にシリコン酸化膜を形成し、次に当該シリコン酸化膜をエッチバックすることによって、エミッタ59の側面にサイドウォール61Aを形成する。その後、基板1上にTiを形成し熱処理を施して、チタンシリサイド膜67を形成する。サイドウォール61Aを形成する工程では、LOCOSエッジ90上にサイドウォール61Bを付随的に形成する。

(もっと読む)

半導体装置の製造方法

【課題】従来の製造方法においては、オーバーエッチングによりコンタクト底部の表面荒れが引き起こされ、それにより半導体装置の特性ばらつきが増大してしまう。

【解決手段】P型シリコン基板1に形成されたトレンチの底部に設けられたコレクタ領域4を有するバイポーラトランジスタを形成する。P型シリコン基板1上に層間絶縁膜23を形成する。トレンチの上部の層間絶縁膜23を途中までエッチングすることにより、コレクタコンタクト用開口の一部30を形成する。トレンチの上部の層間絶縁膜23を上記底部に達するまでエッチングすることにより、コレクタコンタクト用開口の残りの部分32を形成する。コレクタコンタクト用開口の残りの部分32の形成は、エミッタコンタクト用開口25およびベースコンタクト用開口27の形成と同時に実行される。

(もっと読む)

半導体装置およびその製造方法

【課題】従来は、コレクタ抵抗の低減およびコレクタ−エミッタ間耐圧の向上の双方を達成することが困難であった。

【解決手段】半導体装置1は、SOI基板10(半導体基板)と、SOI基板10の表層に設けられたコレクタ領域22とコレクタ引上領域26と、コレクタ領域22とコレクタ引上領域26に挟まれて設けられたコレクタ引出領域28と、コレクタ領域22の上にベース領域32を介して設けられ、コレクタ領域22およびベース領域32と共にバイポーラトランジスタを構成するエミッタ領域34と、を備えている。ここで、コレクタ引出領域28は、コレクタ領域22よりも不純物濃度が高い。

(もっと読む)

半導体装置の製造方法およびエミッタポリシリコン電極構造をもつバイポーラトランジスタの電流増幅率の調整方法

【課題】ポリシリコンエミッタ電極構造の縦型NPNバイポーラトランジスタの電流増幅率を、何らの工程を付加することなく制御し、低コスト化とバイポーラトランジスタの高周波数応答特性とを両立させる。

【解決手段】低温による(400℃)のエミッタポリシリコン190の形成時に、真性ベース140とポリシリコンエミッタ190間に界面酸化膜(自然酸化膜)が成長する。その後、エミッタ150を形成するための熱処理温度を、820℃〜910℃の範囲で調整することによって、界面酸化膜の状態と電子のパイルアップ状態を制御し、これによって、電流増幅率を微調整する。

(もっと読む)

ヒューズ素子及びヒューズ素子を備えた半導体装置並びに半導体装置の製造方法

【課題】より低い電圧の印加によって溶断可能であって、しかも溶断に要する熱量を低減可能なヒューズ素子、及びヒューズ素子を備えた半導体装置、並びに半導体装置の製造方法を提供する。

【解決手段】ヒューズ素子は、半導体基板上に少なくともシリコンと、このシリコンよりも融点が低い元素とで形成した導電層と、この導電層の上面に形成した金属シリサイド層とで形成する。シリコンよりも融点が低い元素はゲルマニウムとする。特に、半導体基板には、上面に金属シリサイド層を設けたシリコン−ゲルマニウム層からなるベース引き出し電極を備えたバイポーラトランジスタが形成されており、導電層はバイポーラトランジスタにおけるシリコン−ゲルマニウム層の形成にともなってヒューズ素子部分に形成されたシリコン−ゲルマニウム層で形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】エミッタからベース電極間の抵抗が低減され、高速動作が可能であり、高性能のバイポーラトランジスタを有する半導体装置を提供する。

【解決手段】半導体基体上に形成された絶縁膜の開口を含むように、シリコン層9A,9C、シリコンとゲルマニウム及び/又はカーボンとを有する層9B、により成るシリコン混晶層9によって形成されたエピタキシャルベース領域を有するバイポーラトランジスタが形成されて成り、シリコン混晶層9の最上層9Cがシリコン層であり、シリコン混晶層9から成るベース領域のうち、単結晶シリコン混晶層上及び多結晶シリコン混晶層上に、多結晶シリコン膜10を介してコバルトシリサイド11が形成されて成る半導体装置を構成する。

(もっと読む)

半導体デバイスの製造方法及び当該方法により得られる半導体デバイス

本発明は、基板(11)と、エミッタ領域(1)、ベース領域(2)及びコレクタ領域(3)を有する少なくとも1つのバイポーラトランジスタを備える半導体本体(12)とを有する半導体デバイス(10)の製造方法であって、当該半導体本体(12)に、前記コレクタ領域とエミッタ領域(1、3)のうちの一方の領域(3)を形成する第1の半導体領域(13)を形成し、半導体本体(12)の表面上には、第1の絶縁層(4)、多結晶半導体層(5)及び第2の絶縁層(6)から成る層のスタックを形成し、該スタックに開口(7)を形成し、その後に、非選択的エピタキシャル成長によって、更なる半導体層(22)を堆積し、開口(7)の底面上の単結晶の水平部分がベース領域(2)を形成し、開口(7)の側面上の多結晶の垂直部分(2A)は多結晶半導体層(5)に接続し、その後に、開口(7)の側面に平行にスペーサ(S)を形成し、そしてエミッタ及びコレクタ領域(1、3)のうちの他方の領域(1)を形成する第2の半導体領域(31)を前記スペーサ(S)の間に形成する、半導体デバイスの製造方法に関する。本発明によれば、上記方法は、前記更なる半導体層(22)を堆積する前に、前記第2の絶縁層(6)に、その下に在る半導体層(5)の端部(5A)から張り出して突出して見える端部(6A)を設けることを特徴とする。この方法により、費用効率の高い、良好な高周波特性を有するバイポーラトランジスタデバイスを得ることができる。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型PNPトランジスタにおいて、高いアーリー電圧と大きなコレクタ電流能力を両立させる。

【解決手段】縦型PNPトランジスタにおけるP型コレクタ領域5bの上部に、外部ベース領域12を取り囲む形状で、前記第1のコレクタ領域5bより濃度の高いP型分離チャンネルストッパー領域8aと第2のコレクタ領域8bを形成することによって、真性ベース領域14直下のP型コレクタ領域5bによってアーリー電圧が高まり、低抵抗の第2のコレクタ領域8bによってコレクタ抵抗が下がり、コレクタ電流を大きくすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ベース抵抗の低減とアーリー電圧の増加を併せて実現しうる半導体装置およびその製造方法を提供する。

【解決手段】外部ベース層51の領域にカーボンを添加し、外部ベース用ボロン注入時に発生する点欠陥生成を防止するように設定したものである。

(もっと読む)

1 - 20 / 51

[ Back to top ]