Fターム[5F004EA32]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | 異なる領域を同時にエッチング (59)

Fターム[5F004EA32]に分類される特許

1 - 20 / 59

半導体装置の製造方法

【課題】レジスト層、中間層、レジスト層のパターン形状をさらに良好にする半導体装置の製造方法を提供する。

【解決手段】下層フォトレジスト7、無機材料の中間層8、上層フォトレジスト9を形成し、上層フォトレジスト9をパターニングして上層レジストパターン9aを形成し、半導体基板1をチャンバー内の下部電極上に設置し、チャンバー内に二酸化硫黄ガス、酸素ガスを有する第1反応ガスを導入してプラズマを発生させるとともに下部電極への高周波電力の供給を切断して上層レジストパターン9aをトリミングし、第1反応ガスを第2反応ガスに置換するとともに下部電極に高周波電力を供給して上層レジストパターン9aをマスクにして中間層8をエッチングして中間層パターン8aを形成し、第2反応ガスを第3反応ガスに置換してプラズマを発生させるとともに下部電極に高周波電力を供給して中間層パターン8aをマスクにして下層フォトレジスト層7をエッチングする。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

半導体素子の作製方法

【課題】エッチング深さが異なる形状を簡単に、且つ精度よく加工できる半導体素子の作製方法を提供する。

【解決手段】開口部幅の異なる領域毎に、半導体のエッチングの進行、またはポリマーの生成のどちらか一方のみが発現するように前記開口部幅が設定された開口部を有するマスク1900を半導体表面に形成すると共に、マスクの周辺に周辺窓1701を有する周辺マスク1700を形成する第1の工程と、メタンプラズマおよび水素プラズマをマスクが形成された半導体表面に照射する第2の工程を有し、マスク1900が、第1のパターンを有す第1のマスク部1910と、第1のマスク部上に形成され、第1のマスク部のマスク厚よりも厚く、第1のパターンの開口部幅を画定する第2のパターンを有す第2のマスク部1920とからなり、周辺マスクの窓領域が第1のパターンの回折格子方向周辺に配されるようにした。

(もっと読む)

半導体素子の作製方法

【課題】同一ウエハ面内でエッチング深さが異なる形状を容易に加工することができる半導体素子の作製方法を提供する。

【解決手段】開口部幅の異なる領域毎に、半導体表面のエッチングが進行する第1の状態、または半導体表面にポリマーが生成される第2の状態のどちらか一方のみが発現するように前記開口部幅が設定された開口部1902,1903,1904を有するマスク1900を半導体1801表面に形成すると共に、マスク1900の周辺にマスクの開口部に供給される水素プラズマ濃度を制御するための周辺窓を有する周辺マスクを形成する第1の工程と、メタンプラズマおよび水素プラズマをマスクが形成された半導体表面に照射する第2の工程を有するようにした。

(もっと読む)

半導体素子の作製方法

【課題】同一ウエハ面内で素子ごとにエッチング深さが異なる形状を簡単に、且つ精度よく加工することができる半導体素子の作製方法を提供する。

【解決手段】開口部幅の異なる領域毎に、半導体表面のエッチングが進行する第1の状態か、半導体表面にポリマーが生成される第2の状態のどちらか一方のみが発現するように前記開口部幅が設定された開口部1901を有する第一のマスク1900を半導体表面に形成すると共に、第一のマスクの周辺に第一のマスクの開口部に供給される水素プラズマ濃度を制御するための第二のマスクを形成する第1の工程と、メタンプラズマおよび水素プラズマを第一のマスク1900および第二のマスクが形成された半導体表面に照射する第2の工程を有するようにした。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】実施形態によれば、ホールの深さのばらつきを防ぐ半導体装置の製造方法及び半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、複数の第1の開口と第1の開口よりも密に並んだ複数の第2の開口とを有するマスクを用いて層間絶縁層61をドライエッチングし、第1の開口の下で下地層10に達する第1のホールと、第2の開口の下で下地層10に達する第2のホール41とを同時に形成する工程を備えている。第1のホールは他の第1のホールとは接することなく下地層10に達する。ドライエッチングの開始後、複数の第2の開口のそれぞれの下に複数のホールhが形成され、ドライエッチングの進行に伴って、複数のホールhは少なくとも開口端を含む上部42で互いにつながる。

(もっと読む)

半導体素子の作製方法

【課題】エッチング面積を変えずにマスク面積を小さくする、同一面内でエッチング深さが異なる形状を容易に加工することができる半導体素子の作製方法を提供すること。

【解決手段】エッチングされる領域のマスク端からの距離は、マスク幅が1μm以上でほぼ一定の値を示す。このことは、マスク上のマスク端から1μmまでの領域に存在する水素プラズマが開口部に拡散してエッチングに寄与することを示す。このとき、マスク上のマスク端から1μm以上の領域に存在する水素プラズマはエッチングに寄与することなくマスク上から脱離するものと考えられる。そのため、本発明の選択エッチングにおいてはマスクの幅は1μm以上あればエッチング領域のマスク端からの距離を十分に得られる。また、半導体素子の高密度集積における素子間隔が10μm程度であることを考慮すると、マスク幅は1μm以上10μm以下で有効である。

(もっと読む)

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

デュアルドープゲートの用途におけるプロフィル制御とN/Pローディングを改善する方法

【課題】プラズマエッチングチャンバ内でデュアルドープゲート構造をエッチングするための方法を提供する。

【解決手段】エッチングされるポリシリコンフィルムを保護するパターンを設ける工程、次いで、プラズマが点火され、保護されていないポリシリコンフィルムのほぼすべてがエッチングされる。次いで、シリコン含有ガスを導入しつつポリシリコンフィルムの残りをエッチングする。また、エッチング処理中にシリコン含有ガスを導入するよう構成されたエッチングチャンバ。

(もっと読む)

半導体表面におけるパターンの作製方法

【課題】所望のパターンを有する第1のマスクと、所望のパターンの開口部に拡散されるエッチング種の量を制御するための第2のマスクとを用いて、深さが場所によって変化する前記所望のパターンを半導体表面に作製するための方法において、エッチングに寄与するエッチング種の供給に前記深さの変化に対応した分布を設ける。

【解決手段】第1のパターン1410を有する第1のマスク1402の上層に、第2のパターンを有する第2のマスク1411を積層する積層マスクを基板1401上に形成し、前記第2のマスク1411は、側壁に傾斜を有する開口部1411Bと、平坦部1411Aと、からなり、かつ、上面視で幅広部1415Aおよび1415Bを有するパターンとする。

(もっと読む)

半導体装置の製造方法

【課題】セルアレイ内部とセルアレイの端部とでパターンを均一に形成できる半導体装置の製造方法を提供すること。

【解決手段】 本発明は、第1の領域と第2の領域とが画定された基板上にエッチング対象層を形成するステップと、該エッチング対象層上に第1の開口を有する第1の感光膜パターンを形成するステップと、該第1の感光膜パターンの表面に遮光膜を形成するステップと、該遮光膜が形成された第1の感光膜パターン上に、前記第1の領域と第2の領域とを同時に露光して複数の第2の開口を有する第2の感光膜パターンを形成するステップと、前記第1の感光膜パターンと第2の感光膜パターンとをエッチングバリアとして、前記エッチング対象層をエッチングして複数のパターンを形成するステップとを含むことを特徴とする。

(もっと読む)

半導体表面におけるパターンの作製方法

【課題】所望のパターンを有する第1のマスクと所望のパターンの開口部に拡散されるエッチング種の量を制御するための第2のマスクとを用いて、深さが変化する所望のパターンを半導体表面に作製するための方法において、エッチングに寄与するエッチング種を増大させること。

【解決手段】エッチングガスに塩素を用いてRIBEを行うと、図17(b)の構造が得られる。このエッチングにおいて、マスク厚の厚いSiNxマスク1411からの塩素プラズマの寄与が大きく、マスク厚の薄いSiO2マスク1410からの塩素プラズマの寄与は小さい。したがって、マスク幅の広い回折格子中央部ではマスク上で反応しない塩素プラズマが多量に開口部に拡散することにより開口部での塩素プラズマは高濃度になりエッチング速度が増加する。ここで用いるマスクは2段構造を有しており、1段構造に比べてより多くのエッチング種をエッチングに関与させる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線絶縁膜としてSiOCH膜を用いる場合に、ビアホールの開口径に依らず、その加工制御性を十分に得て、下層Cu配線の表面の組成のバラツキを十分に抑制する。

【解決手段】下層Cu配線3上に形成されている積層構造20は、シリコンと炭素を含有するキャップ絶縁膜4と、キャップ絶縁膜4上に形成されている配線絶縁膜5としてのSiOCH膜を有する。積層構造20にビアホール8、9を形成する工程は、第1及び第2ドライエッチングを組み合わせて行う。第1ドライエッチングでは開口径が小さいビアホール9のエッチングレートが、開口径が大きいビアホール8のエッチングレートよりも大きくなるようにO2濃度が設定された第1混合ガスを用いる。第2ドライエッチングではビアホール8のエッチングレートがビアホール9のエッチングレートよりも大きくなるようにO2濃度が設定された第2混合ガスを用いる。

(もっと読む)

積層構造体及びその製造方法

【課題】生産性が向上し、かつ、半導体膜の導電膜からのはみ出し量が低減できる積層構造体及びその製造方法を提供すること。

【解決手段】本発明にかかる積層構造体は、半導体膜15、ゲート絶縁膜12、ソース電極17、及びドレイン電極18を有するものである。ゲート絶縁膜12は、半導体膜15下において、半導体膜15の端から徐々に膜厚が薄くなるテーパー部を有する。ソース電極17及びドレイン電極18は、半導体膜15上において、半導体膜15のパターンからはみ出さないように形成され、半導体膜15端からの距離が0以上0.3um以下である。

(もっと読む)

半導体装置の製造方法

【課題】パッド領域上での堆積物の生成を抑制することのできる、半導体装置の製造方法を提供する。

【解決手段】パッド領域を有する配線層群を形成するステップと、前記配線層群が被覆されるように、絶縁性のカバー層を形成するステップと、前記パッド領域が露出するように、前記カバー層をプラズマエッチングにより除去するステップとを具備し、前記パッド領域は、アルミニウムにより形成され、前記プラズマエッチングにより除去するステップは、炭素ラジカル及びフッ素ラジカルを発生させるCF系ガスを用いて、前記パッド領域を露出させるステップと、前記露出させるステップの後に、塩素ラジカル又は塩素イオンを発生させるCl2系ガスを用いて、前記パッド領域の表面に生成した堆積物を除去するステップとを備える。

(もっと読む)

シリコン構造体の製造方法及びその製造装置並びにその製造プログラム

【課題】エッチングストップ層を有するシリコンの異方性ドライエッチングにおいて、高い垂直性とともに、良好な側壁形状を達成する。

【解決手段】本発明のシリコン構造体の製造方法は、いわゆるガススイッチングによるドライエッチングの過程で、高速エッチング条件を用いてエッチングする工程(a)により、そのシリコン領域のうち最もエッチング速度の速い場所が前記エッチングストップ層までエッチングされる前に、高速エッチング条件のエッチング速度から時間の経過とともにエッチング速度が低下する遷移エッチング条件を用いたエッチング工程(b)を経て、遷移エッチング条件のうち最もエッチング速度の遅い条件のエッチング速度を持つ低速エッチング条件を用いて前記シリコン領域をエッチングする工程(c)を備えている。

(もっと読む)

半導体装置の製造方法

【課題】膜パターンが倒れないように半導体装置を製造する方法を提供する。

【解決手段】半導体装置の製造方法は、基板上にSiO2膜の膜パターンを形成する工程と、SiO2膜の膜パターンを両側面から挟むように複数のSi膜の膜パターンを形成する工程と、SiO2膜の膜パターンの上面と、複数のSi膜の膜パターンの上面と露出した側面とを被覆するようにレジスト膜を形成する工程と、SiO2膜の膜パターンの上面が露出するまでレジスト膜の一部を除去する工程と、レジスト膜が除去された後に、露出したSiO2膜の膜パターンをウェット処理により除去する工程と、SiO2膜の膜パターンが除去された後に、レジスト膜の残部をドライ処理により除去する工程と、を備える。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】半導体素子の微細パターン形成方法を提供する。

【解決手段】被エッチング膜を備える基板上のセルブロック340内に第1方向に延びる第1部分542と、第1部分542と一体に形成されて第1方向とは異なる第2方向に延びる第2部分544と、をそれぞれ備える複数のモールドマスクパターン540を相互平行に配列されるように形成して、モールドマスクパターンブロック540Aを形成するステップと、基板上に複数のモールドマスクパターン540それぞれの両側壁及び上面を覆う第1マスク層を形成するステップと、第1マスク層のうち相互隣接する2個のモールドマスクパターン540間で、モールドマスクパターン540の側壁を覆っている第1マスク層の第1領域は残り、第1マスク層を一部除去して第1マスクパターンを形成するステップと、を含む半導体素子の微細パターン形成方法。

(もっと読む)

半導体装置及びその製造方法

【課題】高精度なドライエッチングを行うことができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、開口幅が小さい密集した複数の開口からなる密集パターンと、開口幅が前記密集パターンの前記開口幅よりも大きい開口からなる幅広パターンとを有し、前記幅広パターンの開口側の角度が180度未満の角近傍に切欠部を設けたレジスト膜を、エッチング対象上に形成する工程と、前記レジスト膜をマスクとして用いて前記エッチング対象に対しドライエッチングを行い、前記レジスト膜の前記密集パターン及び前記幅広パターンを転写する工程とを含む。

(もっと読む)

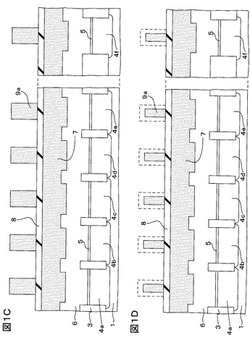

半導体装置の製造方法

【課題】側壁転写技術を用いてライン及びスペースの各幅寸法を微細化した場合に、良好なラインパターンを形成する。

【解決手段】本発明の半導体装置の製造方法は、被加工材4上に犠牲膜5を形成する工程と、犠牲膜5上にライン幅とスペース幅の比率が1対1のラインアンドスペースパターンにパターニングされたレジスト膜6を形成する工程と、レジスト膜6をスリミングしてライン幅寸法をスペース幅寸法の1/3にする工程と、レジスト膜6をマスクにして犠牲膜5を加工した後、レジスト膜6を除去する工程と、犠牲膜5のラインアンドスペースパターンのラインの側壁部に側壁膜9を形成する工程と、犠牲膜5を除去した後、側壁膜9のラインパターンを囲むように枠状の保護パターンを形成する工程と、ラインパターンおよび保護パターンをマスクに、被加工材4を加工する工程とを備えてなる。

(もっと読む)

1 - 20 / 59

[ Back to top ]