Fターム[5F032CA07]の内容

素子分離 (28,488) | 関連技術 (4,816) | 素子領域の材質(単結晶シリコンは不要) (353) | 多結晶シリコン・非晶質シリコン (36)

Fターム[5F032CA07]に分類される特許

1 - 20 / 36

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

液晶表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】島状半導体層を形成するためのフォトリソグラフィ工程及びエッチング工程を省略し、ゲート電極(同一層で形成される配線等を含む)を形成する工程、ソース電極及びドレイン電極(同一層で形成される配線等含む)を形成する工程、コンタクトホールを形成する(コンタクトホール以外の絶縁層等の除去を含む)工程、画素電極(同一層で形成される配線等を含む)を形成する工程の4つのフォトリソグラフィ工程で液晶表示装置を作製する。コンタクトホールを形成する工程において、半導体層が除去された溝部を形成することで、寄生チャネルの形成を防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】加熱による不具合の発生を回避した半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置1の製造方法は、表面に酸化膜、ゲートパターンおよび不純物イオン注入部を有し所定の深さに水素イオン注入部41が形成されているSi基板を用いてSi薄膜トランジスタを形成しており、水素イオン注入部41にマイクロ波M1を照射して水素イオン注入部41を熱処理する照射工程と、照射工程の後、水素イオン注入部41においてSi基板を劈開剥離して、酸化膜、ゲートパターンおよび不純物イオン注入部を有するSi薄膜を分離する剥離工程と、Si薄膜を絶縁基板上に接合する接合工程とを含む。

(もっと読む)

半導体装置

【課題】コンタクト抵抗が低い半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の半導体基板と、埋め込み酸化膜と、第2導電型の半導体層と、を備えるSOI基板に作られ、前記埋め込み酸化膜は、自己に穿設された、前記半導体基板と前記半導体層とを連通する、第1の開口を有し、前記半導体基板は、その表面部分に埋め込み状態に形成され、前記第1の開口内の前記半導体層の埋設部と互いに電気的に接続している、第2導電型の接続層を有し、前記半導体層及び前記埋め込み酸化膜を貫通して、前記接続層の表面部分に至る第2の開口内に埋め込まれて、側面において前記半導体層と電気的に接続し、底面において前記接続層と電気的に接続する、コンタクト電極と、を備える。

(もっと読む)

SOIウエハの製造方法

【課題】半導体基板上に開口部と段差を有する絶縁膜上に、エピタキシャル成長により半導体膜を形成した後研磨することにより、高精度に膜厚を制御された薄膜のSOI層を形成する際にも、SOI層中に残留結晶欠陥が少なく結晶品質の高いSOIウエハの製造方法を提供すること。

【解決手段】半導体基板1に、段差のついた第一第二絶縁膜2、3を形成し、該絶縁膜2、3の第二開口部5bにエピタキシャル層5a成長させ、該エピタキシャル層5aが前記第二開口部5aから横方向に延び、前記第二絶縁膜3を覆うように成長させた際のエピタキシャル膜厚を3μm以下に制御し、続いて、CMP研磨により前記第一絶縁膜2をストッパとして該エピタキシャル層5aを研磨し、前記第一第二絶縁膜2、3の段差の厚みとちょうど同じ厚さに制御されたSOI層を有するSOIウエハとする。

(もっと読む)

半導体装置の作製方法

【課題】可撓性基板上に信頼性の高い半導体装置を歩留まりよく作製する。

【解決手段】耐熱性を有する基板上にTFTを形成される構造にて、前記耐熱性を有する基板とTFTとの間に剥離層を形成する。さらに所望する半導体装置が形成される隙間(平面上で半導体装置と、半導体装置と、の間の領域)の、剥離層の膜厚を変える、すなわち剥離層に段差を設ける加工工程を有する。その後、可撓性基板に素子を転置する。この構造により、例え前記転置する工程にてクラックが入るのを避けられない状態でも、前記半導体装置が形成される間の段差に選択的にクラックが入りやすくすることにより、所望の素子自体へのダメージを避け、歩留まりを高くすることができる。

(もっと読む)

半導体装置と多結晶半導体領域の形成方法

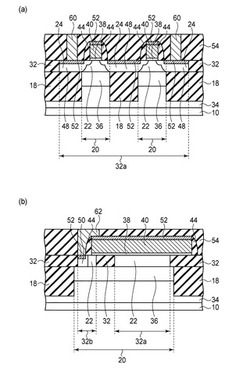

【課題】 ベース層と埋込絶縁層と活性層が順に積層されている積層基板を利用して形成されている半導体装置において、活性層を厚膜化することなく埋込絶縁層と活性層の境界に多結晶半導体領域を形成することができる技術を提供する。

【解決手段】 埋込絶縁層30と活性層20の境界32の一部に、空隙を形成する空隙形成工程と、活性層20の表面20aから活性層20の深さ方向にトレンチを形成するトレンチ形成工程と、トレンチ形成工程で形成されたトレンチを介して空隙形成工程で形成された空隙にポリシリコン(多結晶半導体)を充填する工程を備えている。空隙形成工程とトレンチ形成工程は、空隙とトレンチが連通することを条件として、実施する前後関係が制約されない。

(もっと読む)

半導体装置及び電子機器

【課題】耐熱性の低い基板をベース基板とするSOI基板を用いて高性能な半導体装置を提供することを課題とする。また、機械的な研磨を行わずに高性能な半導体装置を提供することを課題とする。また、該半導体装置を用いた電子機器を提供することを課題とする。

【解決手段】絶縁基板上の絶縁層と、絶縁層上の接合層と、接合層上の単結晶半導体層と有し、単結晶半導体層は、その上部表面における凹凸形状の算術平均粗さが1nm以上7nm以下とする。または、凹凸形状の二乗平均平方根粗さが1nm以上10nm以下であっても良い。または、凹凸形状の最大高低差が5nm以上250nm以下であっても良い。

(もっと読む)

半導体装置の製造方法

【課題】 イオン注入時における素子形成領域と素子分離領域とのレジスト寸法差を所望の値以下とすることができ、デバイス特性の改善に寄与する。

【解決手段】 半導体基板101の素子形成領域102を囲むように素子分離溝を形成する工程と、この溝内に絶縁膜104を埋め込んだ後に平坦化することで素子分離領域103を形成する工程と、素子形成領域102にゲート絶縁膜111、ゲート電極112、ソース/ドレイン領域114,115を形成することでトランジスタを作製する工程と、素子形成領域102と素子分離領域103に跨るように、イオン注入のマスクとなるレジスト121のパターンを形成する工程とを含む半導体装置の製造方法であって、絶縁膜104の厚さを、所望耐圧を満たす膜厚以上に設定し、且つ絶縁膜104上のレジスト寸法と素子形成領域102上のレジスト寸法との差が極小値となる膜厚近傍に設定する。

(もっと読む)

半導体装置の作製方法

【課題】生産コストを削減することができる半導体装置の作製方法の提案を課題とする。

【解決手段】ボンド基板の下に容器を配置した後、ボンド基板を劈開させることでボンド基板から形成される複数の第1の半導体膜を、容器に載置し、複数の第1の半導体膜を容器から拾い上げて、複数の第1の半導体膜どうしが離隔するようにベース基板に貼り、複数の第1の半導体膜をエッチングすることで、複数の第2の半導体膜を形成する半導体装置の作製方法。

(もっと読む)

半導体装置の作製方法及び製造装置

【課題】生産コストを削減することができる半導体装置の作製方法、及び該作製方法を用いる製造装置の提案を課題とする。

【解決手段】ボンド基板(半導体基板)をベース基板(支持基板)に貼り合わせた後に、該ボンド基板を劈開させて半導体膜を形成するのではなく、先にボンド基板を複数箇所において劈開することで複数の第1の半導体膜(マザーアイランド)を形成してから、該複数の第1の半導体膜をベース基板に貼り合わせる。そして、上記複数の第1の半導体膜をそれぞれ部分的にエッチングすることで、1つの第1の半導体膜から単数または複数の第2の半導体膜(アイランド)を形成し、該第2の半導体膜を用いて半導体素子を作製する。複数の第1の半導体膜は、半導体素子が有する第2の半導体膜がレイアウトされるべき領域を少なくともカバーするように、上記レイアウトに合わせてベース基板に貼り合わせる。

(もっと読む)

薄膜トランジスタ、表示素子およびそれらの製造方法

【課題】ゲート絶縁膜を薄膜化可能としつつパターン精度を高めた薄膜トランジスタを提供する。

【解決手段】半導体層31を覆って基板21上に形成したゲート絶縁膜32に、半導体層31上に位置する第1領域41と、半導体層31の外方に位置し基板21からの距離が第1領域41より大きい第2領域42とを連続して設ける。半導体層31の端面近傍での電界集中を緩和し、ゲート絶縁膜32を薄膜化可能としつつパターン精度を高めることができる。

(もっと読む)

半導体装置

【課題】半導体装置の耐電圧を高めることにより、信頼性の高い半導体装置を提供する。

【解決手段】

シリコン層上に誘電体分離膜122、132を閉ループ状に形成することによりシリコン層上の第一の半導体層領域123、133を絶縁分離し、その内側に拡散抵抗124、134を形成する。第一の誘電体分離膜122、132の閉ループの外側には第二の半導体層領域143が形成されている。この第二の半導体層領域143は、第二の誘電体分離膜142により閉ループ状に囲まれて、配線151の電位を与えられている。サージ電圧が印加されたとしても、第二の半導体層143は二つの拡散抵抗124、134の中点電位に固定されているため、第一の半導体層123、133と第二の半導体層143との間の電位差が半減し、誘電体分離膜122、132の破壊を防ぐことができる。

(もっと読む)

半導体装置の作製方法

【課題】高性能で安価な半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上に、単結晶半導体基板にイオンを打ち込み前記基板に貼り付けた後熱処理を加えることにより残存させた単結晶半導体層を有する第1の領域と、非単結晶半導体層を有する第2の領域と、を設ける。また、劈開単結晶半導体層に不活性雰囲気中においてレーザー光の照射を行い、非単結晶半導体層には、少なくとも一度、大気雰囲気中においてレーザー光の照射を行うとより好ましい。

(もっと読む)

マイクロ電子デバイス構造体およびその形成方法(ガード・リングまたはコンタクトをSOI基板に形成する方法)

【課題】セミコンダクタ・オン・インシュレータ(SOI)基板(120)のバルク半導体領域(116)とコンタクトする導電素子(110、310、410a、410b、510)を形成する方法が提供される。

【解決手段】第1の開口部(228)は、トレンチ分離領域(124)の上を覆う共形層(126)に形成される。トレンチ分離領域(124)は、基板(120)のSOI層(108)と端部を共有してもよい。誘電体層(114)は、共形層(126)およびトレンチ分離領域(124)の上面を覆って付着されるのが望ましい。次に、誘電体層(114)および共形層(126)の第1の開口部(228)を通って延びる第2の開口部(416)を形成することができる。バルク半導体領域(116)の一部および共形層の上面(128、328、414a、414b、514)は、第2の開口部(416)内に露出されるのが望ましい。その後、第2の開口部(416)は、金属または半導体のうちの少なくとも1つで充填されて、バルク半導体領域(116)および共形層(126)の上面(128、328、414a、414b、514)の露出部分とコンタクトする導電素子(110、310、410a、410b、510)を形成することができる。

(もっと読む)

SOI基板の製造方法

【課題】貼り合わせ不良を防止できるSOI基板の製造方法を提供する。

【解決手段】半導体基板の所定の深さの領域に脆化層を形成し、半導体基板上に絶縁層を形成し、半導体基板の外縁を脆化層よりも深い領域まで絶縁層側から選択的にエッチングし、半導体基板と、絶縁表面を有する基板と、を、絶縁層を挟んで重ね合わせて接合する。半導体基板を加熱して、絶縁表面を有する基板上に半導体層を残して、半導体基板を脆化層で分離する。

(もっと読む)

半導体装置及びその作製方法

【課題】セルフヒーティングによる誤動作を低減し、より安定した動作を確保することができる信頼性の高い半導体装置を提供する。

【解決手段】半導体素子が有する半導体膜と基板の間に、冷媒を流すための空洞を有する。該空洞は、凹部を有する絶縁膜を半導体膜と基板の間に設けることで形成される。そして該絶縁膜は、空洞内へ冷媒を導入するための開口部と、空洞内から冷媒を排出するための開口部とを少なくとも有する。一方の開口部から導入された冷媒は、空洞内を流れ、他方の開口部から排出される。

(もっと読む)

半導体装置及びその作製方法

【課題】より単純なプロセスで、従来よりも接合容量を低減し、低消費電力化を実現することが出来る半導体装置及びその作製方法を提供する。

【解決手段】ベース基板と、ベース基板上に形成された半導体膜と、半導体膜上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された電極とを有し、半導体膜は、ゲート絶縁膜を間に挟んで電極と重なるチャネル形成領域を有し、半導体膜が有する凹部とベース基板の間に空洞が形成されており、チャネル形成領域は、凹部において空洞に接している。

(もっと読む)

半導体装置及びその作製方法

【課題】応答速度が高く、かつ、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】基板上に、接合層と、前記接合層上に、絶縁膜と、前記絶縁膜上に、単結晶半導体層と、前記単結晶半導体層中に、チャネル形成領域と、低濃度不純物領域と、シリサイド領域と、前記絶縁膜とシリサイド領域の間に、希ガス元素を含む非単結晶半導体膜と、前記単結晶半導体層上に、ゲート絶縁膜と、ゲート電極と、前記ゲート電極の側面に、サイドウォールとを有し、前記非単結晶半導体膜により、前記シリサイド領域中の金属元素が前記チャネル形成領域に拡散するのが抑制される半導体装置及びその作製方法に関する。

(もっと読む)

SOI基板及びその作製方法、並びに半導体装置

【課題】ガラス基板など耐熱温度が低い基板を用いた場合にも、実用に耐えうるSOI層を備えたSOI基板を提供する。また、そのようなSOI基板を用いた半導体装置を提供する。

【解決手段】絶縁表面を有する基板若しくは絶縁基板に、単結晶半導体層を接合するに際し、接合を形成する面の一方若しくは双方に、有機シランを原材料として成膜した酸化シリコン膜を用いる。本構成によれば、ガラス基板等の耐熱温度が700℃以下の基板を用い、強固に接合したSOI層を得ることができる。すなわち、一辺が1メートルを超える大面積基板上に単結晶半導体層を形成することができる。

(もっと読む)

1 - 20 / 36

[ Back to top ]