Fターム[5F033LL04]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 不純物、イオンを含むもの (1,142) | As、B、P系 (585)

Fターム[5F033LL04]に分類される特許

581 - 585 / 585

無定形炭素層を含むマスキング構造

多数層を有するマスキング構造が形成される。そのマスキング構造は、無定形炭素層と該無定形炭素層上に形成されたキャップ層とを含む。無定形炭素層は透明無定形炭素を含む。キャップ層は非酸化物材料を含む。マスキング構造は、半導体装置の製作中、エッチング・プロセスにおけるマスクとして使用可能である。 (もっと読む)

半導体装置

【課題】ESD 保護回路のサージ電流経路に使用される配線層に生じる熱を効率よく放熱でき、サージ電流経路に使用される配線層も保護する。

【解決手段】外部端子と内部回路との間の配線に接続され、外部端子に印加された過大な静電サージ入力から内部回路を保護する保護素子を有する入力保護回路と、入力保護回路に接続され、そのサージ電流経路に含まれる第1のメタル配線層25と、第1のメタル配線層に連なり、熱伝導性が良好な材質の配線を用いてなる放熱器20とを具備する。

(もっと読む)

配線構造

【課題】 高い周波数が印加され、数cm〜数10cmの長さを有する配線の抵抗を低減し、伝送される信号波形のなまりを低減する。

【解決手段】 高周波が印加される配線111は、層間絶縁膜107を介して、配線111の線方向にそって複数設けられたコンタクトホールにより配線106と電気的に並列接続している配線構造を採用する。その配線構造を周辺回路一体型アクティブマトリクス型液晶表示装置の周辺回路に用いることで、高周波信号が印加される配線において信号波形のなまりを低減できる。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

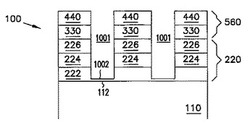

導電線間に空隙を有する導電線構造体の製造方法

【課題】半導体回路の隣接導体線間容量性クロストークを減少させる。

【解決手段】フィラー材料を蒸発させて形成された空隙を有する金属被覆体の製造方法で、フィラー材料30は透過性の誘電層40により覆われる。フィラー材料はPPG、PB、PEG、非結晶フッ化炭素及びPCLからなる群から選択され、スピン・オン法又はCVD法により形成される。フィラー材料を、間隔をあけた導電線20及び半導体構造体10上に形成し、エッチバック処理し、導電線の上面を露出させる。次に、フィラー材料上に透過性の誘電層40を形成する。透過性の誘電層は分解したガス相フィラー材料が拡散するのを許容する性質がある。フィラー材料を蒸発させ、気相フィラー材料に変化させる。気相のフィラー材料は透過性の誘電層を通じて拡散して、間隔をあけた導電線の間に空隙を形成する。透過性の誘電層上に絶縁層が形成される。

(もっと読む)

581 - 585 / 585

[ Back to top ]