Fターム[5F033LL07]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 結晶性 (266) | 結晶面 (49)

Fターム[5F033LL07]に分類される特許

41 - 49 / 49

半導体装置及びその製造方法

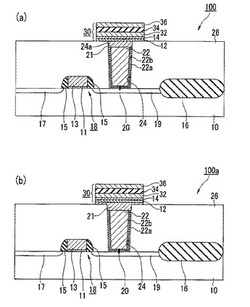

【課題】キャパシタ等のデバイスを構成する各層の結晶配向に優れた半導体装置を提供する。

【解決手段】本発明の半導体装置は、基板10上の層間絶縁膜26に形成された貫通孔24内に設けられてなるプラグ20を介した導電接続構造を具備した半導体装置であり、前記プラグ20が前記貫通孔24内に第1導電膜を埋め込んでなるプラグ導電層22を有しており、少なくとも前記プラグ導電層22上には、シリコンからなる第2導電膜21と、自己配向性を有する導電材料からなる窒化チタン層12とが積層されている。

(もっと読む)

アモルファス膜の成膜方法、このアモルファス膜を備える半導体装置、及び半導体装置の製造方法

【課題】Ti及びAlを含有するほかに、Nを任意成分として含むことがあるアモルファス膜を成膜する方法を提供する。

【解決手段】 Ti及びAlを含むほかに任意成分としてNを含むことがあるアモルファス膜であって、電気抵抗率が、6×102Ω・cm以下の当該アモルファス膜を、スパッタリングターゲットとしてTiAl合金を用い、下記のスパッタ条件で基板上に成膜する。(1)DCパワーは、1kW以上かつ3kW以下である、(2)成膜室内の気圧は、6mTorr以上かつ12mTorr以下である、(3)基板温度は、100℃以上かつ300℃以下である、及び(4)N2ガスとArガスとの混合スパッタガス中におけるN2ガスの体積比率が0%以上かつ70%以下である。

(もっと読む)

金属系膜形成方法及びプログラムを記録した記録媒体

【課題】 結晶構造をコントロールすることによって,従来以上に低い抵抗を有する金属系膜を形成する。

【解決手段】 金属系原料ガスとして例えばWF6ガスを供給するステップと水素化合物ガスとして例えばSiH4ガスを供給するステップとを,不活性ガス例えばArガス,N2ガスを供給するパージステップを介在させて,交互に繰り返し実行することによって,非晶質を含む第1タングステン膜を成膜する第1タングステン膜成膜ステップと,第1タングステン膜上に,上記WF6ガスと還元性ガスとして例えばH2ガスを同時に供給することによって,第2タングステン膜を成膜する第2タングステン膜成膜ステップとを含む。SiH4ガスを供給するステップ後のパージステップの実行時間を変えることにより第1タングステン膜が含む非晶質の割合をコントロールする。

(もっと読む)

基板処理方法、成膜方法、成膜装置およびコンピュータプログラム

【課題】 Cu膜の成膜速度を向上させるための基板処理方法およびこの基板処理方法を用いたCu膜の成膜方法を提供する。

【解決手段】 例えば、表面にRu膜が形成されたウエハWを加熱処理して、Ru膜の表面に、Cuとの格子不整合が小さい配向性を有する(001)面または(002)面を優先配向させる(STEP3)。次に、例えば、熱CVD法等によりRu膜上にCu膜を成膜する(STEP4)。このSTEP4では、Ru膜の表面の結晶性に依存して、Cu膜の成膜速度を大きくすることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 幅の異なる銅配線上に金属キャップ層を形成する際に、幅の広い銅配線の表面を十分覆うために、金属キャップ層を形成にかける時間を長くすると、幅の細い銅配線上に形成される金属キャップ層が、配線の幅からはみ出し、ショートを引き起こす。

【解決手段】 幅の狭い銅配線の表面に金属キャップ層を形成するための時間を、幅の広い銅配線の表面に形成するための時間よりも短くする。この特徴により、幅の広い銅配線表面を十分に金属キャップで覆うことができ、幅の細い配線上に形成された金属キャップ層によるショートの発生を防止できる。

(もっと読む)

銅配線層の形成方法、半導体装置の製造方法

【課題】 細りのない所望する断面積の銅配線を形成することができる銅配線層の形成方法および半導体装置の製造方法を提供すること。

【解決手段】 基板1上に下地絶縁膜2、下地バリア層3、銅シード層4を順次成膜したのち、この銅シード層4上にフォトレジスト層5の配線溝6パターンを形成し、この配線溝6の底部に露出した銅シード層4上に銅配線層7を形成し(図2(a))、この層7上に保護層8を形成したのちこの層8をマスクとしてフォトレジスト層5、銅シード層4、下地バリア層3を順次エッチングして図2(e)に示す銅配線層7のパターンを形成する。

この層7からの銅の拡散を防止するため表面に層間絶縁層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 ボイドの移動経路となるバウンダリーが顕著に低減されるため、SIV不良の発生を効果的に抑制することができ、信頼性の高い半導体装置を提供する。

【解決手段】 相対的に広幅の第2銅配線110,126の上面において、銅のグレインが数10μm程度と非常に大きい。第2銅配線110,126の配線幅は0.3μm〜数10μm程度であるので、第2銅配線110,126の上面において配線幅方向のバウンダリーが顕著に低減され、第2銅配線110,126とビア113との接続部分にボイドが集中・合一して大きなボイドが形成されることを抑制することができ、SIVの発生が効果的に抑制される。相対的に狭幅の第1銅配線111,127の面方位はEM耐性を向上させるために主にCu(111)であり、相対的に広幅の第2銅配線110,126の面方位はSIV耐性を向上させるために主にCu(200)である。

(もっと読む)

半導体内部配線

【課題】Si基板上に成膜配線して半導体素子を形成することにより銅の利点である耐EM性や耐SM性を十分に生かして高度耐腐食性の微細化配線を持つ半導体素子を製造することができる高純度単結晶銅とその製造方法、更に得られた単結晶銅からなるスパッタリングターゲットおよび同ターゲットを用いて成膜した配線を有する半導体素子を提供すること。

【解決手段】銀と硫黄の合計含有量が0.1ppm以下である純度99.9999wt%以上の高純度銅を出発原料として用い、これを電気炉1内に配置した原料るつぼ5内に入れて溶解し、るつぼ底部の溶解滴下孔4から下方の単結晶鋳型6に溶解銅を滴下する。この間上部、中部、下部ヒーター10、11、12により温度を調節し、石英外筒3内を真空排気装置2により排気する。炉底部には断熱トラップ8がありその外側に冷却水9が貫流する水冷フランジ7が配置されている。この装置の単結晶鋳型内に半導体素子の配線形成用ターゲット材として好適な高純度単結晶銅が得られる。

(もっと読む)

配線層の形成方法、配線層および薄膜トランジスタ

【課題】 配線膜厚が200〜1000nm程度のサブμmオーダの薄膜でも2.5μΩcm以下の比抵抗を得ること配線層の形成方法および配線層を提供すること。

【解決手段】 ガラス基板1上に下地絶縁膜2の窒化シリコン膜を形成し、この上に下地金属層3を形成し、この上に金属シード層4を形成し、この金属シード層4上に金属配線層7を形成した配線層であって、上記金属シード層4は主として結晶面が(111)に配向し、平均結晶粒径が0.25μm以上であり、上記金属配線層は膜厚が200乃至1000nmであり、無電解めっき法で形成された層である。

(もっと読む)

41 - 49 / 49

[ Back to top ]