Fターム[5F033QQ44]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | リフトオフ (276) | リフトオフ材 (96) | エッチングマスクと兼用 (16)

Fターム[5F033QQ44]に分類される特許

1 - 16 / 16

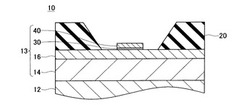

半導体装置の製造方法と半導体装置

【課題】半導体基板の表面のAl層の表面が荒れることを抑制しつつ、リフトオフの後に溶解層が剥離せずに残ることを防止し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板12の表面にAl層14を形成し、Al層14の表面にTiN層16を形成し、TiN層16の表面の一部に絶縁層20を形成し、TiN層16と絶縁層20の表面に溶解層を形成し、溶解層の表面にレジスト層を形成し、溶解層とレジスト層の一部を除去して溶解層開口部を形成してTiN層16の一部を露出させ、レジスト層の表面、及び、露出したTiN層16の一部の表面にTi層30及びNi層40を形成し、アルカリ溶液によって溶解層を溶解させることにより、溶解層とともに、レジスト層とその表面に形成されたTi層及びNi層を除去する。

(もっと読む)

半導体装置の製造方法及びハードマスクの形成方法

【課題】アモルファスカーボン膜のパターン寸法ばらつきが低減した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にアモルファスカーボン膜を成膜する工程と、アモルファスカーボン膜のパターンを形成する工程と、アモルファスカーボン膜をマスクにして下地膜をエッチングする工程を有する。アモルファスカーボン膜は、アモルファスカーボン膜の表面から下地膜に接する面に向かってその厚み方向を進むにつれて、アモルファスカーボン膜の膜密度を小さくする。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数を削減し、電気抵抗値のバラツキを低減して歩留まりを向上させる。

【解決手段】まず、半導体基板1の平面1aに、開口部を有するマスク層を形成し、次いで、半導体基板1に、マスク層の開口部から電極パッド層4に達するビアホール6を形成した後、マスク層を除去する。次に、金属層形成工程において、半導体基板1に形成したビアホール6の底部6aとなる電極パッド層4上に、電極パッド層4よりも絶縁材料の密着性が低い金属層8を形成する。次に、絶縁層形成工程において、化学気相成長法にて金属層8を除く部分、即ちビアホール6の側壁部6bに絶縁材料からなる絶縁層9を形成する。そして、導電膜形成工程において、半導体基板1の平面1a及びビアホール6の内部に導電層12を形成する。

(もっと読む)

パターン形成方法、及び半導体装置の製造方法

【課題】下地の性能を犠牲にすることなく、リフトオフ層が下地から剥離することを防止できるパターン形成方法、及び半導体装置の製造方法を提供すること。

【解決手段】本発明にかかるパターン形成方法は、基板上にカバー絶縁膜22を形成し、第1のレジストパターン104をマスクとして、金属膜パターン形成領域を取り囲むようカバー絶縁膜22に凹部103を形成する工程と、凹部103内に入り込むよう、カバー絶縁膜22上にリフトオフ層となる第2のレジストパターン25を形成する工程と、第2のレジストパターン25をマスクとして、金属膜パターン形成領域のカバー絶縁膜22に開口部を形成する工程と、第2のレジストパターン25の上から基板表面に金属膜を成膜し、第2のレジストパターン25とともに第2のレジストパターン25上の金属膜を除去して金属膜パターンを形成する工程とを備えるものである。

(もっと読む)

配線構造体の製造方法及び配線構造体

【課題】 横方向(基板表面に平行な方向)にカーボンナノチューブを成長させるためには、側壁に平坦かつ微小な表面を持つ触媒膜を形成する必要がある。ところが、このような触媒膜を形成することは困難である。

【解決手段】 基板表面の相互に離隔した2つの縦配線領域に、第1の厚さの縦配線用触媒膜を形成し、1つの縦配線領域から他の縦配線領域まで連続する横配線領域に、第1の厚さよりも厚い第2の厚さの横配線用触媒膜を形成する。縦配線用触媒膜及び横配線用触媒膜の上に、カーボンを含む構造体を気相成長させる。気相成長の初期段階には、縦配線用触媒膜及び横配線用触媒膜の上にグラファイトが形成され、その後、縦配線領域の前記グラファイトと基板との間にカーボンナノチューブが成長し、横配線領域の前記グラファイトが、縦配線領域に成長したカーボンナノチューブによって中空に支持されるように第1の厚さ及び第2の厚さが設定されている。

(もっと読む)

構造体、パターニング方法および接合方法

【課題】一部の領域を加圧することにより、加圧した領域と加圧していない領域との間に材料特性の差異を生じさせることが可能な機能性の高い多孔質膜を有する構造体、前記多孔質膜を簡単にパターニングすることができるパターニング方法、および、加圧した領域の前記多孔質膜を導電性の接合膜として、基材と被着体とを効率よく接合可能な接合方法を提供すること。

【解決手段】構造体1は、基材20と、この上に設けられ、複数の金属粒子101、102が複数の空孔105を囲うように配列した多孔質膜13とを有し、この多孔質膜13は、各金属粒子101、102と複数の樹脂粒子とを含む液状材料を基材20上に供給し、各金属粒子を自己組織化させた後、前記各樹脂粒子を除去することにより、被膜中に空孔105を形成して作製されたものである。この多孔質膜13は、一部の領域を加圧すると、加圧領域と非加圧領域とで材料特性の差異を発現するものである。

(もっと読む)

半導体装置の製造方法

【課題】薄膜トランジスタを印刷法を用いて作製する場合、第1の電極と第2の電極のあわせ精度が問題となる。ホトリソグラフィで作製すれば、各層のホトマスクが必要となりコストが増大する。

【解決手段】本願発明の骨子は、基板上に、ゲートパターン用ホトマスクでの露光により形成されたレジストパタンを用いてゲート形状の加工のみならず、ソース・ドレイン電極の加工を、リフトオフを用いて行う。こうして、ソース・ドレイン電極とゲート電極の位置合わせが施される。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】配線を形成したときに電極と配線との密着性を向上できる炭化珪素半導体装置の製造方法を提供する。

【解決手段】炭化珪素半導体装置100aの製造方法は、以下の工程を備えている。まず、炭化珪素半導体層110が準備される。そして、炭化珪素半導体層110の表面に、金属層が形成される。そして、金属層を熱処理することにより電極150が形成される。そして、電極150の表面の炭素を除去するためのエッチングが行なわれる。金属層を形成する工程では、金属層を熱処理する温度において炭素よりもシリコンとの反応性が高い金属層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】アンダーフィルを用いることなく、半導体装置の高い実装信頼性を提供する。

【解決手段】能動素子10と、能動素子10に形成される電極12と、電極12に接続される導電層15と、導電層15上に形成された絶縁層16とを有し、導電層15の上部が絶縁層16から露出され、導電層15が露出される部分において、導電層15と絶縁層16とに段差が設けられる半導体装置を構成する。

(もっと読む)

パターン形成方法

【課題】本発明の課題は、膜応力の発生により、リフトオフ層としてのレジスト層が下地絶縁膜から剥離し、その露呈部分に不要な金属膜が付着してもショート不良になることを防止できるパターン形成方法を提供する。

【解決手段】本発明のパターン形成方法は、ソース電極20上にPSGからなる下地絶縁膜23を形成し、その上に、金属膜パターン(TiNiAg)と異なるエッチング選択比を有する金属としてのAlからなる第2の金属層102を形成し、その上にリフトオフ層となるレジスト層24を形成し、レジスト層24に所定パターンの開口24aを形成し、これをマスクとして、第2の金属層102および下地絶縁膜23を順次、ウェットエッチングして開口102aおよび開口23aを形成し、その上から金属膜25を被着後、レジスト層を溶解させ、その上の不要な金属膜を除去した後、第2の金属層102をエッチング除去する。

(もっと読む)

金属配線の製造方法

【課題】金属膜の剥離といった問題が生じない高精度な金属配線の製造方法を提供する。

【解決手段】基板1の表面にレジストマスク2を形成し、このレジストマスク2に配線パターンを形成し、レジストマスク2及び基板1の表面の露出部11に金属膜3を形成した後、レジストマスク2を剥離して基板1上に金属膜3のみを残す金属配線の製造方法であって、金属膜3の形成前に、露出部11に凹部12を設けると共に凹部12の底面を粗面化し、金属膜3は0.5μm以上の膜厚を有することを特徴とする金属配線の製造方法。

(もっと読む)

MIMキャパシタを含む半導体集積回路素子およびその製造方法

【課題】キャパシタンス値が所定値以上に高く、VCCが所定値以下に維持されるMIMキャパシタを含む半導体集積回路装置を提供する。

【解決手段】活性領域を含む半導体基板、基板の上面の一部に形成され、絶縁領域を定義する絶縁物、共通のコンダクタ層からパターニングされ基板上に形成され、絶縁物上に形成された第1パターン部と、活性領域上に形成され活性領域内に形成されたトランジスタのゲートを含む第2パターン部を含むコンダクタ層パターン、前記第2パターン部は前記活性領域内に形成されたトランジスタのゲートを含み、コンダクタ層パターンの前記第1パターン部上に形成された下部電極、下部電極上に形成された誘電層パターン、および誘電層パターン上に形成された上部電極を含む絶縁領域内のキャパシタを含む半導体集積回路素子とその製造方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】バイアホールを形成する際のエッチングマスクと、基板との間の付着性を向上させる。

【解決手段】SiC基板にバイアホールを形成する半導体装置の製造方法において、SiC基板2の裏面にTi膜3a、Au膜4aの積層膜を形成し、その上面に、Pd膜6を形成する。次に、Pd膜6を触媒として、無電解メッキ法によりNi膜7(エッチングマスク)を形成する。このように形成することにより、Ni膜7とSiC基板2との間の付着性を向上させることができる。従って、SiC基板2にバイアホールを形成する際のエッチングにおいて、バイアホール8を良好に形成することができる。

(もっと読む)

液晶表示装置及びその製造方法

【課題】工程を単純化することのできる水平電界薄膜トランジスタ基板及びその製造方法を提供すること。

【解決手段】本発明による液晶表示装置は、基板上に形成されたゲートライン102と、ゲートライン102とゲート絶縁膜とを介して交差され画素領域を定義するデータライン104と、ゲート電極とソース電極とドレイン電極112及びソース電極とドレイン電極との間にチャネルを定義する半導体層を含む薄膜トランジスタ(TFT)と、基板上に形成された共通ライン120と、画素領域に形成された共通電極122及び画素領域に共通電極122と水平電界を形成するための画素電極118を含み、データライン104とソース電極及びドレイン電極が不透明導電パターン及び透明導電パターンを備え、画素電極118はドレイン電極の透明導電パターンが伸張され形成され、保護膜が透明導電パターンと境界を成し、透明導電パターンを除いた残りの領域に形成されることを特徴とする。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 薄膜トランジスタ表示板の製造工程を簡素化する。また、画素電極の断線を防止できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】 本発明の一実施形態による薄膜トランジスタ表示板の製造方法は、基板上にゲート線を形成する段階と、前記ゲート線上にゲート絶縁膜を形成する段階と、前記ゲート絶縁膜上に半導体層を形成する段階と、前記半導体層上にオーミック接触部材を形成する段階と、前記オーミック接触部材上にデータ線及びドレイン電極を形成する段階と、前記データ線及び前記ドレイン電極上に保護膜を蒸着する段階と、前記保護膜上に第1感光膜を形成する段階と、前記第1感光膜をマスクとして前記ゲート絶縁膜及び前記保護膜をエッチングすることによって、前記ドレイン電極の少なくとも一部と前記基板の少なくとも一部を露出させる段階と、導電体膜を蒸着する段階と、並びに前記第1感光膜を除去し、前記ドレイン電極の露出した部分上に画素電極を形成する段階とを含む。

(もっと読む)

多層微細配線構造およびその作製方法

【課題】 高速情報処理用デジタル集積回路チップ内およびそのチップを搭載するためのパッケージ、モジュール、ボードなどの実装系内における多層配線の作製方法に関する新しい多層微細配線構造およびその作製方法を提案する。

【解決手段】 高解像感光性ポリイミドを絶縁層として、銅、銀、金、アルミニウム、パラジウム、ニオブなどの金属を配線層として用いて、ストリップライン、マイクロストリップライン、同軸ラインなどの伝送線路構造を有する多層微細配線構造を実現するため、広い周波数帯域について、インピーダンスが一定に制御され、デジタル高速信号伝送に適する線路を実現することができる。高解像特性を有する感光性ポリイミドを絶縁層として用いることにより、絶縁層へのビア穴加工がリソグラフィ工程のみで達成され、また、金属配線層をリフトオフ法によりパターン形成することにより、従来の多層配線技術に比べて、高密度の配線構造が実現でき、大幅に工程が簡略化される。

(もっと読む)

1 - 16 / 16

[ Back to top ]