Fターム[5F033QQ72]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | 熱処理の対象 (3,254)

Fターム[5F033QQ72]の下位に属するFターム

Fターム[5F033QQ72]に分類される特許

21 - 31 / 31

成膜方法及び成膜装置

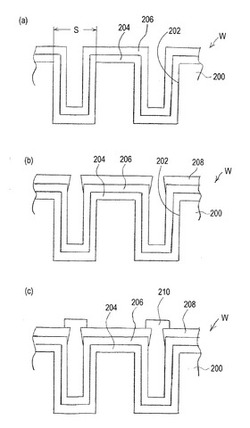

【課題】例えアスペクト比が高く、深さが深いビアホール等の凹部にあっても、銅等の金属材料を、内部にボイドを発生させることなく、凹部内に高速かつ確実に埋込むことができるようにする。

【解決手段】凹部202を有し該凹部202の内部を含む表面に通電層206を形成した基板Wを用意し、凹部202の内部を除く通電層206の表面に電着法で高分子絶縁膜208を形成し、高分子絶縁膜208を形成した基板Wの表面に電解めっきを行って凹部202内に金属材料210を埋込む。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】

本発明は、薄膜トランジスタ表示板及びその製造方法に関し、金属残留物による汚染を減少させて、薄膜トランジスタの特性を確保することを課題とする。

【解決手段】

本発明による薄膜トランジスタ表示板の製造方法は、基板上にゲート線を形成し、前記ゲート線上にゲート絶縁膜、半導体層、及びオーミックコンタクト層を順次形成し、前記オーミックコンタクト層上にデータ層を形成し、前記データ層上に感光膜パターンを形成し、前記データ層をエッチングして、ソース電極を含むデータ線及び前記ソース電極と対向するドレイン電極を形成し、前記ソース電極及び前記ドレイン電極の側面を覆うように前記感光膜パターンをリフローし、前記リフローされた感光膜パターンをマスクにして前記オーミックコンタクト層をエッチングすることを特徴とする。

(もっと読む)

微細加工方法及び微細加工構造並びに電子デバイスの製造方法及び電子デバイス

【課題】プロセス工程の数が従来のリフトオフ方法より少なく、基板との密着性が良好な薄膜パターンの形成が可能な微細加工方法を提供すること。基板との密着性に優れたパターニングされた被加工薄膜を有する微細加工構造を提供すること。移動度が優れた有機トランジスタの作成が可能な微細加工方法及び電子デバイスを提供すること。

【解決手段】基体1上にレジスト膜2を形成する工程、レジスト膜2をパターン露光する工程、現像を行うことなくレジスト膜2上に被加工薄膜4を形成する工程、レジスト膜2の非露光部2bとその上の被加工薄膜4とをリフトオフする工程、を順次行うことを特徴とする。パターン化された被加工薄膜4aと基板1との間に、露光されたレジストパターン2aが介在していることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】多層配線を有する半導体装置において、空孔率の高い配線間構造を用い、配線間の電気的短絡を抑制する。

【解決手段】基板上にそれぞれ同一レベルに備えられた第一および第二の配線層110、310と空孔率60%以上を有する第一および第二の空洞層120、320を有する配線構造において、第一および第二の空洞層120、320と接する配線層の側壁に第一および第二の酸化チタン層160、360からなる絶縁層を備え、配線層と接する側壁に第二および第四のチタン層150a、350aを備え、バリアメタル層と絶縁層の間に酸素バリア層として第一のおよび第二の窒化チタン層150b、350bを備えることにより、隣り合う配線間の電気的耐圧を向上し、配線間短絡を抑制する。

(もっと読む)

半導体装置の製造方法および製造装置

【課題】 バリア層を形成する前にビアホール底部に形成された酸化Cu層を除去する際に、ダメージ等の問題がなく、大口径の基板であっても均一に除去できる半導体装置の製造方法および製造装置を提供する。

【解決手段】 ビアホール底部に形成された酸化Cu層を有機酸洗浄により還元処理する還元処理工程S101と、前記還元処理工程S101後にスパッタリングによりバリア層を形成するバリア層形成工程S106と、前記バリア層形成後にスパッタリングによりCuシード層を形成するCuシード層形成工程S107とを有し、前記還元処理工程S101と前記バリア層形成工程S106と前記Cuシード層形成工程S107とを同一の製造装置内で連続して行う。これにより、低比誘電率材料からなる層間絶縁膜を劣化させることなく、かつ半導体基板面内にわたって均一に、下層配線Cuとバリア層との間に良好なコンタクトを形成することが可能となる。

(もっと読む)

集積回路装置の製造方法

【課題】リソグラフィー技術の限界以上に微細化した配線構造を持つ集積回路装置製造方法の提供。

【解決手段】 線幅30nm以下の配線を作成する方法であって、下地表面上に、配線用材料と親和性を有する最短部の長さが配線の幅の1.5倍以下の複数の領域と、配線用材料と親和性を有しない複数の領域とが交互に表れるパターンを形成し、直径30nm以下の配線用材料をパターンが形成された下地表面に接触させて、配線用材料と親和性を有する複数の領域の間をつなぐ配線を形成することを特徴とする集積回路装置の製造方法。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 エアーギャップ構造を利用したデュアルダマシン構造を有する半導体装置の製造方法を提供する。

【解決手段】 基体上にSi犠牲膜420を堆積し、このSi犠牲膜に下層配線用の溝を形成した後、この配線溝に導電性材料を埋め込み下層配線260とする。この下層配線と前記Si犠牲膜上に多孔質low−k膜280とSi犠牲膜424を順次堆積した後、これらの膜を貫通する開口部と、Si犠牲膜424には上層配線用の溝とを形成し、前記開口部と配線溝に導電性材料を堆積させ上層配線262とする。この後Si犠牲膜420、424をエッチングで除去し、エアーギャップ311,313を形成する。

(もっと読む)

半導体デバイスの製造方法およびこのような方法で得られる半導体デバイス

本発明は、半導体ボディ(1)と基板(2)とを有し、少なくとも1つの半導体素子(3)を備える半導体デバイス(10)の製造に関し、この半導体デバイスは、少なくとも1つの接続領域(4)と、接続領域に接続された、上に位置する帯状の接続導体(5)と、を備え、この接続領域および接続導体は、両方とも誘電体に凹設され、第1材料の誘電体領域(6)が、半導体ボディ(1)の、接続領域(4)が形成される位置に設けられ、その後、誘電体領域(6)は、第1材料とは異なる第2材料の誘電体層(7)で被覆され、この誘電体層には、帯状の接続導体(5)が形成される位置に帯状の凹部(7A)が設けられ、この凹部は、誘電体領域(6)に重なり、かつ前記誘電体領域まで延び、凹部(7A)の形成と誘電体領域(6)の除去の後、接続領域(4)が、誘電体領域(6)の除去により作られた空間(6A)に導電性材料を堆積することにより形成され、接続導体(5)が、凹部(7A)に導電性材料を堆積することにより形成される。本発明によると、第1材料には、有機材料が用いられ、第2材料には、この有機材料より高い分解温度を有する材料が用いられ、誘電体領域(6)は、有機材料の分解温度より高く、第2材料の分解温度よりは低い温度で加熱することにより除去される。本発明に係る方法は、非常にシンプルであり、第2材料を任意に選択することにより、得られるデバイス(10)に高い平面性をもたらすことができる。誘電体領域(4)には、好ましくはフォトレジストが用いられ、誘電体層(7)には、好ましくはSILKまたはSOG材料などの液体材料が用いられ、これは、加熱により固体状に変換することができる。  (もっと読む)

(もっと読む)

ナノ粒子インクを用いた配線形成方法

【課題】ナノ粒子インクを用いた配線形成にあたり、インク使用効率の向上、インク着弾精度の緩和、配線断面の順テーパ形成を実現すること。

【解決手段】第1段階のフォトリソグラフィー工程において、フォトレジスト2を全面に塗布した基板1上に配線領域10を形成する際、そのレジスト断面が逆テーパ形状となるように露光する。ついで、第2段階のインク噴射工程において、インクジェット方式を採用し、ナノ粒子インクを配線領域10に噴射する。その後、レベリング工程、乾燥工程、レジスト剥離工程、焼成工程を経て配線を形成する。

(もっと読む)

現像液に可溶な材料および現像液に可溶な材料をビアファーストデュアルダマシン適用において用いる方法

【課題】ポリアミド酸またはポリエステルのプラットフォームに基づく湿式凹部形成(現像)ギャップ充填および底反射防止コーティングを提供する。

【解決手段】ポリアミド酸のプラットフォームは、熱エネルギーが供給されると、イミド化が可能になり、ポリイミドを形成する。ギャップ充填および底反射防止コーティングは、標準の水性現像液に可溶であり、またデュアルダマシンパターン形成法において、半導体基板上のビア孔およびトレンチのパターン形成に有用である。1つの実施例では、各ビア列間の疎密偏りを改善するために、銅デュアルダマシンプロセスにおいて、ポリアミド酸からなる組成物を反射防止機能を持たないギャップ充填(ビア充填)材料として用いる。別の実施例では、同じ組成物を反射防止目的に用いることができる。ここでは、凹部が形成された表面にフォトレジストを直接コーティングし、基板上のビア孔を平坦化するための充填材料としても機能させる。ここに記述する組成物は、およそ370nm未満の露光波長の時に特に有用である。

(もっと読む)

ビア・ファースト・デュアルダマシン相互接続配線形成のための構造体充填方法

厚さが溶剤により容易に制御できる間隙充填底部反射防止膜を用いたビア・ファースト・デュアルダマシン相互接続構造体を形成する方法である。基板に塗布後、底部反射防止膜は低温焼成により部分硬化される。次に皮膜したウェハ上に溶剤を施し、膜と一定時間接触させて置く。底部反射防止膜の焼成温度と溶剤との接触時間により制御できる速さで溶剤が底部反射防止膜を除去しつつも、薄い底部反射防止膜を作り誘電体積層上に最適の光吸収特性は維持される。本方法の別の実施例では底部反射防止膜を充分除去し、ビアを単に部分充填し、続く処理工程でビア底部が保護されるようにしてもよい。溶剤はウェハから除去され、底部反射防止膜は高温焼成処理により完全に硬化される。次にウェハはフォトレジストにより被覆されトレンチパターンが露出する。使用される底部反射防止膜材によりトレンチパターン形成上、より平坦な表面形状が維持され、誘電体積層上に無機光吸収材層を設ける必要がなくなり、トレンチのエッチング工程時ビアの底部を保護し、溶剤を用いてビアの厚さを制御することにより境界問題の発生を防止する。 (もっと読む)

21 - 31 / 31

[ Back to top ]