Fターム[5F038BB02]の内容

Fターム[5F038BB02]に分類される特許

1 - 20 / 147

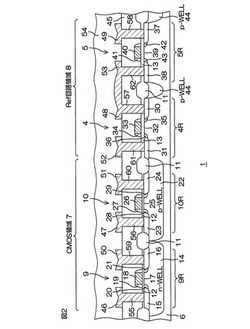

半導体装置および半導体装置の製造方法

【課題】基準電圧発生回路を構成するエンハンスメント型MOSFETとデプレッション型MOSFETとの間の温度特性の差を小さくすることができ、基準電圧発生回路の出力電圧の温度特性を改善することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板6上においてRef回路領域8およびCMOS領域7に跨るようにゲート絶縁膜66を形成した後、CMOS領域7の部分を選択的に除去する。次に、熱酸化により、ゲート絶縁膜66が除去されたCMOS領域7に第1ゲート絶縁膜12を形成し、同時に、Ref回路領域8に残っているゲート絶縁膜66を厚くして第1ゲート絶縁膜12よりも厚い第2ゲート絶縁膜13を形成する。

(もっと読む)

出力回路

【課題】高電圧信号を出力する回路を低耐圧トランジスタで構成しても、信頼性を向上させることのできる出力回路を提供する。

【解決手段】実施形態の出力回路は、出力部1が、高電圧電源端子VCCHと出力端子とZの間に接続されPMOSトランジスタP11、P12と、接地電位端子GNDと出力端子Zとの間に接続されたNMOSトランジスタN11、N12とを有し、低電圧入力信号INが入力されるプリバッファ部2が、PMOSトランジスタP11、NMOSトランジスタN11へ、VCCHよりも小さい振幅のゲート電圧PG、NGを出力する。PMOSトランジスタP12およびNMOSトランジスタN12のゲート端子へVCCHよりも低い定電圧VGが印加され、PMOSトランジスタP12の基板へVCCHよりも低い基板バイアス電圧VBPが印加され、NMOSトランジスタN12の基板へ接地電位よりも高い基板バイアス電圧VBNが印加される。

(もっと読む)

電圧調整回路、電圧調整方法および固体撮像装置

【課題】低消費電力で、かつ、発生する電圧に依存することなく消費電力が一定している電圧調整回路を提供する。

【解決手段】半導体基板上に形成され、発生する電圧を調整するための回路であって、直列に接続された複数の抵抗体(抵抗11、12、13a〜13f)と、複数の抵抗体の接続点のそれぞれに一端が接続され、他端がお互いに共通に接続された第1組の複数のヒューズ31a〜31gと、共通に接続された第1組の複数のヒューズ31a〜31gの他端に接続された第1の出力端子2とを備える。

(もっと読む)

電気回路の製造方法及び電気回路

【課題】所定の電圧値の検出に適した電気回路とその製造方法を提供する。

【解決手段】コンパレーターと、基準電圧生成回路と、第1の電源との接続側に設けられた第1のヒューズを有する第1のユニットと、第2の電源との接続側に設けられた第2のヒューズを有する第2のユニットと、を含み、前記第1のユニットと前記第2のユニットとが縦列接続され、前記第1の電圧は前記第1のユニットと前記第2のユニットとの間の所定の位置における電圧であり、前記基準電圧生成回路は、前記第1の電源及び前記第2の電源から前記基準電圧を生成し、前記第1のヒューズ及び前記第2のヒューズを切断しない状態で前記コンパレーターの出力が変化するときの前記第1の電源の電圧を測定する第1の工程と、前記第1の工程における測定結果に基づき、前記第1のヒューズ及び前記第2のヒューズの切断を行う第2の工程と、を有する。

(もっと読む)

温度検出装置、温度検出回路およびパワー半導体モジュール

【課題】温度検出回路と絶縁素子とを同一の基板上に形成できるようにし、装置全体の小型化を容易にする温度検出装置を提供する。

【解決手段】温度検出回路200は、温度センサ35で検出された温度をデジタル値に変換するAD変換回路44とデジタル比較回路45を備えている。デジタル比較回路45の出力は、第1パルス発生器52、第2パルス発生器53を経由して絶縁トランス回路101に入力される。絶縁トランス回路101で発生する誘導電流によりパルス信号が信号復調回路102に伝達される。また、温度センサ35で検出された温度が限界温度を越えたときにコンパレータ49からパルス信号が生成され、同様に、信号復調回路102に伝達される。

(もっと読む)

半導体装置

【課題】パッケージ応力に起因する回路部品の電気特性変動のバラツキによって出力信号が変動する内部回路について、パッケージ応力に起因する出力信号の変動を防止する。

【解決手段】半導体チップ5に形成された内部回路はその回路を構成する複数の回路部品の電気特性の変動のバラツキによって出力信号が変動するものである。チップタブ3の平面サイズは半導体チップ5の平面サイズよりも小さい。上方から見てチップタブ3の配置位置の全部が半導体チップ5の配置位置と重なっている。さらに、封止樹脂13に起因して半導体チップ5に加わる応力の大きさがチップタブ3上で均一になる位置関係でチップタブ3の周縁と上記半導体チップ5の周縁は間隔をもって配置されている。上記回路部品は半導体チップ5内部で上記チップタブ3上に配置されている。

(もっと読む)

半導体装置および基準電圧生成回路

【課題】所望の温度特性を有することによって回路規模を小さくできるMOSトランジスタを提供する。

【解決手段】ゲート絶縁膜30は、ソース領域51とドレイン領域52との間の領域の上に設けられる。ゲート電極40は、ゲート絶縁膜30の上に設けられる。空乏層42は、P型半導体層41とP型半導体層41の下層(ゲート絶縁膜30)との接合面に生じる。温度が変化すると、ゲート電極40内部の空乏層42の領域が変化し、チャネル形成に対するゲート電圧の影響が変化するので、閾値電圧は通常のMOSトランジスタの場合よりも変化する。このことを利用し、MOSトランジスタが所望の温度特性を有するよう制御されるので、温度補正回路が不要になる。よって、回路規模が小さくなる。

(もっと読む)

ダイオード装置およびダイオード装置の評価方法

【課題】ダイオードへの逆方向電圧の印加後順方向電圧を印加した直後の早い時間領域でダイオードの電流コラプス特性を評価することができるダイオード装置およびダイオード装置の評価方法を提供する。

【解決手段】ダイオード装置100において、第1の回路と、第1の回路と並列に接続され被測定ダイオード107を有する測定回路と、第1の回路および測定回路と並列に接続され被測定ダイオード107のカソード側の電位を所定の電位にクランプするクランプ回路111と、第1の回路、測定回路およびクランプ回路と並列に接続された第2の回路とを備え、被測定ダイオード107のカソード電位は、被測定ダイオード107のカソード電位が所定値未満の場合に、クランプ回路111の出力端子の電位にクランプされる。

(もっと読む)

半導体装置

【課題】電圧生成回路を備えた半導体装置において、電圧生成回路の電荷供給能力が十分でない場合であってもチャージシェアを引き起こすことなく、電圧生成回路の出力電圧を従来よりも高精度に検出できるようにする。

【解決手段】半導体装置1は、電圧生成回路11と、第1のスイッチSW2と、充電回路20とを備える。電圧生成回路11は、電圧を生成して出力し、生成する電圧の大きさを調整する機能を有する。第1のスイッチSW2は、オン状態のときに互いに導通する第1および第2の導通端子を有し、第1の導通端子が電圧生成回路11の出力ノードと配線を介して接続される。充電回路20は、第1のスイッチSW2の第2の導通端子に接続された配線を充電する。

(もっと読む)

貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法

【課題】貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法を提供する。

【解決手段】複数の半導体レイヤ間で伝送される情報の衝突を防止する構造を有する半導体装置であり、該半導体装置は、第1温度情報を出力する第1温度センサ回路を含む少なくとも1つの第1半導体チップと、貫通電極に電気的に連結されずに、第1温度センサ回路に電気的に連結される第1バンプと、第1半導体チップの貫通電極に電気的に連結される第2バンプと、を具備する半導体装置であることを特徴とする。

(もっと読む)

スタートアップ回路及び基準電圧発生回路

【課題】リーク電流の増大を抑制等しつつ、コア面積が小さいスタートアップ回路を提供すること。

【解決手段】本発明にかかるスタートアップ回路は、基準電圧Voutを発生する基準電圧発生部20に対して電源電圧供給開始時にスタートアップ電流Isrtupを供給し、基準電圧Voutを安定化させるスタートアップ回路10であって、基準電圧Voutを検出し、検出結果に応じた制御電圧Vstを出力するモニタ回路13と、電源電圧VDDに応じた電圧レベルの中間電圧Vnを生成し出力するレベルシフタ11と、中間電圧Vnに応じたスタートアップ電流Isrtupを、基準電圧発生部20に対して供給するか否かを制御電圧Vstに基づいて制御するスイッチ回路12と、を備える。

(もっと読む)

集積回路装置及び電子機器

【課題】簡素な構成で、電圧発生回路の電源電圧が上昇した場合でも出力電圧の変動を精度よく抑制できる集積回路装置及び電子機器等を提供する。

【解決手段】集積回路装置100は、ソース同士が接続された第1の入力トランジスター及び第2の入力トランジスターにより構成される入力差動対と、第1の入力トランジスターのドレイン電圧に基づいてゲート電圧を制御される出力トランジスターと、第1の入力トランジスターのドレイン電流と第2の入力トランジスターのドレイン電流との差の電流を出力トランジスターのゲートに供給するカレントミラー回路と、出力トランジスターのゲート及びドレインの間に挿入される第1の容量と、入力差動対を構成するトランジスターの少なくとも一方のソース・ドレイン間に流れる電荷量に対して、第2の電圧に対する第1の電圧の上昇分に対応した電荷量を増加させる電圧変動抑制回路とを含む。

(もっと読む)

バンドギャップ型基準電圧発生回路

【課題】バンドギャップ型基準電圧発生回路において、高温における寄生ダイオードのリーク電流の影響を制御して、基準電圧の温度特性の向上を図る。

【解決手段】NPN型BIPトランジスタQ1の寄生ダイオードD1とは別に、i個(iは1以上の自然数)の温度特性制御ダイオードD31〜D3iをNPN型BIPトランジスタQ1のコレクタに接続する。温度特性制御ダイオードD31〜D3iは、Pチャネル型MOSトランジスタM1,M2からなるカレントミラー回路を介して、寄生ダイオードD21〜D2Kのリーク電流の増加による基準電圧Vrefへの影響をキャンセルするように作用する。

(もっと読む)

半導体集積回路

【課題】外部電源電圧を降圧するレギュレータを内蔵することによるチップ面積の増大を抑え且つ降圧電圧の安定化を実現できる半導体集積回路を提供する。

【解決手段】外部電源電圧(Vext)よりも低い内部電源電圧(Vint)で動作する内部回路を持つ半導体集積回路において、内部電源電圧を生成するレギュレータ(150〜157)を、バッファ及び保護素子を配置するための第2の領域(2)に配置することにより、降圧電源回路のオンチップ化による面積オーバヘッドを低減する。降圧電圧を伝達するループ状の電源幹線(L20)を用い、電源幹線に外付け安定化容量を接続するための電極パッドを設ける等により、低消費電力を更に促進する。

(もっと読む)

半導体装置、及び、その製造方法

【課題】半導体装置、及び、その製造方法を提供する。

【解決手段】PN接合を有する第1半導体素子と、PN接合を有する第2半導体素子と、第1半導体素子と第2半導体素子とを構成要素として含む回路と、を有し、回路から、第1半導体素子のPN接合に生じる第1順方向電圧と、第2半導体素子のPN接合に生じる第2順方向電圧とが加算された加算信号が出力される半導体装置であって、第1半導体素子と第2半導体素子とが直列接続されており、第1半導体素子及び第2半導体素子それぞれの実使用温度域において、回路が第2半導体素子を構成要素として含まない場合に、回路から出力される第1信号の温度特性と、回路が第1半導体素子を含まない場合に、回路から出力される第2信号の温度特性と、が反転している。

(もっと読む)

制御電圧生成回路、定電流源回路及びそれらを有する遅延回路、論理回路

【課題】回路規模を増大させることなくトランジスタの閾値電圧に応じた制御電圧を精度良く生成することが可能な制御電圧生成回路を提供すること。

【解決手段】本発明にかかる制御電圧生成回路は、高電位側電源と低電位側電源との間に直列に接続された同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのドレイン電圧を参照電圧Vp1として生成する参照電圧生成部11と、高電位側電源と低電位側電源との間に直列に接続され参照電圧生成部11と同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのゲートに参照電圧が供給され、何れかのMOSトランジスタのドレイン電圧を制御電圧(バイアス電圧)として出力する電圧変換部12と、を備える。

(もっと読む)

半導体装置

【課題】トリミングデータによって調整可能な基準電圧発生回路を備えた半導体装置において、電源が立上がるまでの基準電圧のばらつきの影響を受けないようにする。

【解決手段】半導体装置10において、基準電圧生成部1は、外部電源電圧VCCに基づいて、トリミングデータTRM1に応じて調整された第1の基準電圧V1*およびこのトリミングデータTRM1に依存しない第2の基準電圧V2を生成する。不揮発性メモリ3は、第1の基準電圧V1*に基づく電圧によって動作し、上記のトリミングデータTRM1を記憶する。パワーオンリセット回路5は、電源立上げ時に外部電源電圧VCCが第2の基準電圧V2の定数倍に達したときにリセット信号の論理レベルを切替える。制御回路6は、リセット信号の論理レベルの切替に応答して、不揮発性メモリ3に記憶された上記のトリミングデータTRM1を基準電圧生成部1に読込ませる。

(もっと読む)

半導体集積回路装置

【課題】SOI基板に形成されたMOSトランジスタを含む半導体集積回路装置において、半導体集積回路装置に入力される電源電圧が高い場合であっても、SOI基板のBOX酸化膜やシリコン層を厚くすることなく、回路動作を安定させる。

【解決手段】MOSトランジスタM1〜M9は、シリコン基板、BOX酸化膜及びシリコン活性層を有するSOI基板に形成され、かつ、ソース拡散層の底部及びドレイン拡散層の底部がBOX酸化膜に到達して形成されている。エンハンスメント型PchMOSトランジスタM3,M4、M5,M7は、デプリーション型NchMOSトランジスタM10を介して、電源電圧が入力される電源端子VDDに接続されている。MOSトランジスタM10は、ソース、ゲート及びボディが結線されて定電流源として機能し、ソース電位がシリコン基板電位よりも高くなることで飽和電流が減少する電気的特性をもっている。

(もっと読む)

リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法

【課題】 リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法に関し、複数種類のデバイス特性をできるかぎり同じ構造のモニタで評価する。

【解決手段】 形状或いはしきい値電圧の少なくとも一方が異なる複数種類のトランジスタを異なった領域に同じ間隔で配置するとともに、前記複数種類のトランジスタの内、設計データにおける設置頻度の比を反映した数のトランジスタのゲート電極同士、ソース電極同士、及び、ドレイン電極同士を電気的に共通に接続する。

(もっと読む)

半導体集積回路装置

【課題】被制御回路のソース電位を精度良く制御する回路構成を小面積で実現する。

【解決手段】電源線6及び接地線4に接続された被制御回路1のソース線5と、前記接地線4との間に、前記ソース線5の電位を制御するソース制御回路2と、前記ソース線5と前記接地線4とを導通、非導通状態へ制御する、前記ソース制御回路2と並列に接続された遮断スイッチ回路3とを有する。ソース制御回路2は、ダイオード回路2aと、前記ダイオード回路2aと並列に接続された抵抗回路2bとを有する。

(もっと読む)

1 - 20 / 147

[ Back to top ]