Fターム[5F038BH18]の内容

Fターム[5F038BH18]に分類される特許

1 - 20 / 220

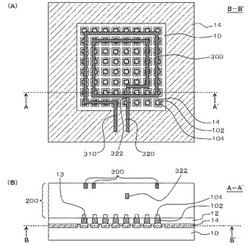

半導体装置

【課題】インダクタの下方に位置する素子分離膜に開口を設けてその開口内に半導体基板を残しつつ、インダクタの下方に位置する半導体基板に渦電流が発生することを抑制する。

【解決手段】インダクタ300は、多層配線層200に形成されており、素子分離膜12の上方に位置している。開口13は、素子分離膜12のうち少なくとも平面視でインダクタ300と重なる領域に形成されている。また、素子分離膜12とインダクタ300の間に位置するいずれの層にも、インダクタ300と半導体基板10の間をシールドするシールド導電部材は形成されていない。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置に負電流が流れた場合でも、回路素子を構成する深い半導体層の電位に対して、半導体基板の電位が低くなるのを抑制して寄生素子を作動させず、半導体装置の誤動作を防止する。

【解決手段】本発明は、n型の半導体基板3と、半導体基板3の一面に形成し、接続する負荷に電力を供給する電力素子1と、n型のソース・ドレイン領域を有するMOSトランジスタ2cを少なくとも1つ含む回路素子2と、電力素子1および回路素子2に対し独立して配置したp型の半導体層4と、半導体基板3および半導体層4と接続する外部回路とを備えている。外部回路は、電源と、電源に一端を接続する抵抗素子と、抵抗素子の他端にアノード電極を接続し、カソード電極をGND接地するダイオードとを有し、抵抗素子の他端に半導体層4を接続する。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、I/Oセルの高さを低減すると同時に幅の増大を防ぐことでI/Oセルの占める領域の面積を削減すること。

【解決手段】レベルシフタ回路、I/Oロジック回路およびI/Oバッファ回路を含むI/Oセルがコア領域の周囲に配置された半導体集積回路装置であって、I/Oロジック回路が配置されたI/Oロジック領域、および、I/Oバッファ回路が配置されたI/Oバッファ領域は、I/Oセルに対するパッドが配置された領域と重なり合うとともに、コア領域の辺に平行な方向に互いに並んで配置されている。

(もっと読む)

チャージポンプ及びこれを用いた電源装置

【課題】プリント配線基板上の実装面積削減やコスト削減を実現することのできるチャージポンプを提供する。

【解決手段】チャージポンプ100は、フライングキャパシタ120の充放電用スイッチとして、半導体装置110に集積化されたフローティングNMOSFET111及び112のボディダイオード111d及び112dを用いる。

(もっと読む)

半導体集積回路

【課題】保護素子とガードリング領域との間のウィークスポットが破壊される危険性を軽減する。

【解決手段】半導体集積回路は、静電保護回路の保護素子Mn2を形成するために、第1導電型の半導体領域P−Wellと第2導電型の第1不純物領域Nと第1導電型の第2不純物領域Pにより形成されたガードリングGrd_Rngを具備する。第1不純物領域Nは、長辺と短辺を有する長方形の平面構造として半導体領域の内部に形成される。ガードリングは、第1不純物領域Nの周辺を取り囲んで半導体領域の内部に形成される。第1不純物領域Nの長方形の平面構造の短辺には、ウィークスポットWk_SPが形成される。長方形の長辺と対向するガードリングの第1部分では、複数の電気的コンタクトが形成される。長方形の短辺に形成されるウィークスポットと対向するガードリングの第2部分では、複数の電気的コンタクトの形成が省略される。

(もっと読む)

金属酸化物半導体出力回路およびそれを形成する方法

【課題】金属酸化物半導体(MOS)出力回路とその形成方法の提供。

【解決手段】第一パッド61と、ゲート、第一の供給電圧に電気的接続のソース、ドレインを含む基板で第一型の第一MOSトランジスタ62と、ゲート、制御信号を受信する構成のソース、第一MOSトランジスタのゲートに電気的接続のドレイン、本体を含む基板で第一型と反対の第二型の第二MOSトランジスタ65と、バイアス信号を受信する構成のゲート、第二供給電圧に電気的接続のドレイン、第二MOSトランジスタのソースに電気的接続のソース、第一参照電圧に電気的接続の本体を含む基板で第一型の第三MOSトランジスタ66とを含み、第二MOSトランジスタの本体は第三MOSトランジスタのソースに電気的接続、一時的な信号イベントの第一パッド上の受信の場合、第二MOSトランジスタのドレインから第二供給電圧まで第二MOSトランジスタの本体を流れる電流を妨げる集積回路。

(もっと読む)

半導体装置、半導体パッケージ、および半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】N型基板10と、N型基板10の一面側に設けられたP型ウェル40と、P型ウェル40に設けられたP型高濃度不純物領域42と、P型ウェル40に設けられたN型のソース・ドレイン領域を有するMOSトランジスタ20と、N型基板10の一面側に設けられ、かつ一方がP型高濃度不純物領域42と電気的に接続し、他方が接地されているソース・ドレイン領域を有するMOSトランジスタ30と、を備える。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

可変容量回路およびシステム

【課題】 電気信号の電圧振幅が大きいときにも、可変容量回路に形成されるトランジスタの寄生ダイオードがオンすることを防止し、電気信号の波形が歪むことを防止する。

【解決手段】 可変容量回路は、電気信号が伝達されるノードに一端が接続される容量素子と、容量素子の他端と第1電源線との間に配置される第1トランジスタと、他端と第2電源線との間に直列に配置される抵抗素子および第1トランジスタと極性が逆の第2トランジスタとを含んでいる。第1トランジスタはゲートで第1制御信号を受け、第1モード中にオンし、第2モード中にオフする。第2トランジスタは、ゲートで第2制御信号を受け、第1モード中にオフし、第2モード中にオンする。これにより、容量素子の他端の中心電圧は、第1トランジスタのオフ中に第2電源線の電圧に設定され、第2トランジスタのオフ中に第1電源線の電圧に設定される。

(もっと読む)

チャージポンプ回路

【課題】寄生トランジスタが発生する場合であっても、目的レベルの出力電圧を生成できるチャージポンプ回路を提供する。

【解決手段】入力電圧に応じた出力電圧を生成するチャージポンプ回路は、入力電圧を積分した積分電圧を出力する積分回路と、積分電圧が印加される入力電極及び基板電極を有するNMOSトランジスタと、NMOSトランジスタに直列接続され、NMOSトランジスタと相補的にオンオフされるPMOSトランジスタと、NMOSトランジスタがオンされている場合に、クロック信号に基づいて充電され、PMOSトランジスタがオンされている場合に、クロック信号に基づいて放電される第1コンデンサと、PMOSトランジスタがオンされている場合に第1コンデンサから放電された電荷が充電され、出力電圧を生成する第2コンデンサと、を備えることを特徴とするチャージポンプ回路。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗素子について、レイアウト面積の増大を防ぎつつ、周辺の電荷の影響を受けずに安定した抵抗値を得ることができ、しかも、抵抗体に印加できる電位の極性に制限のない半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1上のLOCOS酸化膜3上に形成された抵抗素子10と、を備え、抵抗素子10は、LOCOS酸化膜3上に形成されたシールド用ポリシリコン膜11と、シールド用ポリシリコン膜11上に形成されたシリコン酸化膜13と、シリコン酸化膜13上に形成されたポリシリコン抵抗体15と、ポリシリコン抵抗体15の一方の端部に接合された第1の電極21と、ポリシリコン抵抗体15の他方の端部に接合された第2の電極22と、シールド用ポリシリコン膜11に接合された第3の電極23と、を有し、第1の電極21及び第2の電極22うちの一方が、配線25を介して第3の電極23と電気的に接続されている。

(もっと読む)

シンクロナス整流器或いは電圧クランプ用の3端子パワーMOSFETスイッチ

【課題】パワー変換器に於けるシンクロナス整流器として適するMOSFETスイッチを提供する。

【解決手段】互いに接続されソース及びボディが、ドレンよりはより正の側に高い電圧にバイアスされたN−チャネルパワーMOSFETを製造する。ゲートはスイッチ(1184)により制御され、ゲートを、ソース及び当該MOSFETのチャネルを完全にオンにするのに十分な電圧(VCP)のいずれか一方に選択的に接続する。ゲートがソースに接続されたとき、デバイスは、比較的低い電圧でオンし、従来のPN接合よりは低い導通抵抗を有する「擬似ショットキー」ダイオードとして機能する。ゲートが、前記した正の電圧に接続されたとき、MOSFETのチャネルは完全にオンとなる。このMOSFETスイッチは、電力損及び“break-before-make”時間に於ける蓄積電荷を低減する。

(もっと読む)

集積回路内における、インターフェースデバイスの面積効率の良い配列

【課題】過度にシステムの中にスキューを増加させずに、増加した数の入力/出力デバイスを有するシステムを提供する。

【解決手段】論理回路を備えるコアと、処理コアからおよび処理コアへ信号を伝送するための、複数のインターフェースデバイスであって、2つのタイプのインターフェースデバイスを備える、複数のインターフェースデバイスと、コアに電力を送達するための、電力インターフェースデバイスである、1つのタイプと、コアと集積回路の外部のデバイスとの間で、データ信号を伝送するための信号インターフェースデバイスである、第2のタイプと、を備え、複数のインターフェースデバイスは、コアの外縁に向かう外側列、およびコアの中心により近い外側列の内側にある内側列の、2列に配設され、内側列は、2つのタイプのインターフェースデバイスのうちの一方を備え、外側列は、2つのタイプのインターフェースデバイスのうちの他方を備える、集積回路が開示される。

(もっと読む)

半導体装置およびその製造方法

【課題】工程が簡単で、よりラッチアップに強いCMOS構造を得る。

【解決手段】1×1018cm−3から1×1019cm−3の高不純物濃度の半導体基板2を用い、CMOS構造のP型ウェル4とN型ウェル5の境界に設けられた溝分離部13の先端部分がその高不純物濃度領域に達する(エピタキシャル層3を貫通して半導体基板2の領域に至る)ように深く形成することにより、従来のように溝分離部13よりも更に深い領域(溝分離部13の下側)を電子が通過することなく、従来のようにウェル領域内にN+埋め込み層やP+埋め込み層を基板深く埋め込む必要もなく、簡便な方法で、よりラッチアップに強いCMOS構造を得ることができ、コスト性能の両方に優れた半導体装置1を得ることができる。

(もっと読む)

半導体装置

【課題】ウェル抵抗の抵抗値を簡便に調整することができる半導体装置を提供すること。

【解決手段】本発明に係る半導体装置50は、第1導電型のウェル抵抗30を備える半導体装置であって、半導体基板1の主表面側に形成された第1導電型のウェル抵抗領域4と、ウェル抵抗領域4の底部、及び側壁を取り囲むように形成された第2導電型の半導体基板領域2と、ウェル抵抗領域4内の少なくとも2箇所に、互いに離間して形成された高濃度の第1導電型の拡散領域であるコンタクト領域6と、ウェル抵抗領域4の外側端部の上部から、ウェル抵抗領域4を囲む半導体基板領域2の上部に素子分離膜を介して対向配置するように形成された、導電層からなる抵抗調整層20と、を備える。抵抗調整層20は、ウェル抵抗30の抵抗値が所望の値となるようにバイアスされている。

(もっと読む)

半導体集積回路のノイズ耐性評価方法およびノイズ耐性評価装置

【課題】大規模な半導体集積回路であってもノイズ耐性評価が短時間で可能なノイズ耐性評価方法を提供する。

【解決手段】回路ネットリストを作成する第1のステップS11と、能動素子を受動素子回路に置き換えて置換回路ネットリストを作成する第2のステップS12と、トランジスタの制御端子に該当する制御ノードを抽出する第3のステップS13と、ノイズ注入ノードを設定する第4のステップS14と、所定周波数のノイズを設定し、互いに異なる制御ノードとノイズ注入ノード間の経路のインピーダンスを計算する第5のステップS15と、制御ノード、ノイズ注入ノードおよび経路の各組み合わせにおけるインピーダンスのリストを作成する第6のステップS16と、インピーダンスの最小値から半導体集積回路のノイズ耐性を判定する第7のステップS17とを有してなるノイズ耐性評価方法100とする。

(もっと読む)

半導体装置

【課題】主電流Imとこれに対して比例関係にある検知電流Isとの出力用にIGBT素子44,45を備えたIGBTチップ10において、IsからIGBT素子のラッチアップを監視する。製造上のばらつきに対してIs/Imが設計値に調整可能にするとともに、調整抵抗のスペース節約や作業工数低減を図る。

【解決手段】Isを出力する原電極16とセンスパッド17と間の抵抗値を調整する調整抵抗部60は、短絡金属層67と共に作り込まれる。短絡金属層67は、調整抵抗部60の各抵抗64に対する並列接続部分により該各抵抗64の両端子を短絡している。各抵抗64は、レーザのトリミング加工により並列接続部分が切除されると、両端短絡状態を解除されて、調整抵抗部60の抵抗要素として機能する。調整抵抗部60の抵抗値は、抵抗要素となった抵抗64の接続関係及び抵抗値に応じた値になる。

(もっと読む)

昇圧回路およびブーストコンバータ

【課題】電力の消費を抑制すると共に供給された電圧をより適正に昇圧する。

【解決手段】トランジスタ回路14a,14bのトランジスタTr1,Tr3の半導体基板20には、それぞれトランジスタ回路14b,14cのドレイン接続端子Td2からの電圧V2,V3を順に印加し、トランジスタ回路14cのトランジスタTr1,Tr3の半導体基板20には、トランジスタ回路14cのドレイン接続端子Td2からの電圧V3を印加し、トランジスタ回路14b,トランジスタ回路14cのトランジスタTr2,Tr4のウェル30には、トランジスタ回路14a,14bのドレイン接続端子Tr1からの電圧V0,V1を順に印加する。これにより、電力の消費を抑制すると共に供給された電圧をより適正に昇圧することができる。

(もっと読む)

電力増幅器

【課題】 電力増幅器に発生するホットキャリアの影響を抑制する。

【解決手段】 一つの実施形態の電力増幅器には、半導体層に形成され、少なくとも1つ以上から構成され、電力増幅動作する第1のグロースリングゲート構造体と、半導体層に形成され、第1のグロースリングゲート構造体を取り囲むように隣接配置され、第1の構造体が電力増幅動作するときに、逆バイアスが印加されて空乏化領域が形成され、第1の構造体を周囲からアイソレートする複数の第2のグロースリングゲート構造体とが設けられる。

(もっと読む)

半導体集積回路及び半導体集積回路装置

【課題】従来技術と比較して占有面積が小さく、かつ基板電流が流れる経路の抵抗を低く抑え、寄生バイポーラトランジスタの動作を抑制することができる半導体集積回路及び半導体集積回路装置を提供する。

【解決手段】p型半導体基板10に形成されたドレイン領域D1、ソース領域S1、及びp型活性領域Bと、ドレイン領域D1とソース領域S1との間に形成されたゲート電極TG1と、ドレイン電極TD1と、ソース電極TS1と、基板電極TB1とを備えたNMOSトランジスタMN1と、ソース領域S1とp型活性領域Bとの間に形成されたドレイン領域D2及びソース領域S2と、p型活性領域Bと、ドレイン領域D2とソース領域S2との間に形成されたゲート電極TG2と、ドレイン電極TD2と、ソース電極TS2と、基板電極TB2とを備えたNMOSトランジスタMN2とを備え、NMOSトランジスタMN2は、基板電極TB1とソース電極TS1との間に接続される。

(もっと読む)

1 - 20 / 220

[ Back to top ]