Fターム[5F048AC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 集積回路要素 (9,617) | MOS+MOS (7,604) | パワーMOSを含む (667)

Fターム[5F048AC06]に分類される特許

661 - 667 / 667

パワー半導体デバイスおよびその製造方法

改善されたパワーデバイスに対するさまざまな実施例と同様に、その製造方法,多種多様のパワーエレクトロニックアプリケーションにおける使用に対して、当該パワーデバイスを組み込んだパッケージングおよび回路が開示されている。本発明の1つのアスペクトは、多くの電荷調整法および寄生容量を低減する他の方法を組み合わせることによって、改善された電圧性能,速いスイッチング速度および低いオン抵抗を有するパワーデバイスに対する異なる実施例に至る。本発明の別のアスペクトは、低電圧,中程度の電圧および高電圧のデバイスに対する、改善された終端構造を与える。パワーデバイス製造の改善された方法は、本発明の他のアスペクトによって与えられている。例えば、トレンチの形成,トレンチ内部の誘電体層の形成,メサ構造の形成および基板厚さを低減する工程のような、特定の処理ステップに対する改善が示されている。本発明の他のアスペクトによると、電荷調整パワーデバイスは、例えば同じチップ上のダイオードのような、温度および電流の検出部を組み込んでいる。本発明の他のアスペクトは、パワーデバイスに対する等価直列抵抗(ESR)を改善し、パワーデバイスと同じチップ上にさらなる回路を組み込み、電荷調整パワーデバイスのパッケージングに対する改善を与える。  (もっと読む)

(もっと読む)

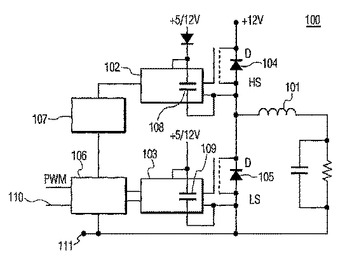

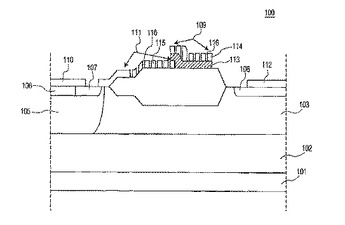

集積VRMパワー電界効果トランジスタ用の集積インタフェース回路構造

ダウンコンバータは、インタフェース部を含み、当該インタフェース部は、当該ダウンコンバータを、複数のスイッチ(104、105)と、それぞれのスイッチのドライバ回路からなる複数のドライバ回路(102、103)とに接続し、前記複数のドライバ回路と前記複数のスイッチとが、集積回路上で組み合わされている。前記複数のドライバ回路は、上側ドライバ回路(102)と下側ドライバ回路(103)とを含む。前記複数のドライバ回路が、前記複数のスイッチと共に集積されることで、寄生インダクタンス、特に電力供給の際の寄生インダクタンスが減少する。  (もっと読む)

(もっと読む)

電界効果型半導体装置における容量素子の動的制御

電界効果型装置はキャパシタのプレートをそれぞれ形成する複数のセグメントを有する少なくとも1つのセグメント化されたフィールド・プレートを含んでおり、選択されたセグメントを動的に接続してゲート−ドレイン間容量及びドレイン−ソース間容量を選択的に設定する電子素子に電界効果型装置が接続されている。トランスデューサを送信モードスイッチング装置と、受信モードスイッチング装置との間でスイッチングするスイッチング装置に結合されたトランスデューサを超音波装置が含んでおり、このスイッチング装置は電界効果型装置を含んでいる。  (もっと読む)

(もっと読む)

集積化電子切断回路、方法およびシステム

過渡現象遮断用の組み合わせデバイス。過渡現象が入力端子 40に印加されると、トランジスタ 44のボディ電位がデプレッションモードJFET型遮断トランジスタ 71のゲート 81を駆動するように、パストランジスタ44が配置されている。同時に、チャネル77を空乏化するために、電位差 Vdが外部ゲート 52の両端に印加される。このように、外部端子上に現れる過渡現象は、非常に急速に伝播されて、チャネル 77および85を空乏化するので、出力端子42に接続されたデバイスが故障する前に、入力端子 40を出力端子 42から効果的に分離する。一旦過渡現象がおさまると、デバイス 37はその通常の導通状態に戻る。 (もっと読む)

半導体装置

【課題】低オン抵抗の縦型トランジスタが形成されてなる半導体装置を提供する。また、マルチチャネル化の自由度の高い半導体装置を提供する。

【解決手段】半導体基板30の一方の表面である主面側に形成された第1電極と、もう一方の表面である裏面側に形成された第2電極とを有する縦型トランジスタ101が形成されてなる半導体装置100であって、第1電極が、主面上に形成された層間絶縁膜43を介して、主面側の半導体基板30表層部に形成された拡散領域41,42,48に接続する第1金属層44からなり、裏面側には、半導体基板30の内部に向かってトレンチ35が形成され、第2電極が、トレンチ内に形成され、トレンチ35によって露出された半導体基板30内の半導体層33に接続する第2金属層37からなる半導体装置100とする。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 サブミクロンCMOSトランジスタを、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗などと一緒に、それぞれの特性を劣化させることなく、同一基板上に混載すること。

【解決手段】 半導体基板1の一主面側にパンチスルーストッパー層を形成する際に、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗を形成する領域をマスクしてたとえばイオン注入をおこなう。それによって、サブミクロンCMOSトランジスタの形成領域にパンチスルーストッパー領域4を形成するとともに、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗の形成領域にパンチスルーストッパー領域が形成されるのを防ぐ。

(もっと読む)

半導体装置とその製造方法

【課題】 高耐圧MOSトランジスタの微細化を図る。

【解決手段】 P型ウエル3上にゲート酸化膜9を介して形成されたゲート電極27Fと、前記ゲート電極27Fから離間されて形成される高濃度のN型ソース・ドレイン層15と、前記ソース・ドレイン層15を取り囲むように形成され、前記ゲート電極27F下方に形成されたP型ボディ層18で分断された低濃度のN型のソース・ドレイン層10とを具備したことを特徴とする。

(もっと読む)

661 - 667 / 667

[ Back to top ]