Fターム[5F048BA11]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 基板中にキャリア再結合中心を添加したもの (8)

Fターム[5F048BA11]に分類される特許

1 - 8 / 8

半導体装置およびその製造方法

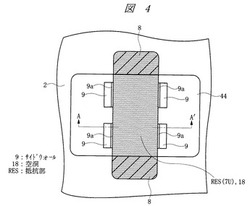

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタと、抵抗素子とを同一基板に有する半導体装置において、安定したHK/MGトランジスタの動作特性を得ることのできる技術を提供する。

【解決手段】TiN膜と多結晶Si膜との積層膜からなるHK/MGトランジスタのゲート電極を形成し、同様に、TiN膜と多結晶Si膜との積層膜からなる抵抗素子を形成した後、抵抗素子の側壁に形成したオフセットサイドウォール9aおよびサイドウォール9の一部を除去し、そのオフセットサイドウォール9aおよびサイドウォール9が除去された箇所から薬液を浸入させることによりTiN膜を除去して空洞18を形成し、多結晶Si膜のみからなる抵抗部RESを形成する。

(もっと読む)

局所的に不動態化されたゲルマニウムオンインシュレータ基板の製造方法

【課題】 GeOxNy層によって、所望の不動態化と電子移動度に関する所望の改善とが可能なゲルマニウムオンインシュレータ基板の製造方法を提供する。

【解決手段】 本発明は、局所的に不動態化されたゲルマニウムオンインシュレータ基板を製造するための方法に関し、電子の高移動度を実現するために、窒化された領域が局所化された位置に形成される。窒化はプラズマ処理によって実現される。

(もっと読む)

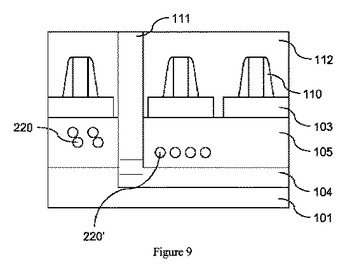

埋め込み型トラッピング層によるトランジスタの閾値電圧の調整方法

方法は、電子サブアセンブリの形成について、調整可能な閾値電圧を有する少なくとも1つの第1のトランジスタ(110)を担持する半導体層(103)が絶縁層(102、105)に接合される組み立てステップと、半導体層および第1のトラッピングゾーンが容量結合されるように、第1のトラッピングゾーン(220)が所定の第1の深さで絶縁層に形成される形成ステップであって、前記第1のトラッピングゾーンが、前記第1のトランジスタのチャネルの少なくとも下に延び、かつ前記第1のトラッピングゾーンの外側のトラップの密度より高い密度のトラップを有する形成ステップとを含み、前記第1のトランジスタからの有用な情報はこのトランジスタ内の電荷移動である。具体的な実施形態において、第2のトランジスタのチャネルの少なくとも下に延びる第2のトラッピングゾーンが、第1のトラッピングゾーンに使用されるのとは異なるエネルギーおよび/または用量および/または原子の第2の注入によって形成される。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】容易にかつ低コストで従来のようなゲッタリング効果を得られるゲッタリングサイトを形成する半導体装置を得ることを目的とする。

【解決手段】本発明の一実施形態における半導体装置の製造方法は、(a)半導体基板1を準備する工程と、(b)半導体基板1の表面側からイオン注入し、半導体基板1の表層部にアモルファス層2を形成する工程と、(c)半導体基板1に熱処理を行ってアモルファス層2を再結晶化した再結晶層3を形成し、半導体基板1と再結晶層3との界面近傍に微少結晶欠陥4を形成する工程と、(d)再結晶層3に半導体素子5を形成する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】コーナーラウンディング現象を抑制できるゲート電極構造を備えた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101に形成された素子分離領域102と、素子分離領域102に囲まれた活性領域103a、103bと、素子分離領域102及び活性領域103a、103b上に形成され、素子分離領域102上に活性領域103a、103b上に比べてゲート長方向のパターン幅が大きい第1の領域を有する第1のゲート電極105とを備える。第1のゲート電極105における第1の領域は、膜厚が活性領域103a、103b上の膜厚と異なる部分を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】スイッチング損失を低減することができ、混載されたバイポーラトランジスタ回路などの特性変動を抑制する。

【解決手段】コレクタ領域をP型不純物層8b、ベース領域をN型不純物層2、エミッタ領域をP型不純物層3とP型拡散層8aとP型基板1とする横型絶縁ゲートバイポーラトランジスタ(IGBT)であって、前記N型不純物層2内に格子欠陥層12を形成し、このN型不純物層2内に形成された格子欠陥層12がライフタイムキラーの役割を果たす。

(もっと読む)

半導体装置

【課題】 電流駆動能力を低下させることなくオン耐圧を改善可能な横形半導体装置を提供する。

【解決手段】 半導体素子形成領域120内に形成される横形半導体素子のドレイン領域121及びソース領域122、123が、SOI基板110表面の同一方向にストライプ状に伸びるように形成し、その周囲にドリフト領域124を形成している。これにより、ドレイン領域124の一部に電流が集中してオン耐圧が悪化されることを防止する。また、半導体素子形成領域120と、誘電体分離領域114を介して隣接する隣接領域に電位が固定される電位固定領域130を設けたことにより、横形半導体素子の耐圧特性が周辺素子の電位変動によって変動することが防止される。

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

1 - 8 / 8

[ Back to top ]