Fターム[5F048CC02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 保護回路の構成 (4,292) | 抵抗 (491) | 配置及び形状 (50)

Fターム[5F048CC02]に分類される特許

1 - 20 / 50

半導体装置

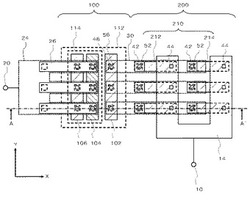

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

過電流保護回路

【課題】入力電源電圧の動作保証範囲が大きいとしても当該電圧変動の影響を抑制して正常に過電流保護を図るようにした過電流保護回路を提供する。

【解決手段】支持基板10が第1半導体層11および第2半導体層12を絶縁層13で挟んで構成されている。第1半導体層11上には絶縁膜14を介してフィールドプレート抵抗膜20が形成されている。可変電流源ISが、ゲート電極19からドレイン電極17にかけて絶縁膜14上に沿って形成されたフィールドプレート抵抗膜20(フィールドプレート抵抗R1およびR2)に生じるノードN1の電圧に応じて出力電流値を変更してセンス抵抗Rsの検出電圧V2を補正する。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、ノイズの発生が抑制された半導体装置を提供する。

【解決手段】実施形態の半導体装置は、ドレイン層と、ドレイン層の表面から内部にかけてトレンチ状に設けられたドリフト領域と、ドリフト領域の表面から内部にかけてトレンチ状に設けられたベース領域と、ベース領域の表面から内部にかけてトレンチ状に設けられたソース領域と、ドレイン層の裏面に対して略平行な方向に、ソース領域の一部からソース領域の一部に隣接するベース領域を貫通してドリフト領域の一部にまで到達する第1トレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、ドレイン層の表面から内部にかけて設けられた少なくとも1つの第2トレンチ内に第1絶縁膜を介して設けられた第1抵抗体層と、ドレイン電極と、ソース電極と、を備える。第1抵抗体層は、ソース電極に電気的に接続されている。

(もっと読む)

過電圧保護回路及び半導体集積回路

【課題】異常な過電圧から内部回路を確実に保護することができる過電圧保護回路を提供する。

【解決手段】過電圧保護回路2Aは、整流素子D10と、互いに並列に接続された第1段から第n段(nは2以上の整数)のスイッチング素子NM1〜NMnとを備える。スイッチング素子NM1〜NMnは、整流素子D10の出力端からの出力電圧が印加される第1から第nの制御端をそれぞれ有する。また、スイッチング素子NM1〜NMnの各々は、第1端子3及び第2端子4にそれぞれ接続された被制御端を有する。整流素子D10は、第1端子3から過電圧が入力されたとき、スイッチング素子NM1〜NMnをオン状態にする制御電圧を出力する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に含まれる静電気保護装置の面積を大きくすることなく、その破壊耐量及び維持電圧を大きくする。

【解決手段】第1導電型である半導体基板1と、半導体基板の上又は上部に形成された第2導電型である第1拡散層3と、第1拡散層の上部に形成され、第1導電型である第2拡散層5と、第2拡散層の上部に形成され、第2導電型である第3拡散層6と、第1拡散層の上部で且つ第2拡散層から間隔をおいて形成された第2導電型である第4拡散層8と、少なくとも第3拡散層の下に、第2拡散層と間隔をおき且つ下端部が第1拡散層の下端部よりも下に位置するように形成された第1導電型の第5拡散層2とを備えている。第3拡散層から第5拡散層までの最短距離と、第5拡散層から第4拡散層までの最短距離及び第1拡散層の下端部から第4拡散層までの最短距離のいずれか短い方の距離との和は、第3拡散層から第4拡散層までの最短距離よりも小さい。

(もっと読む)

ESD保護回路及び半導体装置

【課題】信号電圧が電源電圧を正負両方向に越えるようなチップ端子に対し適切に動作するESD保護回路を提供する。

【解決手段】ESD保護回路は、端子に一端のP側が接続されグラウンドに他端のN側が接続されるPNPN接合と、グラウンドにP側が接続されるPN接合のN側にソース及びゲートが接続され、前記の端子にドレインが接続されるPMOSトランジスタとを含む。

(もっと読む)

半導体集積回路装置

【課題】電極パッドからESD保護回路に十分なサージ電流が流れず、入出力回路が破壊されやすくなる。

【解決手段】半導体集積回路装置201の回路ブロック21の上層に、電極パッド22が設けられている。電極パッド202,213と、内部回路208およびESD保護回路206との間の接続配線に、分岐点A204,分岐点B212が設けられている。分岐点A204,分岐点B212は、電極パッド202,213よりもESD保護回路206に近い位置に、配置されている。

(もっと読む)

保護素子及び半導体装置

【課題】半導体素子を保護する保護素子を備え、静電破壊が抑制され、信頼性の高い半導体装置を提供する。

【解決手段】半導体装置1は、チャネル層105とキャップ層112とを含む半導体積層体113と、半導体積層体113上に形成された下部電極213と上部電極216とを有する少なくとも1つの半導体素子1Xと、半導体素子1Xと共通の半導体積層体113を有し、半導体素子1Xを保護する少なくとも1つの保護素子1Yとを備えたものである。保護素子1Yは、キャップ層112を厚み方向に貫通するリセス部221と、リセス部221の底面221Bから半導体積層体113内に厚み方向に形成された絶縁領域218Yと、リセス部221を挟んで両側に形成されたキャップ層112に接続された一対のオーミック電極219、220とを備えたものである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】アンテナ効果によるゲート酸化膜の破壊等を防止するとともに、半導体装置の動作の遅延を抑制すること。

【解決手段】本発明の一態様に係る半導体装置は、前段出力トランジスタA1に金属配線A2aを介して接続された入力トランジスタゲート電極A9を有する入力トランジスタA3と、入力トランジスタゲート電極A9に抵抗素子A4を介して接続されたダミートランジスタA5を備える。抵抗素子A4は、入力トランジスタA3の後段に設けられ、金属配線A2aに接続されている。抵抗素子A4とダミートランジスタA5は、金属配線A2bを介して接続されている。

(もっと読む)

半導体装置

【課題】温度検出素子の温度検出素子の静電破壊に対する耐性の向上と、測定精度の向上させることができる半導体装置を提供すること

【解決手段】半導体装置100は、温度検出素子10と、一方の端子が温度検出素子10の電流入力端子に接続される抵抗器11とをそれぞれが備え、互いに並列に接続される複数の温度検出素子列12とを備える。また、複数の温度検出素子列12の抵抗器11の他方の端子が接続される第1の外部端子14を備える。

(もっと読む)

半導体保護装置

【課題】

抵抗とダイオードを同一n型不純物領域で形成した半導体保護装置において、半導体保護装置のEMIフィルタ特性を維持してパッド部を離間する場合には抵抗Rの幅Wを広くし、パッド部下方のpn接合容量を小さくする必要がある。この場合、パッド部下方のpn接合容量小さくなることによりESD耐量が劣化する問題があった。

【解決手段】

半導体保護装置の抵抗となるn型不純物領域とダイオードとなるn型不純物領域を離間し、抵抗となるn型不純物領域の面積をEMIフィルタ特性において必要な最小限の面積とすることで、ダイオードとなるn型不純物領域の総面積を最大限に確保できる。これによりESD耐量を従来より向上しつつパッド部間を離間できる。

さらに半導体保護装置の抵抗となるn型不純物領域両端の面積を抵抗の幅より拡大し、これと離間して抵抗となるn型不純物領域両端と同等の面積の他のn型不純物領域を設けてダイオードとすることで、ESD耐量の向上が実現する。

(もっと読む)

ESD保護素子

【課題】ESD耐量を向上させたESD保護素子を提供する。

【解決手段】本発明によるESD保護素子は、バイポーラトランジスタを用いたESD保護素子である。バイポーラトランジスタは、第1端子(Pad)に接続されるコレクタ拡散層7とエミッタ端子とを備えるバイポーラトランジスタと、第2端子(GND)からエミッタ拡散層4を介してコレクタ拡散層7に至る複数の電流経路上のそれぞれに設けられた電流制御抵抗11とを具備する。

(もっと読む)

半導体集積回路

【課題】寄生容量が小さく、かつ、信号波形の歪み発生を防止または抑制した保護素子をIC内に実現する。

【解決手段】内部回路2と、その保護素子3とを同一半導体基板に有する。保護素子3は、アノード同士が共通接続されて浮遊ノードを形成した2つのダイオードD1,D2を有し、これがウェル・イン・ウェル構造に形成されている。このウェル・イン・ウェル構造は、浮遊ゲートを形成するP型ウェルと、P型ウェルを包含し、一方のダイオードのカソードと同電位のN型ウェルと、P型ウェル内に形成された、他方のダイオードのカソードと同電位の第1のN型領域と、を有して構成されている。

(もっと読む)

半導体装置

【課題】薄膜SOI領域を有する基板において、基板に第1半導体素子10と異なる第2半導体素子30、40を形成した際に、この第2半導体素子30、40の特性を従来の半導体装置より向上させることができる半導体装置を提供する。

【解決手段】基板のうち第1半導体素子10が形成される第1半導体素子形成領域1とは異なる部分を第2半導体素子形成領域2とし、第2半導体素子形成領域2に、基板の表裏を貫通する第1貫通トレンチ31を形成し、第1貫通トレンチ31の側壁に絶縁膜32を形成すると共に第1貫通トレンチ31の内部に第1埋込材料33を埋め込む。そして、第1埋込材料33を有する第2半導体素子30、40を形成して半導体装置を構成する。

(もっと読む)

半導体装置

【課題】集積回路の高性能化、小型化を妨げることなく、集積回路のESD(静電気放電)に対する耐性を向上する。

【解決手段】2つの入出力端子の間に保護回路104が挿入されている。ESDが発生したとき、保護回路によって2つの入出力端子を短絡して、回路103に過電圧が印加されることを防ぐ。回路は、接続配線110,120を介して、入出力端子に電気的に接続されている。回路は、接続配線との複数の電気的な接続部を有しており、各接続部と入出力端子間の配線抵抗が等しくなるように、接続配線を形成する。これにより、ESDが発生しても、1つの接続部に電圧が集中して印加することが回避されるため、ESDによって回路が破壊される確率が低減される。

(もっと読む)

半導体装置

【課題】素子が破壊されるような過電圧が供給された場合に、実動作を阻害することなく素子を保護することを課題の一とする。

【解決手段】第1の電位供給端子100と、第2の電位供給端子101と、第1の電位供給端子100及び第2の電位供給端子101に電気的に接続された分圧回路102、制御回路103、及びバイパス回路106を有する保護回路107と、保護回路107を介して第1の電位供給端子100及び第2の電位供給端子101に電気的に接続された機能回路108と、を有する構成とする。

(もっと読む)

半導体装置

【課題】保護回路を有する半導体装置において、保護回路の面積を小さくする。

【解決手段】第1導電型のウェル10、ウェル10に形成された複数の第1の拡散層200、ウェル10に形成された複数の第2の拡散層300、及びウェル10に形成された拡散抵抗層400を有する。第1の拡散層200は、第2導電型であり、半導体装置の入出力端子に互いに並列に接続している。第2の拡散層300は、複数の第1の拡散層200と互い違いに配置されており、電源又はグラウンドに接続されている。拡散抵抗層400は、第2導電型であり、複数の第2の拡散層300のいずれかの隣に位置している。拡散抵抗層400は、半導体装置の入出力端子に対して第1の拡散層200と並列に接続しており、かつ半導体装置の内部回路と入出力端子を接続する。

(もっと読む)

半導体装置

【課題】 厳格な耐圧性を要求されず、且つ過電圧印加時においてもサージ電流による破壊が生じにくい半導体装置を提供する。

【解決手段】 高濃度P型のコンタクト領域17及び18の間に係るP型の第1不純物拡散領域13によってP型の半導体基板11の基板面に平行な方向に抵抗を構成し、第1不純物拡散領域13とNウェル12の間、及びNウェル12と半導体基板11の間において夫々異なる整流方向のダイオードを半導体基板11の基板面に垂直な方向に構成し、第1不純物拡散領域13とNウェル12若しくはウェル12より高濃度N型の第2不純物拡散領域14の間、並びに、Nウェル12若しくは第2不純物拡散領域14と基板より高濃度P型の第3不純物拡散領域21の間において、夫々異なる整流方向のダイオードを半導体基板11の基板面に平行な方向に構成する。

(もっと読む)

半導体装置

【課題】 保護対象回路を静電気放電から保護するために保護対象回路に接続されている保護素子を備えている半導体装置において、保護素子の厚みを増やすことなく保護素子の素子面積を低減でき、かつESD信号の印加部とゲート電極の間の抵抗値を容易に調整することができる保護素子を備えている半導体装置を提供する。

【解決手段】 半導体装置100は、保護対象回路12とパッド10と保護素子90を備えている。保護素子90には、第1ドレイン電極14とソース電極2と第2ドレイン電極6とゲート電極4と素子分離トレンチ18が形成されている。ドレイン電極14、6と素子分離トレンチ18の間はアルミ配線8で接続されている。パッド10から第1ドレイン電極14にESD信号が印加されると、第1ドレイン電極14から素子分離トレンチ18を経由して第2ドレイン電極6にESD電流が流れる。

(もっと読む)

1 - 20 / 50

[ Back to top ]