Fターム[5F064DD08]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 素子、セル、ブロックの大きさ (500) | 拡大、縮小 (77)

Fターム[5F064DD08]に分類される特許

1 - 20 / 77

原版データの生成方法、原版作成方法、原版データを作成するためのプログラム及び処理装置

【課題】 微細なパターンを精度よく形成する原版のデータを生成する生成方法を提供する。

【解決手段】 光源からの光を用いて原版を照明する照明光学系と、前記原版のパターンを基板に投影する投影光学系とを備える露光装置に用いられる原版のデータをコンピュータによって生成する生成方法であって、近似空中像に基づいて主パターンを決定し、補助パターンを挿入することで原版のデータを生成する生成方法を提供する。

(もっと読む)

パターン作成方法および半導体装置の製造方法

【課題】高歩留まり且つ低コストで半導体装置を製造することができるパターン作成方法を提供すること。

【解決手段】実施形態によれば、パターン作成方法が提供される。パターン作成方法では、設計パターンに応じた基板上パターンを形成できるよう前記基板上パターンに応じたマスクパターンを作成する際に、前記設計パターン間が満たす必要のある相対関係に基づいて、前記設計パターン間に対応するマスクパターン間が前記相対関係を満たすよう前記マスクパターンを作成する。

(もっと読む)

ランダム・アクセス電気的プログラム可能なEヒューズROM

【課題】ランダム・アクセス電気的プログラム可能なeヒューズROMを提供する。

【解決手段】1回プログラム可能な読み出し専用メモリ(OTPROM)が、アグレッシブにスケール縮小された、シリサイド移動可能なeヒューズの2次元配列において実施される。ワード・ライン選択は、VDDにおいて動作するデコード論理によって実施され、一方ビット・ライン・ドライブは、VDDとプログラミングのためのより高い電圧VPとの間でスイッチ切替えされる。OTPROMは、それゆえコストを加算することなしに他の技術と適合可能で、統合することができ、そして、ヒューズ・プログラミングの間、電圧降下を最小にする高電流経路の最適化をサポートする。プログラム可能参照を有する差動センス増幅器は、センス・マージンを改善するために使用され、個々のヒューズに設けられるセンス増幅器の代りに、ビット・ライン全体をサポートすることができる。

(もっと読む)

半導体装置のレイアウト検証方法と装置及びプログラム

【課題】Diffusionラウンディングの影響を防ぐためにトランジスタの特性変動量を定量的に考慮した最適な設計基準に基づく設計の検証を可能とする方法の提供。

【解決手段】拡散層1において第1の辺3と第2の辺4で確定されるコーナー部に形成されるDiffusionラウンディング5の形状を数式で表現し、コーナー部に隣接するゲート幅WのトランジスタTrに関して、第2の辺とゲートの間隔をX1とし、Diffusionラウンディングによるゲート幅の誤差をΔWとし、Diffusionラウンディングの形状パラメータとΔWとX1の関係と、トランジスタTrの特性変動率とゲート幅の変動率の関係とから、第2の辺とゲートの間隔X1の設計基準値を導出し、レイアウト情報からコーナー部に隣接して配設されるトランジスタのゲートと第2の辺の間隔を抽出し、抽出したゲートと第2の辺の間隔が、基準値を満たすか否か判定する。

(もっと読む)

集積回路の製造、設計方法、およびプログラム

【課題】消費電力の増加をできるだけ抑えながら、回路の動作速度を向上させる。

【解決手段】本製造方法では、対象経路上のトランジスタの設計パターン形状の少なくとも一部を特徴づけるパラメータの値により閾値を算出し、算出された閾値と目標閾値との差を算出し、トランジスタの閾値とゲート長との関数関係にしたがって、閾値と目標閾値との差に対応するゲート長の変更量を算出し、対象経路上のトランジスタのゲート長を変更量だけ縮小し、ゲート長が縮小されたトランジスタを含む回路の設計情報から回路が製造される。

(もっと読む)

半導体装置の設計方法および、これに用いる標準セル

【課題】配線性の向上とレイアウトサイズの縮小を図る。

【解決手段】標準セル1は、長方形の領域を持つセルであり、論理回路用の入力端子6と出力端子7が存在する信号配線領域3と、信号配線領域3を挟んで標準セル1の長手方向の両側にそれぞれ位置し、論理回路用の電源端子8が信号配線領域3から延びて内在する電源配線領域2とからなる。各々の電源配線領域2は、標準セル1の長手方向の両端側に位置する電源端子8の一部を除去可能な領域9を含む。複数の標準セル1を縦および横方向に隣接させて列状に並べると、隣接する2つの電源配線領域2をセル長手方向にて合わせた範囲X内で電源配線10が移動可能である。電源配線10の位置に応じて領域9を取り除いて、電源端子8の長さを変更可能である。標準セル1の長手方向における信号配線領域3の範囲Yは、信号配線の混雑予測に応じて拡縮可能である。

(もっと読む)

応力発生膜を含む半導体装置の製造方法、および設計方法

【課題】応力発生膜の形状に依存して、半導体装置製造時の半導体装置の回路部品の特性がマクロセル設計段階での半導体装置の回路部品の特性から変動することを極力抑制する。

【解決手段】応力発生膜の延在方向の寸法の変更量に対する、半導体装置の特性の変化量が所定の限度で飽和する延在方向の寸法を目標延在寸法として設定する工程と、半導体装置内で応力発生膜の末端からゲートに至るまでの寸法が少なくとも目標延在寸法となるように応力発生膜を形成する工程とを含む。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法

【課題】I/Oバッファ変更があった場合であっても、リワーク性を有する半導体集積回路を提供する。

【解決手段】半導体集積回路(7)のチップの外周部に沿って形成されたI/O配置領域(2)と、その外周部の内側に形成されたプリミティブブロック配置領域(3)とを具備する半導体集積回路(2)を構成する。その半導体集積回路(7)は、そのプリミティブブロック配置領域(3)は、容量セルの配置を許容する許容領域(3)と、そのI/O配置領域(2)に沿って形成され、その容量セルの配置が禁止された禁止領域(11)とを含む。

(もっと読む)

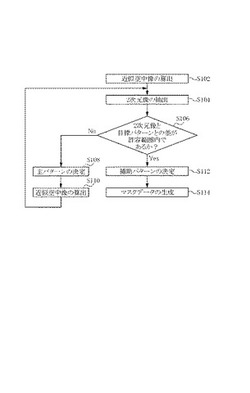

半導体デバイスパターン検証方法およびその検証プログラム

【課題】計算負荷を低減でき、計算時間を低減できる半導体デバイスパターン検証方法および検証プログラムを提供する。

【解決手段】半導体デバイスパターン検証方法は、マスクパターンを算出する第1工程<ST11>、半導体基板上に形成されるフォトレジストの形状を算出する第2工程<ST12>、図形演算処理を用いて一律リサイズを行い、擬似的な仮加工形状に限定して算出する第3工程<ST13>、設計パターンが前記半導体基板上に形成されるか否かについて図形検証を行い、危険箇所候補を検出する第4工程<ST14>、危険箇所候補の加工シミュレーションを行い、部分加工形状を算出する第5工程<ST15>を具備する。

(もっと読む)

半導体装置

【課題】半導体装置の微細化を犠牲とすることなく、ビアの冗長性を向上させ、歩留まりが高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板の上に形成された第1の配線211aと、第1の配線211aよりも上層に形成された第3の配線231aと、第1の配線211aと第3の配線231aとを接続する第1のビア221aとを備えている。第1のビア221aの形成位置と第3の配線231aの端部との間隔t1は、第2の配線と第2の配線よりも上層の第4の配線とを接続する第2のビアの形成位置と第4の配線の端部との間隔よりも小さい。第1のビア221aの半導体基板と平行な方向の断面積は、第2のビアの半導体基板と平行な方向の断面積よりも大きい。

(もっと読む)

半導体集積回路の設計方法、設計支援プログラム、設計支援装置

【課題】レイアウト変更に有効利用できる空き領域を効率的に確保する。

【解決手段】本発明による半導体集積回路の設計方法は、事前に設計されたレイアウトパタンデータから縮小対象の第1セルを選択するステップと、第1セルに隣接する空き領域の面積を算出するステップと、空き領域の面積に応じて選択された一辺を固定し、前記一辺に対向する他の辺を変動させて前記第1セルを縮小するステップとを具備する。

(もっと読む)

設計方法、露光用マスク、設計装置

【課題】疑似エラーの発生を抑制する。

【解決手段】設計装置は、設計データ21に含まれる回路パターンの光学的近接効果に対するアウターセリフパターンとインナーセリフパターンを生成し、それらを含む中間データ23を描画データ24に変換する。設計装置は、アウターセリフパターン,インナーセリフパターンを回路パターンと分離して配置した。そして、設計装置は、アウターセリフパターン,インナーセリフパターンを描画データ24から除去したチェック用描画データ26を生成し、そのチェック用描画データ26に含まれる描画用パターンの形状を検証ルールに従って検証する。

(もっと読む)

半導体集積回路

【課題】入力回路または出力回路を介して電源配線にサージ電圧が印加された場合においても、素子面積の増大を抑制しつつ、内部回路を静電破壊から安定的に保護する。

【解決手段】入出力セル3c〜3fの間の隙間に電源保護素子6a〜6dをそれぞれ配置し、電源保護素子6a〜6dとして、電源配線7、8間に接続されたダイオードストリングS2〜S5をそれぞれ用いる。

(もっと読む)

半導体装置の設計方法

【課題】TATを短縮すること。

【解決手段】本発明では、チップレイアウトデータ(22)に含まれる複数のゲートのうちの、アンテナ違反であるアンテナ違反ゲート群を表すアンテナ違反情報(20)をエラー残箇所ライブラリ(16)に格納する。チップレイアウトデータ(22)に対してリソグラフィシミュレーションを実施し、フォトレジスト露光後の予想レイアウトデータ(23)を生成する。エラー残箇所ライブラリ(16)を参照して、予想レイアウトデータ(23)に含まれる複数のゲートのうちの、アンテナ違反情報(20)が表すアンテナ違反ゲート群を選択する。アンテナ違反ゲート群の各々の面積に対して、そのアンテナ違反ゲート群に接続される配線の面積との比を示す算出値を算出する。その算出値が第1設定値から第2設定値の範囲である場合、アンテナ違反ゲート群の大きさを調整する。

(もっと読む)

回路設計支援方法、回路設計支援装置および回路設計支援プログラム

【課題】回路全体の動作速度に影響を与えない範囲でのセル最適化を支援すること。

【解決手段】半導体集積回路内のパスの遅延分布から、半導体集積回路全体の動作タイミングに影響を与えることのないパスの動作遅延の上限値を上限パスディレイとして求める。上限パスディレイを用い、セルサイズの変更が半導体集積回路全体の動作タイミングに影響を与える可能性のあるクリティカルパスを求める。クリティカルパス上に含まれるセルのセルサイズを小さくしないこと、およびクリティカルパス上に含まれないセルのセルサイズを小さくする場合には当該セルを含むパスの遅延が上限パスディレイを超えないことをセルサイズ最適化の制約条件とする。

(もっと読む)

半導体装置

【課題】誤動作を抑制しつつセルサイズを小さくしたフリップフロップ回路を備える、半導体装置を提供する。

【解決手段】CMOS半導体集積回路内に構成されたフリップフロップ回路を備える半導体装置であって、前記フリップフロップ回路は、少なくとも、第1のクロック信号を生成する、第1のクロック生成インバーターと、前記第1のクロック信号を反転させた第2のクロック信号を生成する、第2のクロック生成インバーターと、を備え、前記第1及び第2のクロック生成インバーターは、前記フリップフロップ回路のマスターラッチ部とスレーブラッチ部とから構成されるラッチ部を挟むように配置され、前記第1のクロック生成インバーターと、前記第1のクロック生成インバーターに隣り合う前記フリップフロップ回路内の第1の他の回路とは、ソース領域を共有し、前記第2のクロック生成インバーターと、前記第2のクロック生成インバーターに隣り合う前記フリップフロップ回路内の第2の他の回路とは、ソース領域を共有する。

(もっと読む)

アップサンプリング装置及びダウンサンプリング装置

【課題】レイアウトデータの階層構造を有効に利用して、精度を高く維持しつつ処理の能率を高めることのできるアップサンプリング装置、ダウンサンプリング装置を提供する。

【解決手段】アップサンプリング部44は、メッシュ付加部441および新メッシュデータ設定部442を備えている。メッシュ付加部441は、空間フィルタ部423から入力される画像データに新たなメッシュを付加する。新メッシュデータ設定部442は、付加されたメッシュ上の画像データにゼロの値を設定し、メッシュが付加される前の画像データとともに、逆フーリエ変換部424へ出力する。

(もっと読む)

半導体装置の設計検証装置

【課題】隣接するビアの配線長又は配線面積を抽出し、これに基づく検証を可能とする半導体装置の設計検証装置を提供する。

【解決手段】ビアが配置された配線レイアウトデータにおいて、ビアの大きさを大きくしたOversize領域を求め、Oversize領域によって分割される配線部をWireとする。Oversize領域内において、ビアの元の大きさの形状からOversize領域の所定のエッジまでの距離が所定値以下の領域をCrossとする。残りのOversize領域内の領域をHaloとする。1つのCrossに対し、これに接続したWireとHaloの総合の面積、あるいは、Wireの面積に対するCrossの数が所定値以上の場合に、不適切なビアの配置であると判断する。

(もっと読む)

半導体装置のレイアウト設計装置、方法及びプログラム

【課題】電源分離処理を行うと、チップサイズが増大する課題があった。

【解決手段】セルデータ格納部と、分離処理部とを具備する半導体装置のレイアウト設計装置によって解決できる。セルデータ格納部は、複数のセルが隣接して連続する構造を有する半導体装置における各セルのセルデータを格納する。分離処理部は、セルデータを処理し、複数のセルに亘って設けられるメタル配線を、半導体装置の設計基準に従って、セル間で分離する。分離処理部は、延伸・短縮部と、反転部とを備える。延伸・短縮部は、セルデータのそれぞれについて、メタル配線の一部であって、各セルのセル枠内に配置されるべきメタル部分の一端を延伸すると共に、他端を、一端を延伸した方向と同じ方向に短縮する。反転部は、延伸・短縮部によって、延伸され及び短縮されたメタル部分を有する任意のセルを、延伸された一端と、短縮された他端とが入れ替わるように、ミラー反転する。

(もっと読む)

電子デバイスをソース技術からターゲット技術に移行する方法及びコンピュータ・プログラム(電流モード動作電子デバイスをターゲット技術に移行する方法)

【課題】アナログ/ミックスド・シグナル電子回路をソース技術からターゲット技術に移行する有用な方法を提供する。

【解決手段】まず、ソース技術電子回路内の電流モード動作デバイス及びそれらの電圧調整ノードが識別される。電流モード動作デバイスはそれ自体の電圧調整ノードに印加される電圧に対する感度が低いため、回路内の他のデバイスのバイアス条件に干渉することなく、電圧調整ノードの電圧を変更して電流モード・デバイスの性能を高めることが可能となる。これにより、回路設計者は、電流モードで動作する電子デバイスをソース技術からターゲット技術に移行する際に使用可能な2つの自由度(典型的には幅及び長さ)を余すところなく利用することが可能となる。

(もっと読む)

1 - 20 / 77

[ Back to top ]