Fターム[5F064DD22]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 素子、セル、ブロックの配列、ピッチ (599) | セルしきつめ型 (44)

Fターム[5F064DD22]に分類される特許

1 - 20 / 44

半導体装置

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

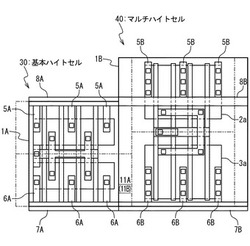

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

半導体装置

【課題】RDRに従い設計され、活性領域と電源配線との境界部や周辺部における不具合の発生が抑制された、小型化かつ高集積化された半導体装置を提供する。

【解決手段】少なくとも1つのスタンダードセル内における半導体基板SBの主表面に形成される第1導電型の機能素子用不純物領域Apと、電源電位が印加される第2導電型の電源電位用不純物領域Anとを備える。半導体基板SBの主表面上に形成され、かつ半導体基板SBの主表面に達する貫通孔SCTHを有する絶縁層II1、II2と、絶縁層II1、II2の貫通孔内に形成されたコンタクト用導電層PCLとを備える。上記機能素子用不純物領域Apと電源電位用不純物領域Anとをまたぐように形成されるコンタクト用導電層PCLを通じて電気的に接続される。

(もっと読む)

半導体装置の設計方法、プログラム、及び設計支援装置

【課題】チップサイズの縮小を図ること。

【解決手段】設計支援装置は、作成したユニットセルに応じて、複数種類のバルクを配置した列(バルク領域)を設定し(ステップ22a)し、列にユニットセルを配置する(ステップ22b)。設計支援装置は、列におけるバルクの使用情報をバルクの周類毎に生成し、その使用情報に基づいてバルクの使用状況を検証する(ステップ22c)。そして、設計支援装置は、バルクの配置が均等ではない場合にユニットセルの配置を変更する。

(もっと読む)

半導体装置

【課題】電子回路の小型化を実現する。

【解決手段】MOSトランジスタ20が、格子状に形成されたゲート電極22と、ゲート電極22で囲まれたソース領域23およびドレイン領域24と、ゲート電極22の格子の一方向に沿って配置され、ソース領域23およびドレイン領域24とコンタクトを介して接続するソース用メタル配線27およびドレイン用メタル配線28を有する。ソース領域23およびドレイン領域24のそれぞれは、各メタル配線の長さ方向に長辺を有する長方形状に形成される。ソース用メタル配線27およびドレイン用メタル配線28は、その長さ方向にジグザグ形状に形成されて、それぞれソース用コンタクト25およびドレイン用コンタクト26に接続する。

(もっと読む)

処理ユニットと不揮発性メモリユニットとの組み合わせのアレイ

【解決手段】リコンフィギャラブルロジックデバイスは、配線ネットワークを介して相互に接続されたタイルのアレイを有する。各タイルは、揮発性メモリを有する処理ユニットと、ランダムアクセスメモリユニットとの両方を有する。 (もっと読む)

半導体集積回路

【課題】配線効率を悪くすることなく効率よくノイズを除去可能な半導体集積回路を提供する。

【解決手段】スタンダードセル10に論理回路領域10aと容量領域10bとを具備させ、同一の配線層に属する1本の電源配線22及び2本の接地配線20,21(または2本の電源配線及び1本の接地配線)をスタンダードセル10に接続し、容量領域10bにおいて、MOS容量17を同一の配線層の電源配線22と接地配線21との間に接続する。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、外部からの電源が供給される電源配線と回路毎に設けられる電源配線とを接続するスイッチトランジスタにより回路の配置に大きな制約が課される問題があった。

【解決手段】本発明にかかる半導体装置の一態様は、半導体基板1と、半導体基板1上に形成されるトランジスタ(セル)に電源を供給する第1の下層配線と、第1の下層配線層に接続され、第1の下層配線よりも電流許容量の大きい第1の中間層配線と、第1の中間層配線よりも上層に配置され、外部から入力される電源を受ける上層配線と、を有し、第1の中間層配線は、半導体基板1上に形成されたスイッチ回路SWを介して上層配線に接続されるものである。

(もっと読む)

集積回路装置のレイアウト方法、集積回路装置のレイアウトプログラム、集積回路装置のレイアウトシステム、集積回路装置及び電子機器

【課題】チップ面積の増加を伴わずに電源補強を実現することができる集積回路装置のレイアウト方法等を提供すること。

【解決手段】本発明の集積回路装置のレイアウト方法は、機能セルが配置されていない未配置領域を探索するステップ(ステップS12)と、未配置領域に、少なくとも一部が第1、第2のポリシリコン配線パターンによりそれぞれ形成された第1、第2の電源補強線を含む第1、第2の電源補強セルを配置するステップ(ステップS14)と、を含む。ステップS14において、第1、第2のポリシリコン配線パターンを第2、第1の電源供給線とそれぞれ交差させて、第2の方向に沿って、第1、第2の電源補強線を介してそれぞれ2つの第1の電源供給線及び2つの第2の電源供給線を接続する2つの配線パターンの少なくとも一方が形成されるように、少なくとも2つの第1、第2の電源補強セルの少なくとも一方を第2の方向に沿って並べて配置する。

(もっと読む)

集積回路装置のレイアウト方法、集積回路装置のレイアウトプログラム、集積回路装置のレイアウトシステム、集積回路装置及び電子機器

【課題】チップ面積の増加を伴わずに電源補強を実現することができる集積回路装置のレイアウト方法等を提供すること。

【解決手段】本発明の集積回路装置のレイアウト方法は、機能セルが配置されていない未配置領域を探索するステップ(ステップS14)と、未配置領域に、少なくとも一部が第1及び第2のポリシリコン配線パターンによりそれぞれ形成された第1及び第2の電源補強線と、を含む電源補強セルを配置するステップ(ステップS16)と、を含む。ステップS16において、第1及び第2のポリシリコン配線パターンを第2の電源供給線及び第1の電源供給線とそれぞれ交差させて、第2の方向に沿って、第1の電源補強線及び第2の電源補強線を介してそれぞれ2つの第1の電源供給線及び2つの第2の電源供給線を接続する2つの配線パターンの少なくとも一方が形成されるように、少なくとも2つの電源補強セルを第2の方向に沿って並べて配置する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路のチップ面積を低減する。

【解決手段】第1トランジスタ(Tr2)と、Y軸に沿って上記第1トランジスタに隣接配置された第2トランジスタ(Tr3)と、X軸に沿って上記第2トランジスタに隣接配置された第3トランジスタ(Tr6)とを含む。さらに、Y軸に沿って上記第3トランジスタに隣接配置されるとともに、X軸に沿って上記第1トランジスタに隣接配置された第4トランジスタ(Tr7)とを含む。上記第1乃至第4トランジスタは、互いにウェルが共通化され、上記第1トランジスタの出力信号と、上記第2トランジスタの出力信号とは互いに逆相とされる。上記第2トランジスタの出力信号と、上記第3トランジスタの出力信号とは互いに逆相とされる。上記第3トランジスタの出力信号と、上記第4トランジスタの出力信号とは互いに逆相とされる。上記トランジスタの出力は、ウェルの電位変動を互いに打ち消すように作用する。

(もっと読む)

セルデータの検証装置、方法、およびプログラム

【課題】個々のセルデータ自体の自動配線への適合性を評価する。

【解決手段】電子装置の他の部分と配線によって接続され、前記電子装置の機能を実現するセルを定義するセルデータの検証装置である。本検証装置は、セルを電子装置の他の部分と接続する端子の定義を含むセルデータを入力する手段と、セルデータの電子装置内での配置を模擬した検証用の配置情報を入力する手段と、配置情報で配置されるセルの端子と接続されるべき相手端子の定義データを生成する手段と、セルデータを配置情報にしたがって配置するとともに、相手端子の定義データを付加したレイアウトデータを作成するレイアウト手段と、自動配線システムにセルデータとレイアウトデータとを入力することによって相手端子から配置されたセルの端子に至る配線データを発生させる、自動配線を起動する手段と、自動配線システムからの自動配線の結果を報知する報知手段とを備える。

(もっと読む)

半導体集積回路

【課題】電源ノイズを抑制する。

【解決手段】電源電圧Vddまたは基準電圧Vssが印加される主配線(第1基準電圧幹線VSS1)と、複数の副配線(基準電圧枝線VSSB)と、複数の基準電圧枝線VSSBに接続されている複数の回路セル(不図示)と、入力される制御信号に応じて、複数の基準電圧枝線VSSBのうち、所定の回路セルが接続されている基準電圧枝線VSSBと第1基準電圧幹線VSS1との接続および遮断を制御する電源スイッチセルSW1,SW2,…と、複数の基準電圧枝線VSSBを相互に接続する補助配線50と、を有する。

(もっと読む)

半導体集積回路装置の設計プログラム、半導体集積回路装置の設計支援システム、半導体集積回路装置の設計方法、半導体集積回路装置及び電子機器

【課題】クリティカルな信号等の所定の信号の配線長に着目して配線レイアウトを早い段階で変更することにより、信頼性の高い半導体集積回路装置を短期間で設計するための設計支援プログラム等を提供すること。

【解決手段】本発明の半導体集積回路装置の設計支援プログラムは、配置配線の対象となる回路に含まれるセルを配置するセル配置手段12と、配置配線の対象となる回路に含まれるネットを配線するネット配線手段14と、配置配線後のレイアウトに基づいて、前記ネットの配線レイアウトを変更する配線レイアウト変更手段16としてコンピュータを機能させる。ネット配線手段14は、所定のネットの配線を他のネットの配線よりも優先して行う。配線レイアウト変更手段16は、前記所定のネットの配線長を計算し、配線長が所定の規格値よりも大きい場合には、前記所定のネットの配線レイアウトを変更する。

(もっと読む)

半導体集積回路のレイアウト方法、レイアウトプログラム、及びレイアウト装置

【課題】半導体集積回路においてゲートのデータ密度に起因するトランジスタの特性バラツキを抑制する。

【解決手段】本発明による半導体集積回路の自動レイアウト装置10は、セルをゲート方向に隣接して配置する際、セルの境界付近に配置済みのゲートを基準ゲート111とし、その周辺の所定の領域内に存在するゲート数を規定の範囲内とするように、配置するセルを決定する。

(もっと読む)

半導体集積回路およびその設計方法

【課題】半導体集積回路置において、クロック回路の電源と、論理回路の電源とを分離しても、設計工数の増加や回路面積のオーバーヘッドを生じないようにする。

【解決手段】開示される半導体集積回路は、スタンダードセルの構造を有するクロック回路35と論理回路34とを第1の層上に同方向に形成された列上に配置し、クロック回路にクロック電源33を供給するクロック電源用電源38と論理回路に論理回路電源31を供給する論理回路電源用電源39とを第2の層上にクロック回路と論理回路の列と直交方向に形成された列上に配置してなるLSIに搭載された半導体集積回路であって、論理回路が論理回路電源の列とグランドGND32の列とにわたって置かれ、クロック回路がクロック電源とグランドGNDとにわたって置かれているとともに、クロック回路の電源にクロック電源が接続されている。

(もっと読む)

集積回路装置の設計方法、集積回路装置、及び集積回路の設計支援システム

【課題】設計が完成していない段階で精度のよい配置配線を行うことが可能な集積回路装置の設計方法、集積回路装置及び設計支援システムの提供すること。

【解決手段】ゲートアレイを少なくとも1部に含む集積回路の設計方法であって、当該集積回路に対応して選択するバルクのセル数または当該集積回路の完成時の予定セル数と、集積回路の回路設計における所定の段階において判明している設計データを実現するための論理回路を構成するセル数に基づき、前記所定段階で判明している論理回路の少なくとも一部に仮配置するセルの総数である仮配置セル数を求める仮配置セル数取得ステップと、前記所定段階で判明している少なくとも一部の論理回路に、所定の規則に従ってまたはランダムに仮配置セル数分のセルを配分する配分ステップと、含むことを特徴とする。

(もっと読む)

半導体集積回路の自動遅延調整方法

【課題】マニュアルによる方法に比べて、汎用性に優れていること。

【解決手段】コンピュータ1は、レイアウトデータ7にダミー配線50−Jを追加する処理(S2)と、レイアウトデータ7中でタイミング違反であるセル30−1とセル30−2間の対象配線40にダミー配線50−Jを接続する処理(S4)とを実行する。処理(S4)において、コンピュータ1は、ダミー配線50−Jを、ダミー配線50−Jの両端部に対応するピン61、62を有するダミー配線セル60に置き換え(S12)、対象配線40を切断して、対象配線41、42を生成し(S13)、対象配線41、42をピン61、62にそれぞれ接続し(S14〜S16)、ダミー配線セル60をダミー配線50−Jに置き換えて、対象配線40の切断部分にダミー配線50−Jが接続された配線とする(S17)。

(もっと読む)

1 - 20 / 44

[ Back to top ]