Fターム[5F064EE57]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 仮配線 (186)

Fターム[5F064EE57]に分類される特許

1 - 20 / 186

半導体装置の設計方法及び半導体装置の製造方法

【課題】半導体装置の歩留まりが低下することを抑制する。

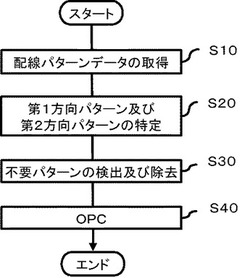

【解決手段】配線パターンを示す配線パターンデータを取得する(ステップS10)。次いで、配線パターンデータを解析して、第1方向パターン及び第2方向パターンを特定する(ステップS20)。第1方向パターンは、第1の方向に延伸するパターンであり、第2方向パターンは、第1の方向に直交する方向に延伸するパターンである。次いで、第1方向パターと第2方向パターンの交点を検出する。そして、この交点から延伸するパターンのうち、ビア、コンタクト及び他のパターンのいずれにも接続していないパターンを不要パターンとして検出し、検出した不要パターンを除去する(ステップS30)。そしてその後、設計した配線パターンに対して光近接効果補正を行う(ステップS40)。

(もっと読む)

半導体設計装置、半導体設計方法及びプログラム

【課題】信号の重要度を考慮に入れたセルの自動配置を行うアルゴリズムは存在しない。従って、重要配線が不必要に長くなる場合がある。重要配線が長くなると、重要配線を伝達する信号を劣化させる原因となり得る。そのため、信号の重要度を考慮に入れたセルの自動配置を行うことで、重要度の高い信号の品質を維持する半導体装置を設計できる半導体設計装置、が望まれる。

【解決手段】半導体設計装置は、半導体装置に含まれる複数のセルを接続する複数の信号配線から、伝達する信号が重要であることを示す重要配線情報が付された重要配線と、複数の信号配線のそれぞれに接続されているセルの数を示すセル接続数と、を抽出する配線情報抽出部と、配線情報抽出部が抽出した重要配線及びセル接続数に応じて、複数のセルの配置を決定するセル自動配置部と、を備えている。

(もっと読む)

配線支援方法及び装置

【課題】配線すべき複数の信号線を、ユーザの指定する目的に従って適切にグループ化する。

【解決手段】配線すべき複数の信号線を複数のグループに分けるための方法は、ユーザから、複数の信号線のグループ化の条件の指定を受け付けるステップと、指定された、グループ化の条件と、データ格納部に格納されている、複数の信号線の始点端子群と終点端子群との配置パターンとに基づいて、複数の信号線のグループ化の処理を切り替えて実施する実施ステップとを含む。

(もっと読む)

半導体集積回路の設計装置、及び半導体集積回路の設計方法

【課題】チップサイズを縮小することができる、半導体集積回路の設計装置、及び半導体集積回路の設計方法を提供する

【解決手段】下位階層の機能ブロック4に配置された複数のセル間を接続する第一の配線を設計する下位階層配線設計部311と、上位階層の機能ブロック間を接続する第二の配線を設計する上位階層配線設計部312とを備えており、下位階層配線設計部311は、機能ブロック4を複数の小領域4aに分割し、小領域4aごとに機能ブロック4内配線に必要となる必要配線層数Lnを算出して、最下部の配線層から必要配線層数Ln枚の配線層を配線可能領域として同領域内に第一の配線を配置し、上位階層配線設計部312は、第一の配線における配線可能領域以外の機能ブロック4の配線層に第二の配線を配置する。

(もっと読む)

フロアプラン作成情報生成方法、フロアプラン作成情報生成プログラム、フロアプラン作成情報生成装置、フロアプラン最適化方法、フロアプラン最適化プログラム及びフロアプラン最適化装置。

【課題】フロアプラン設計におけるイタレーションを防ぎ、設計期間を短縮する。

【解決手段】複数の回路モジュールの接続情報を含むネットリストと、前記複数の回路モジュールにグループを設定するためのグループ設定情報と、を記憶部に記憶し、ネットリスト及びグループ設定情報に基づき、複数の回路モジュールにグループを設定し(S21)、設定されたグループ間におけるタイミング制約を満たす距離を算出し(S23)、算出されたグループ間の距離を含み、フロアプランを作成するためのフロアプラン作成情報を生成する(S25)。

(もっと読む)

半導体集積回路設計支援装置、半導体集積回路設計方法およびプログラム

【課題】レイアウト設計において、複数のI/Oバッファセルを2列以上に配列する場合、I/Oバッファ領域の近傍にリピータを挿入する領域を確保し、手戻りをできるだけ抑えることができる、半導体集積回路設計支援装置、半導体集積回路設計方法およびプログラムを提供する。

【解決手段】リピータを含まないフィルセル(FC)と、リピータを含むフィルセル(FCR)とが用いられる。フィルセル(FC)は、同列で互いに隣接したI/Oバッファセル(Bm=1、n、Bm=1、n+1など)間に配置される。なお、複数のI/Oバッファセルは、2列に配置されている。I/Oバッファセルからプリミティブセルまでの配線長に基づいて、すでに配置されているフィルセル(FC)が、リピータを含むフィルセル(FCR)に置換される。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラム

【課題】マクロの全端子で配線が引き出し可能かを判定できるレイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラムを提供する。

【解決手段】記憶部11は内部にマクロを含んだ多層回路の階層レイアウトの設計データを記憶する。チャネル数算出部13は設計データに基づいて、マクロの各端子から所定の配線層まで配線を引き出すために使用可能なチャネル数を端子毎に算出する。経路算出部15は算出したチャネル数の少ない端子から順に、端子から所定の配線層まで配線を引き出すための経路を算出する。経路判定部16はマクロの全ての端子について引き出し経路を算出できたか否かを判定する。

(もっと読む)

LSI設計方法,設計プログラムおよび設計装置

【課題】従来のLSI設計フローではクロックの遅延やスキューが無いことを前提とするため,クリティカルパスにてタイミングが仕様を満たさないことがSTA後に判明する。

【解決手段】ハードウェア記述ファイルと制約条件ファイルとから第1のクロックと第2のクロックのそれぞれのクロックツリーによる想定遅延値をそれぞれ生成し,第1のクロックと第2のクロックの想定遅延値をもとにしてクリティカルパスをデータベースへ登録するデータベース構築工程と,ハードウェア記述ファイルと制約条件ファイルについて論理合成を行うとともに,クリティカルパスをそれ以外のパスよりも優先して最適化し,ネットリストを生成する論理合成工程とを有するLSI設計方法。

(もっと読む)

半導体集積回路装置

【課題】チップ面積を増加させることなく、効率良くリーク電流を抑制することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は論理が同一のセルA−1,B−1,C−1を備えている。セルB−1はセルA−1よりセル幅W2が大きいが、MOSトランジスタのゲート長L1はセルA−1と等しい。セルC−1は、セルB−1とセル幅W2が等しいが、ゲート長L2が大きいMOSトランジスタを有しており、セルA−1,B−1と比べて回路遅延は遅くなるがリーク電流は小さくなる。このため例えば、空き領域に隣接したセルA−1をセルB−1に置き換え、タイミングに余裕があるパスにおけるセルB−1をセルC−1に置き換えることによって、チップ面積を増加させることなく、リーク電流を抑えることができる。

(もっと読む)

レイアウト設計方法及びレイアウト設計装置

【課題】チップ面積を小さくすることのできるレイアウト設計方法を提供する。

【解決手段】レイアウト設計方法は、所定のタイミング制約F1を満足させるように、セルを配置し、低抵抗配線が形成される第1配線層を使用してセル間のパスの接続配線を形成する処理(ステップS2〜S4)を有する。また、レイアウト設計方法は、タイミング制約F1を満足させたまま、パスの接続配線のうち、セル間に配置されるバッファ回路によって区切られる複数のステージ中の少なくとも一つのステージに対応する接続配線におけるレシーバ側からの一部を、第1配線層から該第1配線層よりも配線遅延が大きくなる第2配線層に置き換えて形成する配線置換処理(ステップS5)を有する。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップサイズを縮小する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、半導体集積回路のレイアウト設計を階層別に行う階層レイアウト設計における上位階層において、上位階層の下の階層で配置配線が行われる所定の機能を備えた階層ブロックが配置される領域であって、空きユニットセル配置領域3と階層ブロック用のユニットセル配置領域4とを含む階層ブロック配置領域2を、チップ領域1に設定し、チップ領域1における階層ブロック配置領域2を包囲する周辺領域5のユニットセル配置領域、および、階層ブロック配置領域2内の空きユニットセル配置領域3を用いて、配置配線を行う。

(もっと読む)

階層レイアウト設計装置、階層レイアウト設計方法およびプログラム

【課題】複数の下位階層ブロックに跨るセル同士を各下位階層ブロックに設けた端子を経由して相互に接続する場合に、セル間を結ぶ経路が迂回経路となること。

【解決手段】階層レイアウト設計装置は、第1の下位階層ブロックに含まれるセルから出力された信号を受信する出力端子を該セルの近傍に配置する出力端子配置部と、第2の下位階層ブロックに含まれる複数のセルへ前記出力端子から出力された信号を供給する入力端子を、該複数のセルを囲む最小の矩形領域の境界上であって、前記出力端子が配置された箇所からの距離が最短の箇所に配置する入力端子配置部と、を備えている。

(もっと読む)

マクロ用レイアウト検証装置及び検証方法

【課題】マクロのレイアウト情報に基づいて、当該マクロが使用されるLSIのレイアウト設計時に発生する可能性がある設計規則違反を予め検出する。

【解決手段】マクロ用レイアウト検証装置は、マクロの端子にビアコンタクトを配置したと仮定する手段と、ビアコンタクトとマクロ内レイアウトとの関係が設計規則に違反するか否かを判定する手段と、を具備する。

(もっと読む)

配線削減方法及び回路生成装置

【課題】モジュール間の配線を自動的に削減する。

【解決手段】モジュール11A及び11Bの間に接続された配線に関する情報を含む仮配置/仮配線情報33に基づき、モジュール11A及び11Bの間に接続された配線の本数を抽出し、抽出された配線の本数と、予め設定された、配線の本数に対する閾値を少なくとも含む閾値情報34とを比較し、比較の結果、配線の本数が閾値を超えた場合に、モジュール11A及び11Bのうち、送信側のモジュール11Aに、パラレル信号をシリアル信号に変換するパラレルシリアル変換回路13を挿入するとともに、受信側のモジュール11Bに、シリアル信号をパラレル信号に変換するシリアルパラレル変換回路14を挿入し、モジュール11A及び11Bの間の接続をパラレル接続からシリアル接続に変更する。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】半導体集積回路の遅延時間の変動を抑制すること。

【解決手段】回路設計支援装置1は、選択部1bと配置部1cとを有している。選択部1bは、設計対象の半導体集積回路モデルが備えるレジスタモデル2bにクロック信号を供給するクロック信号線の分岐点P1からレジスタモデル2bのクロック信号入力端子に至る第1の経路と、分岐点P1からレジスタモデル2bのデータ信号入力端子に至る第2の経路の、配線に関する物理パラメータの差分値に基づいて、物理パラメータが異なる配線負荷を有する複数の遅延回路モデルから遅延回路モデルBを選択する。配置部1cは、選択された遅延回路モデルBをデータ信号入力端子に接続されるデータ信号線に配置する。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】半導体集積回路のレイアウト設計において、幅が広い第1の配線と幅が狭い第2の配線との間に無駄なスペースが発生することによる配線性の悪さを改善する。

【解決手段】このレイアウト設計方法は、回路情報に基づいて、レイアウト領域において複数の横ラインと複数の縦ラインとが交差する格子点上に、複数の回路素子の接続点を配置するステップ(a)と、回路情報及び複数の回路素子の配置に基づいて、いずれかの横ライン又は縦ラインの位置を始点として、第1の方向に格子間隔よりも大きい所定の幅を有する第1の配線を配置するステップ(b)と、ステップ(b)において配置された第1の配線に第1の方向と反対の第2の方向において隣接する横ライン又は縦ライン上に、最小幅を有する第2の配線を配置するステップ(c)とを含む。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】配線の遅延特性のばらつきを抑制すること。

【解決手段】回路設計支援装置1は、設定部1aと生成部1bとを有している。設定部1aは、半導体集積回路モデル2の層2a、2bそれぞれに、積層方向および面方向に隣接するユニット3の配線方向が互いに異なる方向に配線が生成される複数の矩形のユニット3を設定する。生成部1bは、ユニット3の境界で異なる層のユニット3に跨る配線を生成する。

(もっと読む)

半導体集積回路の設計方法および半導体集積回路の設計プログラム

【課題】配線が混雑する領域であっても最適な配線をすることができる半導体集積回路の設計方法を提供することである。

【解決手段】本発明にかかる半導体集積回路の設計方法は、所定の単位領域に配置されたレイアウトセルの端子数を調査し、単位領域のうち前記レイアウトセルの端子数が所定の値よりも大きい単位領域において、端子が存在する配線トラックである端子存在トラックと端子が存在しない配線トラックである空トラックとに分類すると共に、当該端子存在トラックが所定数以上連続する箇所を調査し、端子存在トラックが所定数以上連続する箇所における端子の位置を移動する。

(もっと読む)

設計ライブラリデータベース

【課題】結晶化半導体薄膜に対して適正かつ効率的なフォトマスクの作成を可能にする。

【解決手段】1実施形態に係る設計ライブラリデータベースは、2次元的に区画して各々薄膜トランジスタのチャネル領域のサイズを超える複数の結晶粒規定領域が配置された結晶化半導体薄膜を用いる薄膜トランジスタ回路の設計ライブラリデータベースであって、各々のチャネル領域が単一の前記結晶粒規定領域内の固定位置に配置される2個以上の薄膜トランジスタおよび前記2個以上の薄膜トランジスタを相互接続する配線を含む様々な論理ゲート回路をそれぞれ表す複数のスタンダードセル、並びに前記様々な論理ゲート回路の様々な組み合わせをそれぞれ表す複数のマクロセルの少なくとも一方のセルのライブラリ、および前記複数の結晶粒規定領域が配置された結晶化アレイパターンのスタンダードセルのライブラリを含みハードディスクに登録される。

(もっと読む)

基板の配線設計方法及びプログラム

【課題】配線設計において、簡易的に配線混雑を回避することが可能な配線設計方法を提供することを目的とする。

【解決手段】複数の第1方向配線の配線層及び複数の第2方向配線の配線層を備える基板対して概略配線を行い、基板を複数のタイルに分割し、複数のタイルに対応するように、複数の第1方向配線の配線層及び複数の第2方向配線の配線層を分割して、複数の第1方向配線の部分配線領域と、複数の第2方向配線の部分配線領域と、を形成し、タイルにおける第1方向配線がオーバーフローしている場合には、このタイルに対応する第2方向配線の部分配線領域を、第1方向配線の部分配線領域に変更する。

(もっと読む)

1 - 20 / 186

[ Back to top ]