Fターム[5F064HH20]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | その他 (17)

Fターム[5F064HH20]に分類される特許

1 - 17 / 17

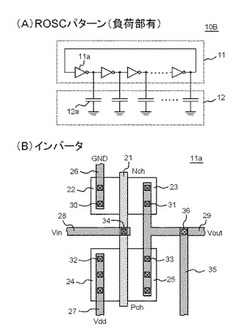

半導体装置、パラメータ最適化方法、及びプログラム

【課題】トランジスタの容量の各成分や配線容量を分離してパラメータを最適化することが可能な半導体装置、パラメータ最適化方法、及びプログラムを提供すること。

【解決手段】MOSトランジスタから構成されたプリミティブゲート回路11aを奇数段でリング状に結合した第1リングオシレータ部11の各前記プリミティブゲート回路の出力部と電気的に接続された負荷部12となる第1配線を有する配線負荷パターンと、第2リングオシレータ部の各プリミティブゲート回路の出力部が第2配線を介して負荷部となるMOSトランジスタのゲートに電気的に接続された複数のゲート負荷パターンと、第3リングオシレータ部の各プリミティブゲート回路の出力部が第3配線を介して負荷部となる拡散層に電気的に接続された複数の拡散層負荷パターンと、を備え、複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、複数の拡散層負荷パターンは、パターンごとに容量負荷が異なる。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

半導体集積回路の設計方法

【課題】設計期間の短縮が可能な半導体集積回路の設計方法を提供する。

【解決手段】本実施形態によれば、半導体集積回路の設計方法は、第1配線層、前記第1配線層上に設けられる第2配線層、及び前記第2配線層上に設けられる第3配線層を有する半導体集積回路の設計方法である。この方法は、前記第2配線層に、第1方向に沿って複数のスペア配線を配置し、前記第3配線層に、前記第1方向に直交する第2方向に沿って複数のスペア配線を配置する工程を備える。さらに、この方法は、前記スペア配線の配置後に、前記第1配線層に素子を配置する工程と、前記素子の配置後に、前記第1乃至第3配線層の少なくともいずれか1つに信号配線を配置する工程と、前記スペア配線を用いて、配線の設計変更を行う工程と、を備える。

(もっと読む)

回路シミュレータおよび半導体装置の設計方法

【課題】インパクトイオン化電流の算出精度を向上させる。

【解決手段】飽和ソース−ドレイン電圧Vdsatがソース−ゲート電圧Vgsおよびソース−ドレイン電圧Vdsの関数にて与えられたドレイン横方向電界Edの計算式に基づいて電界効果トランジスタのインパクトイオン化電流Iiiを計算する。

(もっと読む)

半導体集積回路

【課題】複数の相補トランジスタ対(CMOS対)を同相駆動するような回路を実現するためのスタンダードセルのスペース削減、コスト低減を図る。

【解決手段】所望の回路を形成するためのセルに相補対を同相駆動するタイプのスタンダードセルを含む。例えばダブルハイトの場合、CMOS対を複数(ここでは7対)含み、その少なくとも一部(ここでは7対とも)同相駆動される。このスタンダードセルは、CMOS対の1対分に対応した基本セル長のM(ここではM=2)倍のM倍セル長で、規格化されたセル長(縦)のサイズが規定されている。同相駆動される少なくとも2対分の共通ゲート電極21,22,23が規格セル長(縦)の方向に直線配置されている。

(もっと読む)

クロック配線方法

【課題】OCVがあっても、フリップフロップ間のデータ伝達に対するタイミングマージンの変動を少なくすることのできるクロック配線方法を提供する。

【解決手段】セル配置の終了したレイアウトデータにもとづいて、データパスを有するフリップフロップ間のデータ伝達のクロック信号に対するタイミングマージンを算出し、そのタイミングマージンの少ない順にフリップフロップを2個ずつ組み合わせてフリップフロップ対を生成する。その後、それぞれのフリップフロップ対のフリップフロップ間に部分的クロック配線を配線し、その部分的クロック配線上において、その接続先の2個のフリップフロップへの等遅延点を求め、その等遅延点を最終分岐点とするクロックツリーを生成する。

(もっと読む)

半導体素子の漏洩電流予測方法

【課題】 半導体素子の漏洩電流予測方法を提供する。

【解決手段】 半導体素子の漏洩電流予測方法において、多数のセルを有するチップを多数の分割領域に区分して、各セルで漏洩電流を引き起こす工程変数相互間の空間相関を決める。多数の漏洩成分に関する実際漏洩特性関数を算術的に合算して、上記多数の漏洩成分と物理的に等価の仮想セル漏洩特性関数を生成する。分割領域内の各セルに対する仮想セル漏洩特性関数を算術的に合算して、上記分割領域で発生する漏洩電流に関する特性関数の領域漏洩特性関数を生成する。領域漏洩特性関数を統計的に合算して、全チップで発生する漏洩電流に関する特性関数の全チップ漏洩特性関数を生成する。これにより、全チップ漏洩特性関数を獲得するためのウィルキンソンアルゴリズムの複雑度を減らすことができる。

(もっと読む)

入力容量抽出方法、セルライブラリ、セルライブラリの生成方法および配置配線方法

【課題】実デバイスに近い入力容量を抽出する。

【解決手段】半導体集積回路の基本セルと、半導体集積回路の入力端子部周辺に配置される複数種のセル外パターンと、セル外パターンから算出されるセル外入力容量と、を備えるセルライブラリ13が生成され、半導体集積回路のレイアウトデータ11に、セルライブラリ13から、入力端子部周辺に配置されたパターンとして適切なセル外パターンが付加され、セルスワップレイアウトデータ14が生成され、セルスワップレイアウトデータ14から、セルライブラリ13を参照して、セル外パターンに対応するセル外入力容量が抽出されるようになる。

(もっと読む)

スペアセル用のセルデータ、半導体集積回路の設計方法及び半導体集積回路。

【課題】セルベース設計において、スペアセルを使用した回路の修正を行なう際に、可及的に配線長を短くしつつ、修正により影響される配線層数を減らす。

【解決手段】スペアセルの信号入力端子および信号出力端子の形状を表現するマスクパターンデータを、第2配線層以上の配線層のマスクパターンデータとする。この解決手段により、マスク製造のやり直しを最小限に抑えつつ、スペアセルに接続される配線の長さを可及的に短くすることができる。

(もっと読む)

ダミーパターンの配置方法、半導体設計装置及び半導体装置

【課題】従来のダミーパターンの配置方法は、エッチング工程において形成されるパターンにばらつきが生じる問題があった。

【解決手段】本発明にかかるダミーパターンの配置方法は、配線パターンが配置された配線領域にダミーパターンを配置する方法であって、前記配線領域を分割して得られる分割領域において前記配線パターンの占める密度を示すパターン密度を算出する密度算出ステップと、前記分割領域における前記配線パターンの周囲長の合計値を算出する周囲長算出ステップと、算出された前記パターン密度と前記配線パターンの周囲長の合計値と、予め設定される上限値又は下限値との差分に基づいてダミーパターンの形状を決定して配置する配置ステップとを有することを特徴とするものである。

(もっと読む)

半導体集積回路のレイアウトデータ作成装置及びレイアウトデータ作成方法、半導体装置の製造方法

【課題】半導体集積回路の検証精度を向上し、高信頼性、高歩留まり且つ高集積の半導体装置を実現すること。

【解決手段】半導体集積回路の仕様の情報に基づき論理回路図を設計する論理回路図設計部と、論理回路図に基づきレイアウトデータを作成するレイアウトデータ作成部と、レイアウトデータから配線の抵抗の情報を抽出する抵抗情報抽出部と、回路シミュレーションを実行する回路シミュレーション実行部と、配線の抵抗の情報及び回路シミュレーションの実行結果に基づき配線における電流の向きを識別する電流方向識別部と、配線における電流の向きの情報に基づき配線のレイアウトデータが半導体集積回路の仕様の情報から抽出するデザインルールに違反しているか否かを検証してその検証結果を生成する検証部と、レイアウトデータを出力するデータ出力部と、を有する。

(もっと読む)

半導体集積回路のセットアップエラー修正方法および装置

【課題】過剰なセットアップエラー修正を防止し、レイアウトへの影響を低減することができるセットアップエラー修正方法および装置を提供する。

【解決手段】改善度見積もり部106において、修正方法決定部105で決定された修正方法に基づいて改善される遅延値の見積もりを算出し、改善度判定部107へ処理を進める。改善度判定部107において、改善度見積もり部106で見積もった改善度とフリップフロップ間の遅延時間から改善後の予想遅延時間を算出する。改善後の予想遅延時間が要求遅延時間を満たしていない場合、修正箇所選択部104へ戻り、セットアップエラーパスの修正処理を継続する。改善後の予想遅延時間が要求遅延時間を満たすか、修正対象箇所がなくなるまでセットアップエラーパスの修正処理を繰り返す。

(もっと読む)

半導体集積回路及びその製造方法並びにASIC素子の製造方法

【課題】高性能、低消費電力及び低コストを有し、そして開発期間及び開発リスクを減らし得る半導体集積回路の製造方法及びASIC素子の製造方法を提供する。

【解決手段】少なくとも一つの標準化された機能ブロックと、新たに開発したカスタム機能ブロックとを組み合わせて半導体集積回路を製造する方法において、前記標準化された機能ブロックを具現する基本ブロックチップを形成する工程と、前記カスタム機能ブロックを具現する別途のカスタムブロックチップを形成する工程と、前記基本ブロックチップと前記カスタムブロックチップとを結合する工程とを有する。

(もっと読む)

LSIフロアプラン決定装置及び方法並びにプログラム記録媒体

【課題】本発明は、固定形状を持つLSIブロックについても、その配置位置を指定できるようになるLSIのフロアプランを決定できるようにするLSIフロアプラン決定装置の提供を目的とする。

【解決手段】LSIのフロアプランとなるLSIブロックの配置関係をツリー構造で記述する配置関係記述文の初期解を入力あるいは生成する手段と、配置関係記述文を操作し、その操作による配置関係記述文の規定するLSIのフロアプランでは固定形状のLSIブロックが配置不可能である場合には、その配置が可能となるようにと、その固定形状LSIブロックを1つ又は複数の他のLSIブロックとマージしてそこにパッキングし、その評価を求めて、それに従って配置関係記述文を変更するのか否かを決定することを繰り返していくことで、LSIのフロアプランを決定する手段とを備えるように構成する。

(もっと読む)

基板結合等価回路の生成方法

【課題】半導体基板に寄生する基板インピーダンスを介して電気的に結合する基板結合対策として、ガードリング等による、基板結合に対する低減効果を、設計段階で精度よく予測するシミュレーション手法による大規模半導体集積回路における基板結合の等価回路の生成方法を提供する。

【解決手段】基板結合等価回路の生成方法は、半導体集積回路の形成された半導体チップを水平方向にスライスした2個以上の水平部分チップに分割し、それぞれの水平部分チップを抵抗メッシュ近似して基板結合等価回路を導出して、これらの基板結合等価回路を回路ネットリスト上で接続することにより半導体チップ全体の基板結合等価回路を得る。この等価回路を用いて半導体チップ断面方向に強く局所性を持った不純物濃度分布があっても精度劣化しない基板結合による雑音を解析することを可能とする。

(もっと読む)

半導体集積回路の検証方法、検証装置および検証プログラム

【課題】

従来の半導体集積回路の検証方法では、隣接する入出力バッファ同士の配線の接続や、内部回路を設計した後の、入出力バッファ内の電源配線を考慮したLVSネットリストの作成が困難となっていた。

【解決手段】

半導体集積回路の検証方法は、半導体素子の外周部に配置された入出力バッファと、内部回路とを含む半導体集積回路の検証方法であって、前記入出力バッファのライブラリに、前記入出力バッファの配線に関しての物理情報を保持させ、前記物理情報に基づいて前記入出力バッファの配置検証を行う。

(もっと読む)

マクロ提供システム

【課題】 マクロ要求者にマクロを効率よく提供でき、半導体集積回路の設計効率を向上できるマクロ提供システムを提供する。

【解決手段】 提供情報設定処理では、各マクロについて、プロセステクノロジ毎に、マクロの提供可否およびマクロを構成するためのマクロデータの種別が設定される。登録処理では、マクロ名およびプロセステクノロジ名に対応づけてマクロデータが登録される。提供制御処理では、マクロ名、プロセステクノロジ名、マクロデータの種別、マクロ版数およびマクロ要求者の組合せ条件に基づいたマクロの提供が許可される。第1提供処理では、提供制御処理により提供を許可されたマクロのマクロデータがマクロ要求者に提供される。

(もっと読む)

1 - 17 / 17

[ Back to top ]