Fターム[5F082BA36]の内容

Fターム[5F082BA36]に分類される特許

1 - 17 / 17

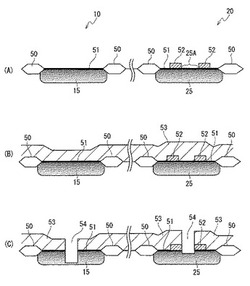

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

半導体装置の製造方法及び半導体集積回路装置

【課題】本発明は、簡素な工程で、デバイスの特性を均一化することができる半導体装置の製造方法及び半導体集積回路装置を提供することを目的とする。

【解決手段】半導体基板40の表面の所定領域41に、LOCOS酸化膜70を形成するLOCOS酸化膜形成工程と、

該LOCOS酸化膜70と前記半導体基板40の表面の境界を覆うように、ポリシリコン膜90を形成するポリシリコン形成工程と、

該ポリシリコン膜90をマスクとして、前記半導体基板40の表面にイオンの打ち込みを行い、前記半導体基板40の表面に、不純物領域60を形成するイオン打ち込み工程と、を含むことを特徴とする。

(もっと読む)

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】トランジスタを短絡させることなく、シリサイド層を形成することができる半導体装置の提供。

【解決手段】バイポーラトランジスタ形成領域100と、CMOSトランジスタ形成領域200とを分離し、絶縁層52a,52bを形成し、上方に導電層56a,56bを形成し、側壁54a,54bを形成して、バイポーラトランジスタ形成領域100に、短絡防止部50aを形成すると同時に、CMOSトランジスタ形成領域200にゲート50bを形成する。バイポーラトランジスタのエミッタ領域40a、コレクタ領域40bおよびベース領域42aおよびCMOSトランジスタのソース領域40c,42bおよびドレイン領域40d,42cを形成し、各領域の上にシリサイド層60を形成する。短絡防止部50aは、エミッタ領域40a、コレクタ領域40bおよびベース領域42aのうち、いずれか2つの領域の間に位置する半導体基板10の上方に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 CMOS製造プロセスを使用しても、バイポーラトランジスタの適切な駆動能力や温度特性を得ることが可能な半導体装置を提供する。

【解決手段】 縦型バイポーラトランジスタ90aとMOSトランジスタ90bからなる構成であって、縦型バイポーラトランジスタの少なくともベース領域は、エッチングにより表面から掘り下げることでMOSトランジスタ90bのウェル20b深さよりも浅くなっている。このためバイポーラトランジスタに必要とされる特性を独立さえて作り込むことが可能である。

(もっと読む)

BICMOS統合のために選択的エピタキシャル成長を用いる、隆起した外因性自己整合型ベースを有するバイポーラ・トランジスタ

【課題】BICMOS統合のために選択的エピタキシャル成長を用いる、隆起した外因性自己整合型ベースを有するバイポーラ・トランジスタを提供する。

【解決手段】隆起した外因性自己整合型ベースを有する高性能バイポーラ・トランジスタが、CMOSデバイスを含むBiCMOS構造と統合される。パッド層を形成して、先在するCMOSデバイスのソースおよびドレインに対して真性ベース層の高さを隆起させることにより、かつ選択的エピタキシを介して外因性ベースを形成することにより、表面の凹凸の影響は、外因性ベースのリソグラフィによるパターン形成時に最小になる。また、バイポーラ構造の製作の間に、化学機械研磨プロセスを使用しないことにより、プロセス統合の複雑さが軽減される。内側のスペーサまたは外側のスペーサが、エミッタからベースを分離するために形成されうる。パッド層、真性ベース層、および外因性ベース層は、一致した外側の側壁表面を有するメサ構造を形成する。

(もっと読む)

エミッタ−ベーススペーサ領域中に低K材料を有するバイポーラトランジスタの作製方法

【課題】本発明はエミッタ−ベーススペーサ領域中に低K材料を有するバイポーラトランジスタの作製方法を提供する。

【解決手段】本発明は半導体ウエハ基板上に配置されたバイポーラトランジスタを供する。バイポーラトランジスタは半導体ウエハ基板中に配置されたコレクタ、コレクタ中に配置されたベース、ベース上に配置され、ベースの少くとも一部と接触するエミッタを含んでよく、エミッタはその中に低K層を有する。低K層はたとえば、エミッタの一方の側に近接して配置するか、エミッタの相対する側に近接して配置してよい。しかし、すべての実施例において、低K層はバイポーラトランジスタの適切な機能を妨げず、従来のバイポーラトランジスタに典型的に付随したエミッタ−ベース容量を、本質的に減す。

(もっと読む)

半導体デバイスの製造方法及び当該方法により得られる半導体デバイス

本発明は、基板(11)と、エミッタ領域(1)、ベース領域(2)及びコレクタ領域(3)を有する少なくとも1つのバイポーラトランジスタを備える半導体本体(12)とを有する半導体デバイス(10)の製造方法であって、当該半導体本体(12)に、前記コレクタ領域とエミッタ領域(1、3)のうちの一方の領域(3)を形成する第1の半導体領域(13)を形成し、半導体本体(12)の表面上には、第1の絶縁層(4)、多結晶半導体層(5)及び第2の絶縁層(6)から成る層のスタックを形成し、該スタックに開口(7)を形成し、その後に、非選択的エピタキシャル成長によって、更なる半導体層(22)を堆積し、開口(7)の底面上の単結晶の水平部分がベース領域(2)を形成し、開口(7)の側面上の多結晶の垂直部分(2A)は多結晶半導体層(5)に接続し、その後に、開口(7)の側面に平行にスペーサ(S)を形成し、そしてエミッタ及びコレクタ領域(1、3)のうちの他方の領域(1)を形成する第2の半導体領域(31)を前記スペーサ(S)の間に形成する、半導体デバイスの製造方法に関する。本発明によれば、上記方法は、前記更なる半導体層(22)を堆積する前に、前記第2の絶縁層(6)に、その下に在る半導体層(5)の端部(5A)から張り出して突出して見える端部(6A)を設けることを特徴とする。この方法により、費用効率の高い、良好な高周波特性を有するバイポーラトランジスタデバイスを得ることができる。  (もっと読む)

(もっと読む)

半導体デバイス及びその製造方法

本発明は、エミッター領域(1)と、ベース領域(2)と、第一、第二及び第三の接続導体を具えるコレクタ領域(3)とを有するバイポーラトランジスタを具える半導体本体(11)及び基板(11)を有する半導体デバイスであって、エミッター領域(1)は、スペーサ(4)を設けたメサ形のエミッター接続領域(1A)と、それに隣接し多結晶シリコンからなる一の導電領域(2AA)をもつベース接続領域(2A)とを具える。本発明に従うデバイス(10)において、ベース接続領域(2A)は、他の導電領域(2AB)を有し、多結晶シリコンからなる一の導電領域(2AA)とベース領域(2)との間に位置決めされ、多結晶シリコンからなる一の導電領域(2AA)の選択エッチングが可能な材料で構成される。このようなデバイス(10)は、本発明に従う方法によって製造することが容易であり、そのバイポーラトランジスタは優れたRF性質を具備する。  (もっと読む)

(もっと読む)

バイポーラトランジスタの製造方法

第一のトレンチ(11)内でバイポーラトランジスタを製造する方法で、一つのフォトリソグラフィマスクのみを適用して第一のトレンチ(11)及び第二のトレンチ(12)を形成する。コレクタ領域(21)を第一のトレンチ(11)及び第二のトレンチ(12)内に自己整合して形成する。ベース領域(31)を第一のトレンチ(11)内にあるコレクタ領域(21)の一部分に自己整合して形成する。エミッタ領域(41)をベース領域(31)の一部分に自己整合して形成する。コレクタ領域(21)に対する接点を第二のトレンチ(12)内に形成し、ベース領域(31)に対する接点を第一のトレンチ(11)内に形成する。バイポーラトランジスタの製造を標準CMOSプロセスに組み入れることができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 製造に多くの工数を必要とせず、回路特性変動を抑制することが可能である半導体装置を提供する。

【解決手段】 シリコン基板1に形成されたNPNトランジスタQ1と、シリコン基板1に形成された複数の抵抗領域8から構成され、NPNトランジスタQ1にNPNトランジスタQ1のhFEに対応したバイアス電圧を与えるための抵抗素子と、複数の抵抗領域8のうちの、抵抗素子の抵抗として機能する抵抗領域8とNPNトランジスタQ1とを接続する配線23aとを備える。

(もっと読む)

バイポーラートランジスターの作製方法

本発明は、標準的な浅いトレンチ分離作製方法を適用してバイポーラートランジスターを作製するための方法を提供するものであり、第一トレンチ(5,50)の中に縦型バイポーラートランジスター(29)又は横型バイポーラートランジスター(49)と、第二トレンチ(7,70)の中に浅いトレンチ分離領域(27,270)を同時に形成する。更に本作製方法は、第一トレンチ(5,50)の中に縦型バイポーラートランジスター(27)、第三トレンチの中に横型バイポーラートランジスター(49)、及び第二トレンチ(7,70)の中に浅いトレンチ分離領域(27,270)を同時に形成することもある。  (もっと読む)

(もっと読む)

バイポーラトランジスタ及びその形成方法

【課題】エミッタ端子及びベース端子が同一な高さを有する高速バイポーラトランジスタを提供する。

【解決手段】高速バイポーラトランジスタは、ベースのためのシリコン−ゲルマニウム膜(25a)をコレクタのための半導体膜(19)上に形成し、エミッタ端子及びコレクタ端子のための接触窓を有する層間絶縁膜(27)(29)を形成し開口する。ポリシリコンを蒸着した後ベース、エミッタ接触窓(35b)(35a)内にポリシリコンを充填し、イオン注入熱処理工程により、エミッタ拡散部(36)を形成する。その後、平坦化処理により、同一高さをもつポリシリコンエミッタ端子及びポリシリコンベース端子を形成する。更に、エミッタ及びベース接触窓と、金属配線との間に安定的なシリサイド膜を形成でき、低抵抗なエミッタ、ベース接触窓を持つバイポーラトランジスタを形成できる。

(もっと読む)

半導体装置、高周波増幅器および携帯情報端末

【課題】チップ面積の増大を抑制しつつ、電流コラプス現象を低減することができる半導体装置と高周波増幅器を提供する。

【解決手段】半導体装置は、GaAs基板6と、GaAs基板の上に設けられたサブコレクタ層5と、サブコレクタ層5の上の一部に設けられたコレクタ層4と、コレクタ層4の上に設けられたベース層(第1の半導体層)3と、ベース層3のうち真性ベース領域11の上に設けられた第2エミッタ層(第2の半導体層)2aと、ベース層3のうち外部ベース領域2aの上に設けられた第2エミッタ層(第2の半導体層)2bと、第2エミッタ層2aの上に設けられた第1エミッタ層1とを有している。

(もっと読む)

自己整合エピタキシャル成長バイポーラ・トランジスタ

照明システムは、複数個の発光素子(R、G、B)を含む光源(1)を有する。これらの発光素子は、少なくとも第1の原色の第1の発光ダイオードと、少なくとも第2の原色の第2の発光ダイオードとを備え、第1と第2の原色がお互いに異なっている。この照明システムは、発光素子によって発せられた光を平行にするためのファセット光コリメータ(2)を有する。このファセット光コリメータは、照明システムの長手方向軸(25)に沿って構成される。ファセット光コリメータ内の光伝搬は、全内部反射に、又はファセット光コリメータのファセット上に施された反射コーティングでの反射に基づいている。ファセット光コリメータは、光源から離れて面する側で、ファセット光反射板に組み合わせる。この照明システムは、光整形拡散体(17)を更に備える。この照明システムは、均一な空間の及び空間角度色分散で光を発する。  (もっと読む)

(もっと読む)

バイポーラ・デバイス、トランジスタ・デバイス、ならびにトランジスタおよびバイポーラ相補型金属酸化膜半導体(BiCMOS)デバイスを製造する方法

【課題】

バイポーラ・デバイス、トランジスタ・デバイス、ならびにトランジスタおよびバイポーラ相補型金属酸化膜半導体(BiCMOS)デバイスを製造する方法を提供することを目的とする。

【解決手段】

コレクタ(112)、コレクタの上方の真性ベース(118)、コレクタに隣接するシャロートレンチ分離領域(114)、真性ベースの上方の隆起外部ベース(202)、外部ベースの上方のT字形のエミッタ(800)、エミッタに隣接するスペーサ(700)、および、スペーサによりエミッタから分離されるシリサイド(400)層を有する、バイポーラ相補形金属酸化膜半導体(BiCMOS)またはNPN/PNPデバイスを開示する。

(もっと読む)

1 - 17 / 17

[ Back to top ]