Fターム[5F083AD54]の内容

Fターム[5F083AD54]の下位に属するFターム

複数に分かれたプレート電極を持つもの (7)

(最下部の)ストレージ電極側面を覆うもの (146)

(最下部の)ストレージ電極の底面と側面を包み込むもの (4)

Fターム[5F083AD54]に分類される特許

1 - 17 / 17

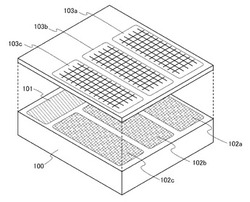

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置の製造方法

【課題】アスペクト比の高い下部電極は、エッチングにより倒壊が生じやすいという問題があった。

【解決手段】複数の筒状の第一の下部電極9上に、前記第一の下部電極9の上端に接合するとともに前記第一の下部電極9同士を連結する第一梁10aを形成する工程の後に、前記第一の下部電極9同士の間の空間を残しつつ、前記第一梁10を覆うように第二の層間絶縁膜11を形成した後に、前記第二の層間絶縁膜11を貫通する複数の筒状の第二の下部電極12を形成する工程と、前記第二の層間絶縁膜11上に、前記第二の下部電極12の上端に接合するとともに複数の前記第二の下部電極12を連結する第二梁13aを形成する工程と前記第二の層間絶縁膜11する工程と、を少なくとも一以上繰り返すことを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

半導体装置及びその製造方法

【課題】新規な半導体装置及びその製造方法を提供する。

【解決手段】主面を有する半導体基板上に層間膜を形成する層間膜形成工程と、前記層間膜に、第1開口幅を有する第1溝と、前記第1開口幅より広い第2開口幅を有する第2溝とを形成する溝形成工程と、前記層間膜の上面上並びに前記第1溝及び前記第2溝の側面上及び底面上に、導電膜を形成する導電膜形成工程と、前記導電膜をエッチングして、前記層間膜の上面上に形成された前記導電膜を除去すると共に、前記第1溝及び前記第2溝の側面上及び底面上に形成された前記導電膜を残すことで、前記第1溝の側面上及び底面上にかけて連続する導電膜から成る第1導電体と、前記第2溝の側面上及び底面上にかけて連続する導電膜から成る第2導電体とを形成する導電膜エッチング工程とを有する方法により、半導体装置を製造する。

(もっと読む)

半導体装置の製造方法

【課題】エッチング時に、除去しにくい反応生成物を生じさせうる膜を含む積層構造の被加工膜にも対応できるエッチング技術を提供する。

【解決手段】ハードマスク膜と前記ハードマスク膜上に積層されたフォトレジスト膜とを含むマスク層を被加工膜上に選択的に形成し、フォトレジスト膜を含むマスク層をマスクとして前記被加工膜に対し第1のエッチングを行い、前記マスク層に前記フォトレジスト膜が実質的に存在しない状態で前記ハードマスク膜をマスクとして前記被加工膜に対し第2のエッチングをさらに行うことを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

半導体装置

【課題】 新たなメモリセルの選択方式を導入することによって、上述した諸問題を解決し安価なDRAMを提供することである。さらには、本選択方式は、その他のDRAMセル、あるいはスタティック・ランダムアクセスメモリ(SRAM)の高性能化にも寄与する。

【解決手段】 アレーを構成する行線Xと列線Yの交点にメモリセルMCが接続され、該1個のメモリセルは行線Xと列線Yで制御され、行線Xと列線Yのそれぞれにパルス電圧が印加されることによって該メモリセルMCが選択されてデータ線DLと信号の授受を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜に設けたホールパターンに形成された導電体膜の断線を防止できる構造を備えた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、第1の導電体膜上に絶縁膜を形成し、絶縁膜を露出する開口部を有するマスク膜を用いた異方性エッチングにより、開口部に露出した絶縁膜の上部に凹部を形成すると共に、マスク膜の側壁部下部に反応生成物を付着させる。次に、等方性エッチングにより、マスク膜の側壁部を水平方向に後退させると共に、異方性エッチングにより、凹部の底部に露出した絶縁膜を垂直方向に掘り下げながら、マスク膜の側壁部下部に付着した反応生成物を除去する。次に、異方性エッチングにより、凹部の周囲に存在する絶縁膜を鉛直方向に掘り下げて段差部を形成すると共に、凹部の底部を貫通させて第1の導電体膜を露出させる。その後、第1の導電体膜の上に第2の導電体膜を形成する。

(もっと読む)

半導体装置、及びその製造方法

【課題】DRAMメモリセル領域と周辺回路(ロジック回路)領域との段差をなくし平坦化して、ウエットエッチングによる層間絶縁膜の除去時にマスク用のフォトレジスト膜を使用せず、ウエットエッチング時に異物の発生を防止すると共に境界領域を小さくする。また、下部電極の倒壊や下部電極同士の接触を防止して、製造に際しての歩留りを向上させた半導体装置及びその製造方法を提供する。

【解決手段】メモリセル領域において凹状の下部電極51と下地層と、境界領域において凹状の下部導電領域51aと下地層と、メモリセル領域及び境界領域において下部電極51、下部導電領域51a、及び下地層の表面を全面、被覆するように設けられた誘電体膜52と、導電層と凸部74とを有する上部導電領域53と、を備えた半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離絶縁膜上に形成されたキャパシタを有する半導体装置において、寄生容量を抑制すること。

【解決手段】本発明は半導体基板10に設けられた素子分離絶縁膜12と、素子分離絶縁膜上に設けられた導電層22と、導電層を覆うように設けられた層間絶縁膜30と、層間絶縁膜内であって導電層上に接触して設けられた金属からなる下層電極42と、層間絶縁膜内であって下層電極上に設けられた誘電体層49と、層間絶縁膜内であって誘電体層上に設けられた金属からなる上層電極52と、を具備する半導体装置およびその製造方法である。

(もっと読む)

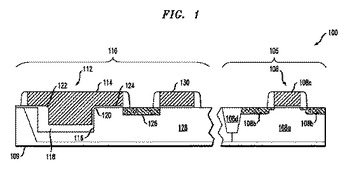

ランダム・アクセス・メモリ・デバイスのトレンチ・キャパシタ漏洩電流を低減する方法

本発明は、一態様では、半導体デバイスを製造する方法を提供する。この方法は、半導体基板(109)のダイナミック・ランダム・メモリ領域(DRAM)(110)内にトレンチ分離構造(118)を形成すること、ならびにトレンチ分離構造(118)の上に、トレンチ分離構造(118)の一部分を露出するようにエッチング・マスクをパターニングすることを含む。露出したトレンチ分離構造(118)の一部分を除去してその中に、半導体基板によって形成された第1の角部と、トレンチ分離構造によって形成された第2の角部とを含むゲート・トレンチ(116)を形成する。エッチング・マスクをDRAM領域(110)から除去し、ゲート・トレンチの少なくとも第1の角部に丸みをつけて、丸みをつけた角部(120)を形成する。この後に、ゲート・トレンチ(116)の側壁の上、第1の丸みをつけた角部(120)の上、およびゲート・トレンチ(116)に隣接する半導体基板(109)の上の酸化物層(124)の形成を続ける。トレンチ(116)をゲート材料で充填する。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】スタック型キャパシタを有するDRAMの微細化に関して、キャパシタの上部電極の上の層間膜を簡易に平坦化できるようにする。

【解決手段】シリコン基板301の上にDRAMセルトランジスタ302、第1の層間膜303及び第1のコンタクトプラグ304が形成されている。第1の層間膜303の上にエッチングストッパ膜305及び第2の層間膜306、第3の層間膜307、第4の層間膜308及び第5の層間膜315が形成されている。層間膜の中に下部開口部309及び上部開口部310が形成され、開口部にキャパシタの下部電極311、容量絶縁膜312、及び上部電極313が形成されている。また、上部電極313の側面で第4の層間膜308と接する領域に下部電極311と同じ材料で構成されるサイドウォール314が形成されている。

(もっと読む)

半導体装置

【課題】 データ保持時間を長くしつつセル電流を向上した半導体装置を提供することを目的とする。

【解決手段】 埋め込み絶縁膜101を有する半導体基板100の埋め込み絶縁膜101上に、フローティングウェル領域102とフローティングウェル領域102を挟むソース/ドレイン領域103と、フローティングウェル領域102内に設けられたトレンチ106a内部にゲート絶縁膜105を介して形成されたゲート電極106とを備えることにより、ソース/ドレイン領域103の不純物イオン濃度を低濃度に保ちリーク電流を抑えてデータ保持時間を長くしつつセル電流を向上する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 半導体記憶装置及びその製造方法に関し、特に、電源を切っても記憶情報を保持しうる不揮発性を有し、情報の保持能力や耐久性などの信頼性が高く、集積度が高くビット単価が安い半導体記憶装置を提供する。

【解決手段】 ゲートGがワード線WLに接続され、一方のソース/ドレインS/Dがビット線BLに接続された転送トランジスタTrと、転送トランジスタTrの他方のソース/ドレインS/Dに一方の電極が接続され、常誘電体を誘電体膜とする常誘電体キャパシタC1と、転送トランジスタTrの他方のソース/ドレインS/Dに一方の電極が接続され、強誘電体を誘電体膜とする強誘電体キャパシタC2とにより半導体記憶装置を構成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】本発明は、蓄積電荷容量を増加させ、微細化に適した半導体装置およびその製造方法を提供する。

【解決手段】MOSトランジスタのソース拡散層SとディープトレンチキャパシタCDTのストレージ電極330を電気的に接続する第一の電極(サーフェスストラップ)520上部に、第二の絶縁膜530を介して上部電極540を形成し、第二のキャパシタを備える。このとき上部電極540をディープトレンチキャパシタCDTのプレート電極320と素子周辺部などにおいて接続し、蓄積電荷容量を増大させる。

(もっと読む)

半導体装置及びその製造方法

【課題】 誘電体膜に用いる材料及び容量上部電極に用いる材料に依存することなく、上部電極のセルプレートの配線遅延を防止し、高集積で且つ高速動作が可能な立体スタック型構造の誘電体メモリを提供する。

【解決手段】 半導体装置は、半導体基板(10)上に形成された第1の凹部(15a)を有する絶縁膜(14)と、第1の凹部(15a)の壁部及び底部に形成された第2の凹部(15b)を有する容量下部電極(16)、第2の凹部(15b)の壁部及び底部に形成された第3の凹部(15c)を有する誘電体膜よりなる容量絶縁膜(17)、並びに第3の凹部(15c)の壁部及び底部に形成された容量上部電極(18A)からなる複数の容量素子とを備える。複数の容量素子を構成する容量上部電極(18A)の少なくとも一部を被覆し、且つ、複数の容量素子に跨るように形成された、容量上部電極(18A)の抵抗よりも低い抵抗を有する低抵抗導電層(19A)を備える。

(もっと読む)

デュアルストレージノードを備える半導体メモリ装置とその製造及び動作方法

【課題】デュアルストレージノードを備える半導体メモリ装置とその製造及び動作方法を提供する。

【解決手段】基板40と、基板40に形成された第1トランジスタと、第1トランジスタのソース領域42に連結された第1ストレージノードと、第1トランジスタのドレイン領域44に連結された第2ストレージノードと、第1及び第2ストレージノードに同時に接触された第1プレートライン62と、を備えることを特徴とする半導体メモリ装置である。

(もっと読む)

電極を有するキャパシタを備えた集積回路およびキャパシタを製造するための方法

【課題】メモリセルに好適に使用できる電極を有するキャパシタを備えた集積回路およびキャパシタを製造するための方法を提供すること。

【解決手段】本発明は、電極を有する少なくとも1つのキャパシタを備えた集積回路(IC)に関しており、キャパシタの電極のうちの少なくともいずれか一方(10または30)は、少なくとも表面がケイ化物化された半球状結晶粒のシリコンまたはシリコン合金から形成されている。

また、本発明は、ケイ化物化電極を有するこのようなキャパシタを得るための製造方法に関している。

(もっと読む)

1 - 17 / 17

[ Back to top ]