Fターム[5F083EP40]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 制御機構 (7,428) | ゲート/チャネル/ゲート構造 (16)

Fターム[5F083EP40]に分類される特許

1 - 16 / 16

半導体装置及び半導体装置の駆動方法

【課題】専有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、該記憶ゲートを絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1及び第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された読み出し信号線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

半導体メモリセルおよびその製造方法

【課題】スイッチング特性に優れ、セルサイズの小さい半導体メモリセルを提供することにある。

【解決手段】ゲート絶縁膜が強誘電体膜4で構成されたMFSFET21からなるメモリ素子と、ゲート絶縁膜が常誘電体膜9で構成されたMISFET22からなる選択スイッチング素子とを備えた半導体メモリセル20であって、MFSFETの第1のゲート電極3は、基板1上の結晶性絶縁膜2表面に形成された結晶性導電膜3からなり、強誘電体膜4は、第1のゲート電極3を覆って結晶性絶縁膜2上に形成され、常誘電体膜9は、半導体膜5を介して強誘電体膜4上に形成され、MISFET22の第2のゲート電極10は、常誘電体膜9上に形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層に新たな機能を有する素子を設けた半導体装置を提供する。

【解決手段】半導体基板上に形成された第1配線層150、及び半導体素子200を備える。第1配線層150は、絶縁層156と、絶縁層156の表面に埋め込まれた第1配線154とを備える。半導体素子200は、半導体層220、ゲート絶縁膜160、及びゲート電極210を備える。半導体層220は、第1配線層150上に位置する。ゲート絶縁膜160は、半導体層220の上又は下に位置する。ゲート電極210は、ゲート絶縁膜160を介して半導体層220の反対側に位置する。

(もっと読む)

半導体記憶装置

【課題】メモリウィンドウが大きく信頼性の高い半導体記憶装置を提供することを課題とする。

【解決手段】表面が絶縁体からなる支持基板の上に設けられた半導体層と、前記半導体層内に設けられた、第1の導電型の2つの拡散層領域と、前記2つの拡散層領域の間の前記半導体層内に位置するチャネルと、前記チャネルの上に設けられたゲート絶縁膜と、前記ゲート絶縁膜の上に設けられたゲート電極と、を有し、前記ゲート絶縁膜は、電荷蓄積機能を有し、前記ゲート電極は、その少なくとも一部がリング状平面構造をなし、前記2つの拡散層領域の一方が、前記リング状平面構造の内側に存在し、他方が前記リング状平面構造の外側に存在することを特徴とする半導体記憶装置により上記課題を解決する。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】シリコン基板11上に、それぞれ複数の絶縁膜及び電極膜14が交互に積層された積層体を設ける。電極膜14は、X方向に延びる複数本の制御ゲート電極CGに分断する。また、積層体内に、選択ゲート電極SGb、SGs、制御ゲート電極CG1〜CG4を貫き、一端がソース線SLに接続され、他端がビット線BLに接続されたU字ピラー30を設ける。そして、最上層の制御ゲート電極CG4に、他の制御ゲート電極CG1〜CG3とは異なる電位を印加する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを備える半導体装置の信頼性を向上させる。

【解決手段】半導体基板1のメモリ用pウェルmpwにおいて、主面S1上に制御ゲート絶縁膜CGIを介して形成された制御ゲート電極CGと、制御ゲート電極CGに隣り合うようにして、メモリゲート絶縁膜MGIを介して形成されたメモリゲート電極MGと、制御ゲート電極CGおよびメモリゲート電極MGの側方下部に形成されたp型のメモリドレイン領域MDおよびメモリソース領域MSとを有する不揮発性メモリNVMにおいて、制御ゲート電極CG下の制御ゲートチャネル領域CHcのp型不純物濃度は、メモリゲート電極MG下のメモリゲートチャネル領域CHmのp型不純物濃度よりも高く、メモリゲートチャネル領域CHmのp型不純物濃度は、制御ゲートチャネル領域CHcに近い第1領域m1よりも、遠い第2領域m2の方が低い。

(もっと読む)

不揮発性半導体記憶装置及びその動作方法

【課題】情報を記憶するための正のしきい値を有する複数の正の準位及び負のしきい値を有する複数の負の準位を設定することが可能な不揮発性半導体記憶装置及びその動作方法を提供する。

【解決手段】本発明の1態様による不揮発性半導体記憶装置は、半導体層の第1の主面側に設けられ、情報を記憶させるための正のしきい値電圧を有する複数の正の準位と負のしきい値電圧を有する複数の負の準位とを備えた電荷蓄積層を含む記憶素子と、前記半導体層の第2の主面側に前記記憶素子と対向して設けられ、前記負の準位に蓄積された情報を正のしきい値電圧を有する情報へと変換する電圧を印加する電極とを具備する。

(もっと読む)

フローティングボディ素子及びバルクボディ素子を有する半導体素子及びその製造方法

【課題】フローティングボディ素子及びバルクボディ素子を有する半導体素子及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は、バルクボディ素子領域及びフローティングボディ素子領域を有する基板を準備する工程を含む。バルクボディ素子領域の基板の活性領域を画定するとともに、フローティングボディ素子領域のうち第1素子領域の基板上に順に積層された第1犠牲パターン及び第1活性パターンを画定する素子分離膜を形成する。フォトリソグラフィ及びエッチング工程を用いて素子分離膜に第1犠牲パターンの一部分を露出させる第1リセス領域を形成する。第1犠牲パターンを除去して第1活性パターン下部に第1空間を形成する。第1空間の内壁及び第1リセス領域の内壁に第1埋込誘電膜を形成する。第1埋込誘電膜を有する基板上に少なくとも第1空間を埋め込む第1埋込パターンを形成する。

(もっと読む)

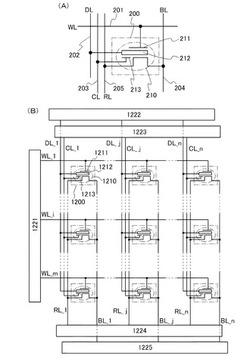

半導体装置およびその駆動方法、表示装置およびその駆動方法

【課題】スイッチングトランジスタおよび不揮発性のメモリトランジスタとして複数のTFTを同一の基板に形成する際において、効率的に、その製造をする。

【解決手段】第1ゲート電極311と第2ゲート電極332とが、半導体層321のチャネル形成領域321cを介して対面しているデュアルゲート構造にて、薄膜トランジスタ300を形成する。ここでは、第1ゲート絶縁膜の側の面よりも、第2ゲート絶縁膜の側の面において、凹凸が大きくなるように、半導体層321を形成する。そして、その半導体層321に対面するように、順次、第2ボトム絶縁層331b、電荷蓄積層331m、第2トップ絶縁層331tを積層することによって、第2ゲート絶縁膜331を形成する。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】低いビットラインコンタクト抵抗を有する不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】第1及び第2フィン105a,105bを備え、第1導電型を有する半導体基板と、第1及び第2フィンの一端を連結する共通ビットライン電極160a,160bと、第1及び第2フィン105a,105bの一側面を覆い、第1及び第2フィン上を横切って延びる複数の制御ゲート電極150と、共通ビットライン電極160a,160bと複数の制御ゲート電極150との間に配置され、第1及び第2フィン105a,105bの一側面を覆い、第1及び第2フィン上を横切って延びる第1ストリング選択ゲート電極155aと、第1ストリング選択ゲート電極と複数の制御ゲート電極との間に配置され、第1及び第2フィンの一側面を覆い、第1及び第2フィン上を横切って延びる第2ストリング選択ゲート電極155bと、を備える不揮発性メモリ素子である。

(もっと読む)

不揮発性半導体記憶素子及び不揮発性半導体記憶装置

【課題】しきい値電圧の制御性が良く、しきい値電圧のバラツキが抑制され、2種類を超えるしきい値電圧の実現と低電源電圧化との両立を図ることのできる高性能な不揮発性半導体記憶素子及び不揮発性半導体記憶装置を提供することを可能にする。

【解決手段】不揮発性半導体記憶素子のチャネルを板状に形成し、チャネル領域の一方の面上には絶縁膜を介して電荷蓄積層を形成し、その上に絶縁膜を介して制御ゲート電極を形成する。チャネル領域の他方の面上には絶縁膜を介して制御ゲート電極を形成する。板状半導体領域の厚さは、その不純物濃度で決まる最大空乏層の厚さの二倍よりも薄く形成する。この様にすると、制御ゲート電極の電圧を変化させる事に伴うしきい値電圧の変動量を、従来素子に於ける限界値を超えて小さくする事が可能となる。その結果としてしきい値電圧の制御性を向上させ、低電源電圧化の可能な、その結果として低消費電力化の可能な不揮発性半導体記憶素子を得ることができる。

(もっと読む)

不揮発性半導体記憶装置及びその制御方法

【課題】プログラムベリファイ時に多数ビットを同時にベリファイ可能にして書き込み動作の高速化を図る。

【解決手段】メモリセルアレイ11のNウェルに形成したメモリセルTrmのソース線SLを、ブロック内ソース線であるカラムソース線CSLおよびブロックソース線BSLで共通に接続するとともにブロックソースセレクトゲートBSSGを介してブロック外ソース線MSLに接続する。このブロック外ソース線MSLは最上層のメタル層でY軸(ビット線方向)に延びるように配線する。プログラムベリファイ時にカラムラッチの出力でビット線から書き込み完了のメモリセルを介して流れるセル電流をこのブロック外ソース線MSLでバイパスさせる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】電荷保持寿命の低下を抑制する。また、書き換え回数の向上と回路動作の速度の向上との両立を図る。

【解決手段】P−型Si基板1のうち、センストランジスタ領域上に、浮遊ゲート4を形成する。このとき、トンネル膜7に接する部分のリン濃度をリンが析出しない濃度とする。その後、浮遊ゲート4の表面上から、P−型Si基板1のうち、選択トランジスタ領域上に至って、絶縁膜8を形成する。このとき、絶縁膜8は、窒化膜、オキシナイトライド膜等の酸化膜より耐湿性及び誘電率が高い膜を用いる。その後、選択トランジスタのゲート電極9を形成する。このとき、ゲート電極9のリン濃度を浮遊ゲート4のトンネル膜7に接する部分の濃度よりも高くする。また、センストランジスタの絶縁膜8aの表面上に、浮遊ゲート4を覆い、且つ固定電位とされる、浮遊ゲート4の電位を遮蔽するための導電性膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 簡易な構成で電荷蓄積時間の長い電荷蓄積層を有するMISトランジスタを実現する。

【解決手段】 SOI−MISFETを有する半導体装置において、絶縁層14と、絶縁層14上に形成されたGeを含む半導体層13と、絶縁層14中の半導体層13との界面付近に形成された、半導体層13よりも高いGe組成を有する複数の半導体ドット15と、半導体層に形成されたMISトランジスタとを備えた。

(もっと読む)

不揮発性メモリ

【課題】 シリコンドットに密度を増加させずに、書き込み前と書き込み後における、メモリ素子のしきい値電圧のシフトを大きくし、かつ電荷の保持時間を長くすることが可能な、シリコンドットを電荷の蓄積に利用した不揮発性メモリ素子を提供する。

【解決手段】 本発明の不揮発性メモリ素子は、完全空乏型の薄膜SOI表面に形成されたトンネル酸化膜と、該トンネル酸化膜表面に所定の密度で形成された複数のシリコンドットと、該シリコンドットを挟んで、トンネル酸化膜上に形成された酸化膜と、該酸化膜の表面に形成されたゲート電極とを備える。

(もっと読む)

半導体装置の製造方法

【課題】 制御用電極と電荷蓄積素子の他に、アシストゲート電極を備えるフラッシュメモリ製造時において、アシストゲートの断線を抑える。

【解決手段】 半導体基板表面に、第1電極を、所定の間隔をおいて形成し、第1電極に挟まれた領域上に第2電極用の材料膜として第2導電膜を形成する。次に、第2導電膜上に絶縁膜を形成し、この絶縁膜上に、第3電極用の材料膜として第3導電膜を形成する。次に、第3導電膜をパターニングして、第3電極を形成する。このとき、第1の電極上に第3導電膜を所定の膜厚分残す条件でパターニングを行う。次に、第3電極と残存する第3導電膜をマスクとして、絶縁膜を除去し、更に、第3電極と残存する第3導電膜と絶縁膜とをマスクとして、第2導電膜をパターニングし、同時に、第1電極上に残した第3導電膜を完全にエッチングする。

(もっと読む)

1 - 16 / 16

[ Back to top ]