Fターム[5F083EP49]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 絶縁膜 (4,144) | ゲート絶縁膜 (1,132) | 材料 (527)

Fターム[5F083EP49]に分類される特許

161 - 180 / 527

不揮発性半導体記憶装置

【課題】本発明の目的は、書き込み/消去特性が向上しつつ、電荷保持特性、が向上した、MONOS型メモリを、簡単、且つ、再現性高く、形成する方法を提供することである。

【解決手段】本発明の半導体装置は、シリコン基板上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成された電荷蓄積膜と、電荷蓄積膜上に形成されたブロック膜と、ブロック膜上に形成された制御ゲート電極膜と、を備えるMONOS型メモリセルであって、トンネル絶縁膜は、シリコン基板上に形成された第1のシリコン酸化膜と、第1のシリコン酸化膜上に形成されたボロンを含むシリコン窒化膜と、シリコン窒化膜上に形成された第2のシリコン酸化膜と、を備えたものである。

(もっと読む)

メモリセルのアレイを作製する方法、メモリセルのアレイ及びメモリセルのアレイにおいてメモリセルを動作させる方法

【課題】安価なメモリデバイスを提供する。

【解決手段】1F2当り少なくとも1ビットを記憶するよう構成されたメモリセルのアレイは、アレイの最小ピッチの半分に等しい距離で離間した電子メモリ機能を与える実質的に縦型の構造を含む。電子メモリ機能を与える構造は、ゲート当り1ビットを超えて記憶するよう構成されている。また、アレイは、実質的に縦型の構造を含むメモリセルに対する電気接点も含む。セルは、第1のソース/ドレイン領域に隣接したゲート絶縁物にトラップされた多数の電荷レベルの1つを有するようプログラムすることができる。これにより、チャネル領域は第1のしきい値電圧領域と第2のしきい値電圧領域とを有し、プログラムされたセルが低減されたドレインソース電流で動作する。

(もっと読む)

半導体記憶装置、及びその製造方法

【課題】動作信頼性を向上させる半導体記憶装置、及びその製造方法を提供すること。

【解決手段】活性領域AA上に形成された第1絶縁膜16と、前記第1絶縁膜16上に複数配置された微小結晶体の電荷蓄積部17と、前記電荷蓄積部17を覆うように、前記第1絶縁膜16上に形成された第2絶縁膜18と、前記第2絶縁膜18上に形成された制御ゲート19とを具備し、前記第1絶縁膜16のゲート幅方向の端部における前記電荷蓄積部17の密度は、ゲート幅方向の中心部における密度よりも大きい。

(もっと読む)

電荷を非対称に捕獲する多値メモリセル

【課題】高メモリ密度、低電力消費、及び高信頼性を達成可能なNAND型多値メモリセルを提供する。

【解決手段】NAND型多値メモリセルは、2つのドレイン/ソース領域を基板に有する。2つのドレイン/ソース領域の間における基板の上方には、酸化物−窒化物−酸化物構造体が形成される。このうち窒化物層は、電荷を非対称に捕獲する層として機能する。酸化物−窒化物−酸化物構造体の上方には、制御ゲートが配置される。ドレイン/ソース領域に非対称のバイアスをかけることで、ドレイン/ソース領域に高い電圧が生じ、これによってドレイン/ソース領域の略近傍における電荷捕獲層にGIDL(ゲートに起因するドレインでの電流漏れ)正孔注入処理を行い、正孔を非対称な分布で注入する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】垂直壁の貫通ホールが形成でき、また、貫通ホールがテーパ状となった場合においても上部と下部とでしきい値電圧特性が均一化でき、安定して動作する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】基板11と、基板の主面11a上に設けられ、主面に対して垂直な第1方向に交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、積層構造体を前記第1方向に貫通する半導体ピラーSPと、電極膜のそれぞれと半導体ピラーとの交差部に設けられた記憶部(記憶層48)と、を備える不揮発性半導体記憶装置が提供される。電極膜は、アモルファスシリコン及びポリシリコンの少なくともいずれかを含む。基板からの距離が近い第1領域RG1の電極膜に含まれる添加物の濃度は、第1領域よりも基板からの距離が遠い第2領域RG2の電極膜に含まれる添加物の濃度とは異なる。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

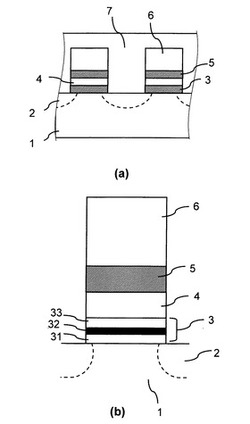

【課題】ワードゲートとコントロールゲートの間の高低差を大きくすることなく、シリサイドショートを防止することが可能な不揮発性半導体記憶装置、及びその製造方法を提供すること。

【解決手段】本発明にかかる不揮発性半導体記憶装置は、半導体基板1上にゲート絶縁膜2を介して形成され、一定の幅を有する部分が上に突出した突出部3bが設けられているワードゲート3と、ワードゲート3の側壁面にONO膜4を介して設けられたコントロールゲート5と、コントロールゲート5の側壁面と、ワードゲート3の突出部3bの側壁面とに形成された絶縁性のサイドウォール7と、ワードゲート3の突出部3bの上面と、コントロールゲート5の表面の一部とに形成されたシリサイド層9と、を備え、突出部3bの幅は、突出部3bよりも下側の部分のワードゲート3の幅よりも狭いものである。

(もっと読む)

半導体装置及びその製造方法

【課題】深さの異なる複数のコンタクトホールの底部径のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、階段構造部を覆って設けられた層間絶縁層43と、層間絶縁層43を貫通し、それぞれが対応する各段の導電層WL1〜WL4に達して形成された複数のコンタクトホール61〜64の内部に設けられたコンタクト電極60とを備え、複数のコンタクトホール61〜64の底部の孔径は略同じであり、下段側の導電層に達するコンタクトホールは、上段側の導電層に達するコンタクトホールよりも深く、上端部の孔径が大きい。

(もっと読む)

Fin−FET型不揮発性メモリ・セル及びアレイ並びにその製造方法

不揮発性メモリ・セルが、基板層を有し、第1の導電型のフィン形状半導体部材が基板層上にある。フィン形状部材は、第2の導電型の第1の領域と、第1の領域から離間配置された第2の導電型の第2の領域とを有し、チャネル領域が第1の領域と第2の領域との間に延びている。フィン形状部材は、第1の領域と第2の領域との間に上面及び2つの側面を有する。ワード線が、第1の領域に隣接し、チャネル領域の第1の部分の上面及び2つの側面に容量結合される。浮遊ゲートが、ワード線に隣接し、上面から絶縁され、チャネル領域の第2の部分の2つの側面に容量結合される。 (もっと読む)

3次元メモリセルアレイを含む半導体メモリ素子及びその製造方法

【課題】高密度、且つ工程マージンの確保された3次元メモリセルアレイを含む半導体メモリ素子を提供する。

【解決手段】平坦な基板と、基板に対して垂直に形成され且つ各々複数の貯蔵セルを含む複数のメモリストリングからなるメモリストリングアレイと水平方向に互いに重畳した複数のワードラインを含み、ワードラインは各々基板に平行で且つメモリストリングに接続された第1部分及び第1部分から延伸され基板に対して上方に傾斜する第2部分を含み、メモリストリングアレイは複数のワードラインの各々の第1部分の中間部分に配置され、ワードラインの各々に接続されて各々対応する貯蔵セルを形成し、複数のワードラインの第1、第2グループは各々、メモリストリングアレイの第1、第2の側方に配置された第1、第2導電ラインのグループの各々と電気的に接続される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】制御ゲート電極からリークした電子のエネルギーの増加を抑制し、トンネル絶縁膜の絶縁性の劣化を防止する。

【解決手段】本発明の例に係わる不揮発性半導体記憶装置は、半導体層101と、半導体層101の表面に形成された第1の絶縁膜102と、第1の絶縁膜102の表面に形成された電荷蓄積膜103と、電荷蓄積膜の表面に形成された第2の絶縁膜104と、第2の絶縁膜104の表面に形成された制御ゲート電極105とを具備し、電荷蓄積膜103及び第2の絶縁膜104の少なくとも一方に、散乱によって電子のエネルギーを減少させる非弾性散乱層が少なくとも一層含まれている。

(もっと読む)

半導体装置

【課題】MONOS型不揮発性メモリの信頼性を向上させる。

【解決手段】メモリセルは、選択ゲート6とその一方の側面に配置されたメモリゲート8とを有している。メモリゲート8は、一部が選択ゲート6の一方の側面に形成され、他部がメモリゲート8の下部に形成されたONO膜7を介して選択ゲート6およびp型ウエル2と電気的に分離されている。選択ゲート6の側面にはサイドウォール状の酸化シリコン膜12が形成されており、メモリゲートの側面にはサイドウォール状の酸化シリコン膜9と酸化シリコン膜12とが形成されている。メモリゲート8の下部に形成されたONO膜7は、酸化シリコン膜9の下部で終端し、酸化シリコン膜12の堆積時にメモリゲート8の端部近傍の酸化シリコン膜12中に低破壊耐圧領域が生じるのを防いでいる。

(もっと読む)

不揮発性半導体記憶装置、不揮発性半導体記憶装置の製造方法

【課題】記憶領域の増大を抑制しつつ、より多くの情報を記憶できる不揮発性半導体記憶素子を提供する。

【解決手段】第1ソース/ドレイン拡散層(11)と、第2ソース/ドレイン拡散層(12)と、チャネル領域の上に構成され、電気的に絶縁される二つの電荷蓄積層(21)と、電気的に絶縁された二つのゲート電極(13、14)とを具備する不揮発性半導体記憶装置を構成する。第1の電荷蓄積層(2−1、2−2)は、第1領域(2−1)と第2領域(2−2)とを有し、第2の電荷蓄積層(2−3、2−4)は、第3領域(2−3)と第4領域(2−4)とを有するものとする。そして、第1のゲート電極(13)は、第1領域(2−1)と第3領域(2−3)とに跨り、第2のゲート電極(14)は、第2領域(2−2)と第4領域(2−4)とに跨る。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】階層が異なる電極層間での特性ばらつきを抑制する半導体装置の製造方法及び半導体装置を提供する。

【解決手段】本発明の半導体装置の製造方法は、絶縁層15と電極層WLとを交互に複数積層する工程と、絶縁層15と電極層WLとの積層体を貫通するメモリホール18を形成する工程と、メモリホール18の内壁に導電膜31を形成する工程と、導電膜31に対して異方性エッチングを行い、メモリホール18の側壁に導電膜31を選択的に残す工程と、熱処理を行い、導電膜31を絶縁物に変質させる工程と、電極層WLを覆う絶縁物を除去し、メモリホール18内に電極層WLを露出させる工程と、を備えた。

(もっと読む)

NAND型フラッシュメモリ

【課題】チップ内のメモリプレーン数が増えてもロウデコーダ数の増加を抑える。

【解決手段】NAND型フラッシュメモリは、第1及び第2メモリプレーン11A,11B間に配置され、第1NANDブロックBKi内の第1ワード線WL0〜WLn及び第3NANDブロックBKi内の第2ワード線WL0〜WLnに共通接続される第1転送トランジスタ18と、第1メモリプレーン11Aの第2メモリプレーン11B側とは反対側の第1端に配置され、第2NANDブロックBK(i+1)内の第3ワード線WL0〜WLnに接続される第2転送トランジスタ18と、第2メモリプレーン11Bの第1メモリプレーン11A側とは反対側の第2端に配置され、第4NANDブロックBK(i+1)内の第4ワード線WL0〜WLnに接続される第3転送トランジスタ18とを備える。

(もっと読む)

半導体装置の製造方法

【課題】電荷蓄積膜を用いる不揮発性記憶用MOS型トランジスタと、これを選択するMOS型トランジスタが隣接するスプリットゲート構造を有する不揮発性メモリセルにおいて、電荷保持特性を向上し、ゲート電極を低抵抗化する。

【解決手段】電荷蓄積膜のコーナー部20の薄膜化を抑制して電荷保持特性を向上するために、選択ゲート電極15の側壁にテーパーを設ける。また、自己整合で形成するゲート電極を低抵抗化するシリサイドを安定に行うため、選択ゲート電極15の側壁をリセスさせる。もしくは、自己整合ゲート電極上部18と選択ゲート電極上部65の間に段差を設ける。

(もっと読む)

インサイチュでのメモリのアニール

メモリデバイスを有するシステムにおいて、あるイベントがシステム操作中に検出される。メモリデバイスは、そのイベントの検出に応じて、メモリデバイスの使用に起因する劣化を反転させるために加熱される。別のシステムにおいて、メモリデバイスは、そのシステムの別のメモリデバイス内でのデータアクセス操作と同時に使用に起因する劣化を回復させるために加熱される。第1および第2のメモリデバイスと連結されたメモリコントローラを有する別のシステムにおいては、データは、メンテナンス操作が第1のメモリデバイス内において必要であると決定することに応じて、第1のメモリデバイスから第2のメモリデバイスに退避される。 (もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】選択ゲート電極を低抵抗化し、半導体ピラーを選択する選択ゲートトランジスタの応答特性が良好な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】第1方向に交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、前記第1方向において積層構造体MLに積層された選択ゲート電極SGと、積層構造体MLと選択ゲート電極SGとを前記第1方向に貫通する半導体ピラーSPと、電極膜WLのそれぞれと半導体ピラーSPとの交差部に設けられた記憶部と、半導体ピラーSPと選択ゲート電極SGとの間に設けられた選択ゲート絶縁膜SGIと、を備えた不揮発性半導体記憶装置が提供される。選択ゲート電極SGは、選択ゲート電極SGの前記第1方向に対して垂直な面上に設けられた第1シリサイド層51を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】優れた特性を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板100に設けられた素子形成領域10bと、素子形成領域上に形成されたトンネル絶縁膜11と、トンネル絶縁膜上に形成された電荷蓄積絶縁膜12と、電荷蓄積絶縁膜上に形成されたブロック絶縁膜14と、ブロック絶縁膜上に形成された制御ゲート電極15と、を備えたメモリセルトランジスタと、メモリセルトランジスタに隣接して形成された素子分離領域13と、を具備し、メモリセルトランジスタのチャネル幅方向に平行な断面において、電荷蓄積絶縁膜の端部の膜厚は、電荷蓄積絶縁膜の中央部の膜厚よりも薄い。

(もっと読む)

メモリ半導体装置、その製造方法、及び動作方法

【課題】メモリ半導体装置、その製造方法及び動作方法を提供する。

【解決手段】メモリ半導体装置は、基板の上部面に垂直長軸を有し、2次元的に配列される複数の半導体パターン、及び複数の半導体パターンを横切る長軸を有しながら、複数の半導体パターン間で3次元的に配列される複数のワードラインを包含できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】貫通ホールの径の変動に起因した電界の変動を補償し、良好な動作特性を有する不揮発性半導体記憶装置を提供する。

【解決手段】第1方向に交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、積層構造体を第1方向に貫通する半導体ピラーSPと、電極膜のそれぞれと半導体ピラーとの間に設けられた記憶層48と、記憶層と半導体ピラーとの間に設けられた内側絶縁膜42と、電極膜のそれぞれと記憶層との間に設けられた外側絶縁膜43と、を備える。第1方向に対して垂直な第2方向における外側絶縁膜の外径が大きい領域では、外径が小さい領域よりも、第2方向における外側絶縁膜の厚さが厚い。

(もっと読む)

161 - 180 / 527

[ Back to top ]