Fターム[5F083EP49]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 絶縁膜 (4,144) | ゲート絶縁膜 (1,132) | 材料 (527)

Fターム[5F083EP49]に分類される特許

201 - 220 / 527

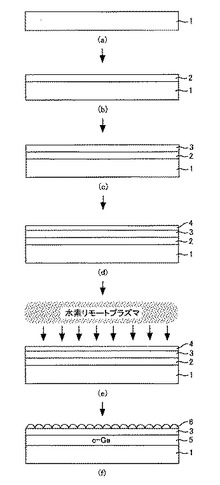

結晶半導体の製造方法およびそれを用いた半導体素子の製造方法

【課題】低温で結晶半導体を形成可能な結晶半導体の製造方法を提供する。

【解決手段】80〜240nmの膜厚を有するa−Ge膜2が基板1上に形成される(工程(b)参照)。そして、約10nmの膜厚を有するSiO2膜3がa−Ge膜2上に形成される(工程(c)参照)。その後、約90nmの膜厚を有するPt薄膜4がスパッタリングまたは蒸着によってSiO2膜3上に形成される(工程(d)参照)。そして、Pt薄膜4は、水素リモートプラズマによって処理される(工程(e)参照)。

(もっと読む)

メモリ装置を製造するための方法

【課題】メモリ装置を製造するための方法。

【解決手段】ナノ粒子244を含むメモリ装置100を製造するための方法であって、少なくとも1つの半導体をベースとする基板において、ソースおよびドレイン領域118、120と、ソースおよびドレイン領域118、120の間に配置され、かつメモリ装置100のチャネル121を形成するための基板の少なくとも1つの領域上に少なくとも1つの第1の誘電体241とを形成するステップと、少なくとも1つの導電材料のナノ粒子を懸濁した状態で含み、少なくとも第1の誘電体241を覆う少なくとも1つのイオン液を堆積するステップと、ナノ粒子244の堆積物を少なくとも第1の誘電体241上に形成するステップと、残りのイオン液を除去するステップと、ナノ粒子244の堆積物の少なくとも一部上に、少なくとも1つの第2の誘電体252および少なくとも1つの制御ゲート254を形成するステップとを含む。

(もっと読む)

半導体不揮発性メモリ、半導体不揮発性メモリの電荷蓄積方法、及び電荷蓄積プログラム

【課題】電流値分布幅をより狭くして電流ウィンドウをより広げる。

【解決手段】半導体基板における電荷蓄積部に電荷を徐々に蓄積するため、ゲート電圧は書き込み回数が増加するに従って徐々に増加させる(B)。チャネル領域に流れる電流の値が、電荷蓄積部に蓄積される電荷の量が所定のデータに対応する値となった場合に該チャネル領域に流れる電流の予め定められた目標値よりも大きい領域において、該電流の値が該目標値に近づいた場合に、ソース電圧、ドレイン電圧を下げることにより、1回当たりの電荷の蓄積量の増加割合を減少させる(C)。よって、各電荷蓄積部への電荷の蓄積量が目標値を超えることを抑えることができる。

(もっと読む)

NAND型フラッシュメモリ

【課題】メモリセルのしきい値電圧の分布幅の拡大を抑制することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリは、第1の絶縁膜、電荷保持層、第2の絶縁膜、および、制御ゲートを含み、電荷保持層に保持された電荷量に応じた情報を記憶するメモリセルが直列に複数接続されたNANDストリングと、制御ゲートおよび半導体ウェルに印加する電圧を制御する制御回路とを備え、書き込み動作後、選択メモリセルにデータが書き込まれたか否かを検証するベリファイリード動作を行う前に、制御回路は、選択メモリセルの制御ゲートに、半導体ウェルの電位と同電位または書き込み電圧と同極性である第1の電圧を印加し、書き込み対象ではない非選択メモリセルの制御ゲートには、書き込み電圧と同極性であり第1の電圧よりも絶対値として大きい第2の電圧を印加するデトラップ動作を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】ブロック絶縁膜をゲート幅方向に連続するように構成しながら、シリコン基板の上面部のうちのワード線方向の端部とゲート電極との間の絶縁破壊の発生を抑制する。

【解決手段】素子分離領域2によって区画された活性領域3を有する半導体基板1と、活性領域3上に形成されたトンネル絶縁膜7と、トンネル絶縁膜7上に形成された電荷蓄積膜8と、電荷蓄積膜8上に形成されたブロック絶縁膜9と、ブロック絶縁膜9上に形成されたゲート電極10、11とを有してなるメモリセルトランジスタを備え、ブロック絶縁膜9をゲート幅方向に連続するように形成し、更に、電荷蓄積膜8のうちのゲート幅方向の端部8aの膜厚を厚くするように構成した。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】選択ゲートトランジスタに隣接するメモリセルに発生するGIDL電流を防止する。

【解決手段】本発明の例に係わる不揮発性半導体記憶装置は、半導体基板1と、半導体基板1上に形成され、絶縁膜で構成される電荷蓄積層3及びゲート電極9をそれぞれ有する第1及び第2のメモリセルと、第1のメモリセルMCaに隣接して形成される選択ゲートトランジスタST1とを具備し、選択ゲートトランジスタST1のチャネル領域は、第1導電型の領域12と、第1導電型の領域12の上面に第1導電型とは反対の第2導電型の領域13で形成され、第1のメモリセルMCaのチャネル領域は、第1導電型の領域14と、第1導電型の領域14の上面の少なくとも一部に第2導電型の領域15が形成され、第1のメモリセルMCaに格納されるデータ数は、第2のメモリセルMCに格納されるデータ数より少なく形成される。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜とゲート電極との間の界面層にカーボン層を導入して、低い閾値電圧を実現している例では、カーボン層中のカーボンはSi半導体基板中に入り、欠陥準位を形成するため、EWFが不安定であった。本発明は上記問題点を解決するためになされたもので、p−metalを用いたMIS型半導体装置において、EWFを安定して増加させることが可能な半導体装置を提供する。

【解決手段】半導体基板10と、半導体基10上に形成された絶縁膜20と、絶縁膜20上に形成され、且つ、CN基又はCO基を含む界面層30と、界面層30上に形成された金属層40とを備えて半導体装置を構成する。

(もっと読む)

半導体装置

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】素子分離領域形成時に周辺回路領域のゲート絶縁膜へのダメージを防ぐことが可能な半導体記憶装置及びその製造方法を提供すること。

【解決手段】メモリセル及び周辺トランジスタが配置される第1、第2領域にゲート絶縁膜及び導電層を順次形成し、前記第2領域に第1トレンチを形成し、前記第1トレンチに露出する前記第1導電層、前記ゲート絶縁膜の側面、前記第1トレンチの側面及び底面に沿って第1シリコン酸化膜を堆積し、前記第1領域に第2トレンチを形成すると共に、前記第1トレンチ側面の前記第1シリコン酸化膜を残存させつつ、前記第1トレンチの底面を第2トレンチよりも深く形成し、第2シリコン酸化膜の堆積と該第2シリコン酸化膜の一部の除去とを繰り返して第1、第2トレンチ内に第2シリコン酸化膜を埋め込み、前記第1、第2領域に第1、第2素子分離領域を形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】本発明は、半導体基板表面の斜面に不揮発性素子のチャネル領域を形成して素子の微細化を図ることを最も主要な特徴とする。

【解決手段】素子分離領域によって区画され、表面が凹凸を連続的に繰り返すように形成された素子形成領域13を有する半導体基板と、素子形成領域上に形成されたトンネル絶縁膜14と、素子形成領域の互いに隣り合う凹部上と凸部上及びその間の斜面上に渡って連続するように、トンネル絶縁膜14を介して形成された浮遊ゲート15と、浮遊ゲート上に形成されたゲート間絶縁膜16と、ゲート間絶縁膜上に形成された制御ゲート11と、浮遊ゲートに隣接するように凹部に形成された拡散層17とを具備する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】MONOS型の半導体記憶装置で、メモリセルトランジスタ間の素子分離絶縁膜の上面の高さが、電荷蓄積膜の厚さの範囲に位置するように制御された半導体記憶装置を提供する。

【解決手段】シリコン基板1上に、トンネル絶縁膜21、電荷蓄積膜22、ブロック絶縁膜23および制御ゲート電極24を順に積層したゲート電極部MGと、ゲート電極部MGの下部のチャネル領域を挟んだシリコン基板1の第1の方向の両側に形成されるソース/ドレイン領域30と、を有するメモリセルトランジスタTrmと、メモリセルトランジスタTrmを隣接するメモリセルトランジスタと分離するシリコン基板1に形成された素子分離絶縁膜12と、を備え、第1の方向に垂直な第2の方向に沿った断面での素子分離絶縁膜12の上面は、端部で電荷蓄積膜22の厚さの範囲内に存在し、中央部付近で最も高く、端部と中央部との間で極小となる形状を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリセルを有する半導体装置において、メモリ周辺回路の信頼性を向上させることのできる技術を提供する。

【解決手段】メモリ周辺回路領域の高圧系nMISおよび高圧系pMISのゲート絶縁膜14を、半導体基板1の主面上に順次積層された下層の絶縁膜11b、電荷蓄積層CSLおよび上層の絶縁膜11tにより構成し、続いて上層の絶縁膜11t上に積層されたn型の導電膜により高圧系nMISのゲート電極GHnまたは高圧系pMISのゲート電極GHpを構成する。メモリ周辺回路領域の低圧系nMISおよび低圧系pMISのゲート絶縁膜8を、半導体基板1の主面上に形成された酸化シリコン膜により構成する。

(もっと読む)

不揮発性半導体メモリ

【課題】トンネル絶縁膜中に挿入する微粒子層における粒径の微小化でエネルギーバリアを高くして記憶保持を改善しても、低電圧/低電界書き込み・消去時にける低いエネルギーバリアによる書き込み・消去の劣化を抑制する。

【解決手段】半導体基板100のチャネル領域101上にトンネル絶縁膜110を介して電荷蓄積層130を形成した不揮発性半導体メモリであって、トンネル絶縁膜110中に、第1の導電性微粒子を含む第1の微粒子層121をチャネル側に、第1の導電性微粒子よりも平均粒径が大きい複数の第2の導電性微粒子を含む第2の微粒子層122を電荷蓄積層側に設け、第1の導電性微粒子における電子1個の帯電に必要なエネルギーの平均値ΔE1 を、第2の導電性微粒子の電子1個の帯電に必要なエネルギーの平均値ΔEよりも小さくし、ΔE1 とΔEとの差を熱揺らぎのエネルギー(kBT)よりも大きくした。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】高い信頼性を有し、安価な不揮発性半導体記憶装置、その製造方法を提供する。

【解決手段】メモリストリングMSは、一対の柱状部、及びそれらの下端を連結させる連結部を有するU字状半導体層35、柱状部を取り囲むトンネル絶縁層34c、電荷蓄積層34b、ブロック絶縁層34a、及びブロック絶縁層34aを取り囲むワード線導電層32a〜32dを備える。ソース側選択トランジスタSSTrは、柱状部から上に延びるソース側柱状半導体層47b、ソース側柱状半導体層47bを取り囲む第2ソース側ゲート絶縁層46d、第1ソース側ゲート絶縁層46b、及び第1ソース側ゲート絶縁層46bを取り囲むソース側導電層42bを備える。ブロック絶縁層34aは、ソース側ゲート絶縁層46Bと連続して形成されている。U字状半導体層35は、ソース側柱状導体層47bと連続して形成されている。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】高い信頼性を有する不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリトランジスタMTrの制御電極として機能するワード線導電層31a〜31dとを備える。ワード線導電層31a〜31dは、その端部の位置が異なるように階段状に形成された階段部STを構成する。また、不揮発性半導体記憶装置は、階段部STを構成するワード線導電層31a〜31dの上面から上方に延びる第2コンタクトプラグ層55b〜55eを備える。第2コンタクトプラグ層55b〜55eは、上端が基板Baと平行な面において揃うように形成され且つその上端から下端へとその径が小さくなるように形成されている。第1、第2コンタクトプラグ層54、55b〜55fは、その積層方向の長さが長いほど、その上端の径が大きくなるように形成されている。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】セル電流を増大させる不揮発性半導体記憶装置、その製造方法を提供する。

【解決手段】メモリトランジスタ層30は、一対の柱状部35a、及び連結部35bを有するU字状半導体層35と、U字状半導体層35の側面を取り囲むように形成された電荷蓄積層34bと、電荷蓄積層34bの側面を取り囲むように形成された第1〜第4ワード線導電層32a〜32dとを備える。選択トランジスタ層40Aは、柱状部35aの上面から上方に延びるドレイン側柱状半導体層47a(ソース側柱状半導体層47b)と、その側面を取り囲むように形成されたドレイン側ゲート絶縁層46A(ソース側ゲート絶縁層46B)と、その側面を取り囲むように形成されたドレイン側導電層42a(ソース側導電層42b)と、その上面に形成され、且つシリコンゲルマニウムを含む半導体層49aとを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】読み出し時のセル電流を増大させる揮発性半導体記憶装置を提供する。

【解決手段】メモリストリングMSは、基板Baに対して垂直方向に延びるメモリ柱状半導体層35と、メモリ柱状半導体層35の側面を取り囲むように形成された電荷蓄積層34bと、電荷蓄積層34bの側面を取り囲むように形成され、メモリトランジスタMTr1〜MTr4の制御電極として機能するワード線導電層31a〜31dとを備える。ワード線導電層31a〜31dは、その間に誘電体を挟んで前記垂直方向に所定間隔Lをもって設けられている。誘電体は、酸化シリコンの比誘電率よりも小さい比誘電率を有する空気にて構成されている。所定間隔Lは、空気の等価酸化膜厚DEOTが、次の関係式[数1]を満たすように設定されている。

[数1]

Dsio2<DEOT<Dk

(もっと読む)

半導体装置,及び半導体装置の製造方法

【課題】上部絶縁層と素子分離絶縁層の界面に起因する信頼性劣化が抑制された半導体装置を提供する。

【解決手段】半導体装置は,半導体基板と,前記半導体基板上に配置され,かつトンネル絶縁膜,電荷蓄積層,上部絶縁層,および制御電極が順に積層される積層構造と,前記積層構造の側面に配置される素子分離絶縁層と,前記半導体基板の前記トンネル絶縁膜の両側に形成された不純物ドーピング層と,を具え,前記素子分離絶縁層は,SiO2,SiN及びSiONの少なくとも一つからなり,前記上部絶縁層は,希土類金属,Y,Zr,及びHfからなる群より選ばれる少なくとも一つの金属M,及びSiを含む酸化物であり,前記電荷蓄積層,前記上部絶縁層,前記制御電極それぞれのチャネル長方向の長さLcharge,Ltop,Lgateが関係「Lcharge,Lgate < Ltop」を満たす。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリトランジスタの特性が良好な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板11上に、それぞれ複数の絶縁膜及び電極膜14が交互に積層された積層体を設ける。電極膜14は、X方向に延びる複数本の制御ゲート電極CGに分断する。また、積層体内に、選択ゲート電極SGb、SGs、制御ゲート電極CGを貫き、一端がソース線SLに接続され、他端がビット線BLに接続されたU字ピラー30を設ける。そして、各制御ゲート電極CGは、Y方向において隣り合う2本のシリコンピラー31によって貫かれており、接続部材32によって相互に接続された2本のシリコンピラー31は、相互に異なる制御ゲート電極CGを貫いている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

201 - 220 / 527

[ Back to top ]