Fターム[5F083EP64]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 拡散領域 (1,645) | ドレイン領域 (815) | 逆導電型領域を有するもの (69)

Fターム[5F083EP64]に分類される特許

1 - 20 / 69

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

半導体装置

【課題】消去特性と消去ディスターブ特性との双方を向上することが可能な、MONOS型メモリセルなどの半導体装置を提供する。

【解決手段】半導体基板SUBの主表面に形成される第1のゲート電極CGと、主表面上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる絶縁膜ONOと、第1および第2のゲート電極CG,MGの真下のチャネル領域を挟むように、主表面に形成される1対のソース/ドレイン領域NR1,NR2とを備える。上記ソース領域NR1は、第1のソース領域N11および第2のソース領域N12を含んでいる。上記第2のソース領域N12は第1のソース領域N11よりも主表面から深い領域に形成されている。上記第1のソース領域N11と第2のソース領域N12とに含まれる不純物の材質が異なっている。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

半導体装置

【課題】動作特性に対する信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコンを含む基板7と、前記基板7上に設けられた積層体6と、を有する半導体装置1であって、前記積層体6は、少なくとも前記積層体6の側壁の前記基板側にフッ素を含む抑制領域13を有している。前記抑制領域13は、基板7上に設けられた絶縁膜2の前記側壁側に設けられ、フッ素濃度は、チャネル領域11のフッ素濃度よりも高い。

(もっと読む)

半導体メモリ装置

【課題】短チャネルでも動作するフローティングゲートを有する半導体メモリ装置を提供する。

【解決手段】フローティングゲート104に窒化インジウム、窒化亜鉛等の仕事関数が5.5電子ボルト以上の高仕事関数化合物半導体を用いる。このことにより、基板101とフローティングゲート104の間のフローティングゲート絶縁膜103のポテンシャル障壁が従来のものより高くなり、フローティングゲート絶縁膜103を薄くしても、トンネル効果による電荷の漏洩を低減できる。フローティングゲート絶縁膜103をより薄くできるのでチャネルをより短くできる。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリは、半導体基板1上に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1上に電荷蓄積部を有する絶縁膜5を介して形成されたメモリゲート電極MGとを有しており、メモリゲート電極MGは、制御ゲート電極CGの側面22上に絶縁膜5を介してサイドウォールスペーサ状に形成されている。制御ゲート電極CGは、メモリゲート電極MGに絶縁膜5を介して隣接する側とは反対側の側面21の下部21aが突出し、また、メモリゲート電極MGに絶縁膜5を介して隣接する側の側面22の下部22aが後退している。メモリゲート電極MGは、制御ゲート電極CGに絶縁膜5を介して隣接する側の側面23の下部23aが突出している。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】第2導電型のトンネル領域のフローティングゲート電極のエッジ部の下部に、第1導電型の領域からなるフローティングゲート電極エッジの電界集中防止用領域を形成する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域の表面には、薄い不純物濃度の第1導電型の領域を形成した。

(もっと読む)

半導体装置およびその製造方法

【課題】高品質な半導体装置およびその製造方法を提供する

【解決手段】半導体基板1内に形成された一対の第1の不純物拡散領域1bと、一対の第1の不純物拡散領域1bに挟まれ、一対の第1の不純物拡散領域1bに隣接して形成され、第1の不純物拡散領域1bと同じ導電型且つ第1の不純物拡散領域1bよりも不純物濃度の低い一対の第2の不純物拡散領域1aと、一対の第2の不純物拡散領域1aに挟まれたチャネル領域と、第1の不純物拡散領域1b上に形成された周辺絶縁膜4と、第2の不純物拡散領域1a上およびチャネル領域上に形成され、周辺絶縁膜4よりも膜厚の厚いゲート絶縁膜3と、ゲート絶縁膜3上且つチャネル領域の略直上に形成されたゲート電極5とを備える。

(もっと読む)

不揮発性メモリセル、これを有するメモリアレイ、並びに、セル及びアレイの操作方法

【課題】自己収束消去動作を容易にすると共に保持状態の期間におけるメモリデバイスの電荷蓄積層内での電荷保持能力を保持してもいるトンネル誘電体構造を有する不揮発性メモリデバイスの提供。

【解決手段】半導体基板101であって、該基板の表面より下に配置され且つチャネル領域106によって分離されたソース領域102及びドレイン領域104を備えた半導体基板と、前記チャネル領域より上に配置されたトンネル誘電体構造102であって、低いホールトンネリング障壁高さを有する少なくとも1つの層を備えたトンネル誘電体構造と、前記トンネル誘電体構造より上に配置された電荷蓄積層130と、前記電荷蓄積層より上に配置された絶縁層140と、前記絶縁層より上に配置されたゲート電極150とを有するメモリセル、該メモリセルのアレイ及び操作方法と共に開示する。

(もっと読む)

不揮発性半導体記憶装置

【課題】高性能な書きこみ消去特性を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板のp型ウエル2上にゲート絶縁膜6を介して選択ゲート18が形成され、p型ウエル2上に酸化シリコン膜15a、窒化シリコン膜15bおよび酸化シリコン膜15cからなる積層膜15を介してメモリゲート17が形成される。メモリゲート17は、積層膜15を介して選択ゲート18に隣接する。p型ウエル2の選択ゲート18およびメモリゲート17の両側の領域には、ソース、ドレインとしてのn型の不純物拡散層20,21が形成されている。不純物拡散層20,21の間に位置するチャネル領域のうち、選択ゲート18により制御され得る領域51とメモリゲート17により制御され得る領域52とにおける不純物の電荷密度が異なる。

(もっと読む)

不揮発性半導体記憶装置とその駆動方法および電子機器

【課題】周辺回路の増大を極力抑えつつ、データディスターブを改善する不揮発性半導体記憶装置を提供する。

【解決手段】第1ボディ領域100上に不純物拡散層104,124を、第1不純物拡散層104上に第2ボディ領域106を形成する。第1不純物拡散層104はメモリトランジスタMTのドレイン領域と選択トランジスタSTのソース領域、第1不純物拡散層124は選択トランジスタSTのドレイン領域をなす。第2ボディ領域106と第1不純物拡散層104に跨るように第2ボディ領域106上にメモリトランジスタMTのゲート部G_MTをMONOS構造で形成する。第1不純物拡散層104、第1ボディ領域100、第1不純物拡散層124に跨るように選択トランジスタSTのゲート部G_STをMOS型構造で形成する。両トランジスタMT,STは、バックゲートとなるボディ領域が電気的に分離される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリセルを有する半導体装置において、メモリ周辺回路の信頼性を向上させることのできる技術を提供する。

【解決手段】メモリ周辺回路領域の高圧系nMISおよび高圧系pMISのゲート絶縁膜14を、半導体基板1の主面上に順次積層された下層の絶縁膜11b、電荷蓄積層CSLおよび上層の絶縁膜11tにより構成し、続いて上層の絶縁膜11t上に積層されたn型の導電膜により高圧系nMISのゲート電極GHnまたは高圧系pMISのゲート電極GHpを構成する。メモリ周辺回路領域の低圧系nMISおよび低圧系pMISのゲート絶縁膜8を、半導体基板1の主面上に形成された酸化シリコン膜により構成する。

(もっと読む)

不揮発性メモリー装置

【課題】MONOS型不揮発性メモリーの消去を行う場合には、FN電流を用いた消去法を用いる場合でも、バンド間トンネリングホットホールを用いた消去を行う場合においても、負電源を用いることが必要となる。負電源を用いるためには別途電気的に分離できるよう配線パターンを設計する必要があり、配線パターンに制約が加わるという課題がある。

【解決手段】接合深さとして、10nm以上500nm以下の値となるようドレイン領域203D、ソース領域203Sを形成した。ドレイン領域203D、ソース領域203Sでの電界強度が大きくとれることから、バンド間トンネリングホットホールをゲート電極206を接地し、ドレイン領域203Dに5[V]程度の電位を供給することで発生させることができ、負電源を用いることなく消去を行うことが可能となる。

(もっと読む)

不揮発性メモリー装置および不揮発性メモリー装置の製造方法

【課題】MONOS型不揮発性メモリー素子の消去を行う場合として、バンド間トンネリングホットホールによる消去方法を用いることが好適である。この場合、消去できる領域がドレイン領域近傍に制限されるため、FN電流を用いた消去動作よりも消去できる領域が狭く、特にソース領域近傍側の電荷を消去しきれないという課題があり、特に製造工程で帯電したソース領域近傍の電荷を消去することが困難になるという課題がある。

【解決手段】ソース領域203Sに5V程度の電圧をかけ、ドレイン領域203D、ゲート電極206を接地する動作と、ドレイン領域203Dに5V程度の電圧をかけ、ソース領域203S、ゲート電極206を接地する動作とを行う。ソース領域203S近傍に位置するゲート絶縁層204の電荷も消去することが可能となり、製造工程で帯電したソース領域近傍の電荷を消去することが可能となる。

(もっと読む)

不揮発性記憶装置を含む半導体装置

【課題】 動作速度の向上および周辺回路面積の縮小化が達成可能である複数の不揮発性記憶装置を含む半導体装置を提供する。

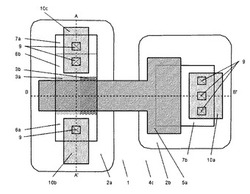

【解決手段】 本発明の半導体装置は、行方向および該行方向と交差する列方向に配置された複数の不揮発性記憶装置100を含む。不揮発性記憶装置100は、半導体層10のチャネル領域上に設けられたゲート絶縁層22と、ゲート絶縁層22上に設けられたゲート導電層14と、第1導電型の第1および第2不純物領域34,24と、ビット導電層80とを含む。ビット導電層80は、i行[j+1]列に配置されたメモリセル100の第2不純物領域24と、[i+1]行[j+1]列に配置されたメモリセル100の第1不純物領域34とを電気的に接続する。電荷捕捉層22bのうちゲート導電層14の一方の端部近傍に電荷蓄積領域を有し、他方の端部近傍には電荷蓄積領域を有さない。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】工程数を削減した不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】浮遊ゲート電極18からキャップ層30まで、およびゲート電極24からキャップ層30までをマスクとして、半導体基板11の上方から、メモリセルアレイ領域に不純物を自己整合的にイオン注入し、浮遊ゲート電極18、およびゲート電極24をそれぞれ挟むように第1不純物拡散層21を形成する工程と、半導体基板11の斜め上方から、ゲート電極24を挟むように形成された第1不純物拡散層21のうち、セルトランジスタ12と反対側に形成されている第1不純物拡散層21aに不純物を選択的にイオン注入し、第1不純物拡散層21aを、不純物の濃度が第1不純物拡散層21より高い第2不純物拡散層22に転換する工程と、を具備する。

(もっと読む)

不揮発性半導体記憶装置ならびにその駆動方法、動作方法および製造方法

【課題】不揮発性半導体記憶装置の駆動時において、書き戻しに駆動電流が大きい、書き戻し時間が長い、チャネルコンダクタンスの劣化があるなどの課題があった。

【解決手段】第1導電型のチャネル領域を介して対向する第2導電型の第1、第2の拡散層2aa,2bbと、第1導電型のチャネル領域上の2層ゲート電極とを備えたトランジスタに対して、チャネル領域と一方の拡散層を第1の電圧レベルに設定し、拡散層の他方を第2の電圧レベルに設定し、コントロールゲート6を第1または第3の電圧レベルに設定し、第1の電圧レベルと第2の電圧レベルとの電位差が第1の電圧レベルと第3の電圧レベルとの電位差よりも絶対値において大きく設定し、チャネル電流が流れるトランジスタに対してそのチャネル領域を流れる電荷の一部をフローティングゲート4に注入するようにした。

(もっと読む)

不揮発性半導体メモリデバイス、その製造方法および動作方法

【課題】書き換え時の閾値電圧変動を抑制し、かつ、データ保持特性低下を防止する。

【解決手段】メモリトランジスタMが、シリコン基板11に形成されているソース領域17S等と、これと離れて形成されているドレイン領域17D等と、両領域間のチャネル形成領域11Aを少なくとも覆って形成されているボトム絶縁膜12Aと、離散化された電荷蓄積手段(キャリアトラップ)を含む電荷蓄積膜12Bと、トップ絶縁膜12Cと、ゲート電極13と、を有する。ボトム絶縁膜12Aは、チャネル形成領域11Aにおけるシリコン基板11とのバリアハイトが、SiO2とSiとのバリアハイトより低いSiONから形成され、このSiONとSiとの界面は、窒素の組成比が9%以上である。

(もっと読む)

1 - 20 / 69

[ Back to top ]