Fターム[5F083FZ00]の内容

半導体メモリ (164,393) | その他の半導体メモリ (2,669)

Fターム[5F083FZ00]の下位に属するFターム

単一電子メモリ (25)

走査型プローブ顕微鏡(SPM)応用メモリ (23)

電荷転送型メモリ

光集積回路用メモリ(PHBメモリを含む) (12)

バイポーラメモリ (7)

疑似SRAM

有機物半導体メモリ (298)

超電導メモリ (2)

その他の半導体メモリ (2,300)

Fターム[5F083FZ00]に分類される特許

1 - 2 / 2

圧電セラミックス膜形成用組成物、圧電素子の製造方法及び液体噴射ヘッドの製造方法

【課題】環境負荷が小さく且つクラックの発生が抑制された圧電セラミックス膜を形成することができる圧電セラミックス膜形成用組成物、圧電素子の製造方法及び液体噴射ヘッドの製造方法を提供する。

【解決手段】圧電セラミックス膜形成用組成物は、ビスマス及び鉄を含む金属錯体混合物と、エチルセルロースと、ターピネオールと、溶媒と、を含む。高分子材料であるエチルセルロースと、沸点の高いターピネオールとを含むことにより、圧電セラミックス膜を製造する工程において発生する残留応力を低減させることができる。これにより、鉄酸ビスマス系の圧電材料からなりクラックの発生が抑制された圧電セラミックス膜を形成することができるものとなる。また、鉛の含有量を抑えられるため、環境への負荷を低減することができる。

(もっと読む)

半導体メモリ素子の製造方法

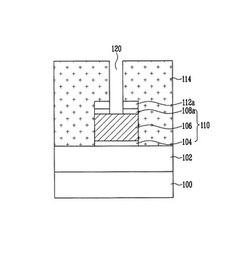

【課題】エッチング方法を変化させてビットラインの損失を防止する半導体メモリ素子の製造方法を提供する。

【解決手段】第1の絶縁膜102上に金属配線層とエッチング停止膜112を形成する。金属配線層とエッチング停止膜112をパターニングして金属配線110を形成する。そして、第1の絶縁膜102上に第2の絶縁膜114を形成し、エッチング停止膜112が露出されるように第1のエッチングガスで第2の絶縁膜114の一部をエッチングする。続いて金属配線110が露出されるように第2のエッチングガスでエッチング停止膜112を除去する。それによって、たとえば比抵抗が低いアルミニウムを金属膜106として用い、そのアルミニウム金属膜106によるビットラインにビアホール120を連結する際、エッチングガスを変化させるだけで別途に追加膜を形成せずともアルミニウム金属膜106のエッチング損傷を抑制できる。

(もっと読む)

1 - 2 / 2

[ Back to top ]