Fターム[5F083FZ07]の内容

半導体メモリ (164,393) | その他の半導体メモリ (2,669) | 有機物半導体メモリ (298)

Fターム[5F083FZ07]に分類される特許

1 - 20 / 298

半導体装置

分子メモリ装置の製造方法

【課題】メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置の製造方法を提供する。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、前記配線層上に犠牲膜を形成する工程と、前記犠牲膜上に第2方向に延びる複数本の第1絶縁部材を形成する工程と、前記第1絶縁部材の側面上に前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、隣り合う前記第1絶縁部材間であって前記第2配線間に複数本の第2絶縁部材を前記配線層に接するように形成する工程と、前記犠牲膜を除去することによりギャップを形成する工程と、前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し他方には結合しない分子材料を形成する工程と、を備える。

(もっと読む)

有機分子メモリおよび有機分子メモリ用有機分子

【課題】メモリ保持特性に優れた有機分子メモリを提供する。

【解決手段】実施の形態の有機分子メモリは、第1の導電層と、第2の導電層と、第1の導電層と第2の導電層との間に設けられ、分子軸に沿ってπ電子系が拡がっている分子骨格を持つ分子系において、(I)分子の最高被占軌道(HOMO)と最低空軌道(LUMO)のうちいずれか一方が分子軸にそって非局在化し、他方が分子軸に対して局在化している、(II)分子の最高被占軌道(HOMO)エネルギー準位が−5.75eV以上の値を持つ、を同時に満たす分子群より選ばれる有機分子を含む有機分子層と、を備える。

(もっと読む)

半導体装置

【課題】有機化合物を含む層を有する素子が設けられたフレキシブルな記憶装置及び半導

体装置を歩留まり高く作製する。また、信頼性の高いフレキシブルな記憶装置及び半導体

装置を歩留まり高く作製する。

【解決手段】剥離層を有する基板上に素子層及び素子層を封止する絶縁層を有する積層体

を形成し、剥離層から積層体を剥離してフレキシブルな記憶装置及び半導体装置を作製す

る方法であって、素子層において第1の電極層及び第2の電極層からなる一対の電極間に

有機化合物を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金

層で形成する。また、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物

を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金層で形成さ

れるフレキシブルな記憶装置及び半導体装置である。

(もっと読む)

記憶装置及びその製造方法

【課題】信頼性が高い記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る記憶装置は、下部電極層と、前記下部電極層上に設けられた絶縁性の芯材層と、前記芯材層上に設けられ、前記芯材層の側面上には設けられていない上部電極層と、前記芯材層の側面上に設けられ、前記下部電極層及び前記上部電極層に接し、複数の微小導電体が隙間を介して集合した抵抗変化層と、を備える。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

電子機器

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

半導体装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

コバルト薄膜およびその形成方法ならびにナノ接合素子およびその製造方法ならびに配線およびその形成方法

【課題】厚さが35nm以下でも十分に高い保磁力および角型比を有する磁性のコバルト薄膜を得ることができるコバルト薄膜の形成方法およびこの方法により形成したコバルト薄膜を用いたナノ接合素子を提供する。

【解決手段】ポリエチレンナフタレート基板11上に真空蒸着法などによりコバルト薄膜12を35nm以下の厚さに成膜する。こうしてポリエチレンナフタレート基板11上にコバルト薄膜12を成膜した積層体を二つ用い、これらの二つの積層体をそれらのコバルト薄膜12のエッジ同士が、必要に応じて有機分子を挟んで、互いに対向するように交差させて接合することによりナノ接合素子を構成する。このナノ接合素子により不揮発性メモリや磁気抵抗効果素子を構成する。ポリエチレンナフタレート基板11の代わりに、少なくとも一主面がSiO2 からなる基板、例えば石英基板を用いてもよい。

(もっと読む)

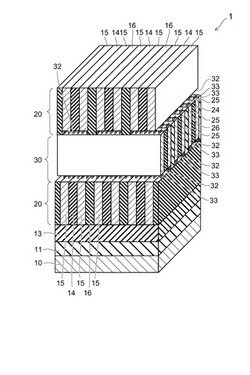

分子メモリ装置の製造方法

【課題】LSIプロセスによって製造可能な分子メモリ装置の製造方法を提供する。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、前記第1配線層上に犠牲膜を形成する工程と、前記第1配線層上に、前記第1方向に対して交差した第2方向に延び、前記犠牲膜とは異なる絶縁材料によって形成された複数本の芯材を形成する工程と、前記芯材の側面上に第2配線を形成する工程と、前記犠牲膜における前記第2配線の直下域に相当する部分を除去する工程と、前記第1配線と前記第2配線との間に、メモリ材料となる高分子を埋め込む工程と、前記芯材間であって前記第2配線間の空間に絶縁部材を埋め込む工程と、を備える。

(もっと読む)

デバイス製造方法

【課題】 ノズルから吐出された液滴に変質等が生じないように吐出空間の雰囲気を置換することが可能なデバイス製造方法を提供する。

【解決手段】 デバイスの製造方法は、基板をチャンバ内に搬入して載置台に載置する工程と、待機位置において封止部材により液滴吐出ノズルを隔離した状態で、チャンバの内部を減圧する減圧工程と、ガス供給機構からチャンバ内にパージガスを導入してチャンバ内部の雰囲気を置換するとともに大気圧状態に戻す雰囲気置換工程と、封止部材による液滴吐出ノズルの隔離を解除し、液滴吐出ノズルを吐出位置に移動させて被処理体へ向けて前記液滴を吐出する吐出工程とを含む。

(もっと読む)

集積装置

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含み、かつ積層された酸化物半導体層の間に混合領域を有する酸化物半導体積層を用いる。

(もっと読む)

受動マトリクス・アドレス指定可能素子の読み取り方法並びにその方法を実施するための素子

【課題】個別にアドレス指定可能なセルを具備した受動マトリクス・アドレス指定可能素子の読み取りの方法を提供する。

【解決手段】セルはデータを各セルの中で2つの分極状態の1つの形式で格納し、セル内の分極状態は直交する電極マトリクスの形でワードおよびビット・ラインを形成する電極を経由してアドレス指定して書き込みおよび読み取りが行われ、セルがワードおよびビット・ラインの間の交差部内またはその部分に具備され、電圧パルス・プロトコルが使用され、それに基づいて全てのワードおよびビット・ライン上の電位が時間を調整される。読み取り中にはワード・ラインが電圧を与えることでアクティブ化され、この電圧は電圧に対応する全ての交差ビット・ライン上の電位に比例し、このアクティブ・ワード・ラインに接続されたセル内に格納されたデータは、そのセルの電荷値を検出装置で検出して決定される。

(もっと読む)

半導体記憶装置

【課題】TFTなどのトランジスタ特性がばらつく状況や、RF回路から電源が供給され

電源が安定しない状況で、SRAMを作製する場合、従来の1つのメモリセルに6つのト

ランジスタの構成では読み出し時にメモリセルが保持する値が書き換わる誤書き込みが発

生してしまう。

【解決手段】SRAMのメモリセルは、書き込みの回路と読み出しの回路を分離する事に

より、SRAMの誤書き込みを防ぎ、安定した動作を行うことを可能にする。また、書き

込みのタイミングを考慮する事により、誤書き込みを起こさず、より確実に書き込みの動

作を行うことが可能なSRAMを提供する。

(もっと読む)

電解質メモリ素子

【課題】 低電圧駆動可能で低消費電力型の不揮発性メモリ素子およびその製造方法を提供する。

【解決手段】 本発明のある態様においては、対向配置された第1基体10Aおよび第2基体20Aと、第1基体および第2基体に挟まれる電解質層30とを備えるメモリ素子1000が提供される。第1基体の基板12の一の面12Sの上には、二酸化バナジウムを主成分とするメモリ層100Aが形成され、メモリ層に接している第1電極部110Aと第2電極部120Aとを有している。第2基体の対向基板22は、第1基体に対向する面の上に第3電極部230Aを有している。そして電解質層30は、第1電極部と第2電極部との間においてメモリ層に近接している。本発明のある態様においては、一方の基体に第1〜第3電極部とメモリ層とが形成された別の典型的なメモリ素子2000も提供される。

(もっと読む)

電気化学素子および電気化学素子を用いた相補型回路

【課題】従来の電気化学素子とは逆極性でオンオフ動作を行うイオン移動型電気化学素子を提供する。この素子を従来型の電気化学素子とを組合せれば、低消費電力の相補型回路を構成できる。

【解決手段】イオン拡散材料として使用する酸化タンタルを挟んで一方にゲート電極を配置し、もう一方に絶縁物材料によって隔てられたソース電極とドレイン電極を配置する。このとき、ソース・ドレイン電極間の電気的接続を実現するゲート電圧(オン電圧)がオフ状態を実現するゲート電圧(オフ電圧)よりも低い電気化学素子が得られる。

(もっと読む)

1 - 20 / 298

[ Back to top ]