Fターム[5F083FZ01]の内容

半導体メモリ (164,393) | その他の半導体メモリ (2,669) | 単一電子メモリ (25)

Fターム[5F083FZ01]に分類される特許

1 - 20 / 25

メモリ装置

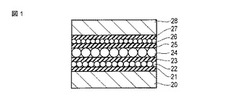

【課題】配線電極間の双方向の電流値、書き込み及び消去の電圧値、および記憶保持時間が制御容易なメモリ装置を提供する。

【解決手段】微結晶である第1の導電性微粒子を含む微結晶層22と、微結晶層22を挟むトンネル絶縁膜21、23とを有する第1の二重トンネル接合構造と、微結晶である第2の導電性微粒子を含む微結晶層26と、微結晶層26を挟むトンネル絶縁膜25、27とを有する第2の二重トンネル接合構造と、第1の二重トンネル接合構造と第2の二重トンネル接合構造との間に配置され、情報電荷を蓄積する電荷蓄積層と、第1の二重トンネル接合構造、電荷蓄積層、及び第2の二重トンネル接合構造を挟む第1、第2の導電層とを備える。第1の導電性微粒子の平均粒径は、第2の導電性微粒子の平均粒径と異なっている。

(もっと読む)

メモリ用シフトレジスタ及びその製造方法

【課題】大容量で、信頼性が高く、少ない工程数で製造可能なメモリ用シフトレジスタを提供する。

【解決手段】一の実施形態によれば、メモリ用シフトレジスタは、基板の主面に平行な第1方向に延び、前記第1方向に垂直な第2方向に向かい合う第1及び第2の制御電極を備える。さらに、前記レジスタは、前記第1及び第2の制御電極間において、前記第1の制御電極側に一列に設けられた複数の第1の浮遊電極を備える。さらに、前記レジスタは、前記第1及び第2の制御電極間において、前記第2の制御電極側に一列に設けられた複数の第2の浮遊電極を備える。さらに、前記第1及び第2の浮遊電極の各々は、前記第1方向に垂直な平面に対し、鏡面非対称な平面形状を有する。

(もっと読む)

微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子

【課題】10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能な微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子を提供すること。

【解決手段】本発明の微細構造物の製造方法は、トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、を含むことを特徴とする。

(もっと読む)

半導体メモリ

【課題】 本発明の実施形態によれば、信頼性の高い半導体メモリを提供することができる。

【解決手段】 半導体メモリは、半導体基板のチャネル領域上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成された電荷蓄積膜と、前記電荷蓄積膜上に形成されたブロック絶縁膜と、ブロック絶縁膜上に形成されたゲート電極とを備え、トンネル絶縁膜内にはクーロンブロッケイド条件を満たす導電性微粒子を含む微粒子層がある。

(もっと読む)

メモリ素子

【課題】カーボンナノピーポッドを用いたメモリ素子の提供。

【解決手段】メモリ素子1は、フラーレン分子を内包した単層カーボンナノチューブからなるカーボンナノピーポッド13を有し、前記カーボンナノピーポッド13が、バックゲート電極11上に積層された絶縁層121上に載置されると共に、所定の距離離間して設けられたソース電極14a及びドレイン電極14bに接続され、前記フラーレン分子が、メモリ情報を保持するメモリセルとなるように構成されている。

(もっと読む)

シリコンドット形成方法及びシリコンドット形成装置

【課題】低温で基板上に直接粒径の揃ったシリコンドットを均一な密度分布で形成する方法及び装置を提供する。

【解決手段】シリコンスパッタターゲット30と基体Sを配置したチャンバ1内に水素ガスを導入し、該ガスに高周波電力を印加してチャンバ1内に、プラズマ発光において波長288nmにおけるシリコン原子の発光強度Si(288nm) と波長484nmにおける水素原子の発光強度Hβとの比〔Si(288nm) /Hβ〕が10.0以下であるプラズマを発生させ、該プラズマでターゲット30をケミカルスパッタリングして500℃以下の低温で基体上に直接、粒径が20nm以下のシリコンドットを形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】安定した均一性で量産可能であるとともに、それぞれがメモリセルを構成する量子ドット素子を高密度で集積した半導体記憶装置を提供する。

【解決手段】半導体記憶装置1は、SOI基板11と、量子ドット21と、インターポリ絶縁膜27と、ラインパターン29と、層間絶縁膜301と、ビット線31とを備える。量子ドット21は、トンネル酸化膜13を介してSOI基板11上に多結晶シリコンで形成されて電荷蓄積層をなす。ラインパターン29は、インターポリ絶縁膜27上で、多結晶シリコンで形成されてコントロールゲート(ワード線)をなす。量子ドット21は、ビット線31に直列に接続される。量子ドット21の4つの側壁と、ラインパターン29のビット線に平行な方向における側壁は、熱酸化膜33で覆われている。量子ドット21a〜21dを一単位として、間隔S4だけ離隔するように反復形成される。

(もっと読む)

メモリデバイス

【課題】書込、読み出し、消去時間を改善した、トンネル障壁構造を有するメモリデバイスを提供する。

【解決手段】メモリデバイスは、制御電極9からトンネル障壁構造2を通り抜けて電荷を書き込むメモリノード1を有する。この蓄積された電荷はソース/ドレイン経路4の伝導性に影響を与え、この経路の伝導性をモニターすることによりデータが読み出せる。電荷障壁構造は多重トンネル障壁構造により構成される。この障壁構造は、メモリノードを形成するシリコンの多結晶層1を被覆する、厚さ3nmのポリシリコン層16と厚さ1nmのSi3N4層15を交互に積層したものからなる。ショットキ障壁構造、および電気絶縁マトリクス内に分散された、メモリノードとして機能する伝導性のナノスケール伝導島30,36,44を含む他の障壁構造2も開示されている。

(もっと読む)

半導体記憶素子およびその製造方法

【課題】安定した均一性で量産可能な半導体記憶素子を提供する。

【解決手段】側壁マスクパターンが互いに交差する方向に側壁マスク加工を2度行い、その交差点を利用して量子ドットを形成する。

(もっと読む)

負性抵抗素子およびその製造方法ならびに単電子トンネル素子およびその製造方法ならびに光センサおよびその製造方法ならびに機能素子およびその製造方法

【課題】簡単なプロセスにより低コストで製造することができ、基板選択性も高く、常温を含むより高温で動作可能でしかもノイズにも強い負性抵抗素子およびその製造方法を提供する。

【解決手段】基板11上にゲート絶縁膜12を形成し、その上にZnOなどの酸化物半導体から成る複数のナノドット13aが一面内において二重ショットキー障壁13bを介して互いに接合した多重ナノドット構造体13を形成し、その上にソース電極14およびドレイン電極15を形成することにより、MOSFET構造のトンネル負性抵抗素子を構成する。ナノドット13aの径は60nm以下または20nm以下にする。このトンネル負性抵抗素子を単電子トランジスタ、単電子ポンプ、単電子メモリなどとして用いる。

(もっと読む)

ナノ結晶を有するメモリ素子及びその製造方法

【課題】ナノ結晶を有するメモリ素子及びその製造方法を提供する。

【解決手段】基板と、基板内部に形成され、互いに離隔されて位置するソース領域及びドレイン領域と、基板表面に形成され、ソース領域及びドレイン領域を連結し、複数個のナノ結晶を有するメモリセルと、メモリセル上に形成される制御ゲートとを具備し、メモリセルが、基板上に形成される第1トンネリング酸化物層と、第1トンネリング酸化物層上に形成される第2トンネリング酸化物層と、第2トンネリング酸化物層上に形成される複数個のナノ結晶を有する制御酸化物層とを具備することを特徴とするメモリ素子である。

【効果】これにより、静電気的引力を与えるためのアミノシラン基を導入できる親水性の第2トンネリング酸化物層を具備することにより、ナノ結晶の単一層配列が可能であり、素子特性の制御が可能となり、一層向上した素子特性を示すメモリ素子を提供することが可能である。

(もっと読む)

単一電荷トンネル素子

【課題】不揮発性メモリ素子としても使用可能な、単一電荷トンネル素子、特に単一電子トランジスタ、を提供する。

【解決手段】強磁性物質から成る単一電荷トンネル素子を従来のようにゲート電圧の印加により電気モードにおいて制御するのみならず、回転する配向磁場の印加により磁気モードにおいても制御する。即ち、該配向磁場の印加により該強磁性物質の化学ポテンシャルが変化し、クーロンブロッケード異方性磁気抵抗効果が生じる。その結果として得られる該素子の抵抗値とその変化を、論理的な1,0の書込み信号と、その切り替えに用いる。該磁気モードのヒステリシス性により、不揮発性メモリ効果が発現される。

(もっと読む)

電子装置、電子装置の製造方法、電子回路及び電子機器

【課題】 特性を安定にでき、製造コストが安価で、高集積化を行い易く、また、効果的に消費電力の低減を行うことができる電子装置とその製造方法を提供すること。

【解決手段】 電子装置は、絶縁体101の中に、金属で形成された第1領域102及び第2領域103と、この第1領域102と第2領域103で挟まれた第3領域104を備える。この第3領域は、第1及び第2領域102,103を形成する金属元素と同じ金属元素で形成されて、直径が20nm以下の微粒子を有する。第1領域102及び第2領域103は、第3領域104よりも、金属濃度が高くて電気抵抗が小さい。第1領域102と第2領域103とに電圧が印加されて、第3領域104を単一の電荷がトンネルする。第1領域102と、第2領域103と、第3領域104とは、互いに同じ金属元素を含むので、互いの境界に形成される障壁を安定にできる。

(もっと読む)

能動素子、能動素子の製造方法および能動素子の製造装置

【課題】 消費電力が格段に小さく、かつ、寸法が格段に小さい能動素子およびその製造方法およびその製造装置を提供すること。

【解決手段】 基板101上にメタル工程により、第1電極102および第2電極103を形成する。上記第1電極102は、第2電極103に略平行かつ第2電極103に対向するように配置する。第1電極102と第2電極103との間を、現存する加工技術の最小加工寸法で形成する。第1,第2電極102,103に所定の電位を印加した状態で、金属イオン等を矢印aに示す方向に注入する。このようにして、基板101上にナノワイヤー構造104を作製する。

(もっと読む)

半導体装置、半導体装置の製造方法、セルアレイ及びセルアレイの製造方法

【課題】 スイッチ機能が十分に得られ、常温においても十分にスイッチ動作ができ、微細化を図ることができるスイッチング素子を提供すること。

【解決手段】 基板101上に形成されたゲート絶縁膜102上に、第2絶縁膜105で隔てられた第1電極103と第2電極104を形成する。第1電極103は、ゲート絶縁膜102の表面に接する側の部分が鋭角断面を有するように、側面が傾斜している。ゲート絶縁膜102中に、20nm以下の直径を有すると共に、第1電極3と第2絶縁膜105との境界が含まれる平面と略同一の平面上に配列された金属微粒子106を形成する。第1絶縁膜2中の金属微粒子6の数を、第1絶縁膜2の膜厚と、第1絶縁膜2への金属元素の注入及びアニール条件とで制御できるので、微細加工の最小加工寸法の制約を受けない。また、ゲート長を、ゲート絶縁膜102の厚みによって設定できるので、微細加工の最小加工寸法の制約を受けない。

(もっと読む)

ビットレジスターリング層を有する半導体メモリ装置及びその駆動方法

半導体メモリ装置は、データを貯蔵するための複数個のメモリセルを有するメモリ層と、前記メモリセルが不良かどうかに関する状態情報を記録するための少なくとも一つのビットレジスターリング層と、を含む。前記メモリ層は、分子メモリ、カーボンナノチューブメモリ、原子メモリ、シングルエレクトロンメモリ、特に化学的ボトムアップ方式で製造されるメモリなどのようなナノメータースケールメモリ装置とすることができる。 (もっと読む)

記憶装置及びその製造方法

【課題】 製造が容易で外乱の影響を受け難い高集積記憶装置を安価に実現する。

【解決手段】 電極間に配置した導電性可動体の移動を利用した記憶装置であって、基板100上に平行配置された複数本の行線111と、行線111と交差するように平行配置され、且つ行線111と間隙を介して対向配置された複数本の列線121と、行線111に隣接する領域と列線121との間に設けられ、最上部が列線121に接触し最下部が行線111と離間して設けられた半導体膜114と、行線111と列線121との交差部にそれぞれ配置され、行線111とそれに隣接する半導体膜114とを電気的に接続する導電性の可動体130とを備えた。

(もっと読む)

多値記憶回路およびその駆動方法

【課題】従来よりも少ない素子数で多値記憶回路の入力と出力とを分離する。

【解決手段】単電子トランジスタ1のドレイン電極Dを電界効果トランジスタ2のソース電極に接続し、電界効果トランジスタ2のドレイン電極を負荷素子3の一端に接続し、負荷素子3の他端を電源端子5に接続し、単電子トランジスタ1のソース電極Sを接地端子6に接続する。また、単電子トランジスタ1の第1のゲート電極Gを電界効果トランジスタ2と負荷素子3との接続点に接続し、さらにこの接続点を出力端子8に接続する。また、単電子トランジスタ1に新たに第2のゲート電極Ginを設け、この第2のゲート電極Ginを入力端子7に接続する。さらに、出力端子8と接地端子6との間に蓄積容量9を接続する。立ち上がり時間と立ち下がり時間とが異なる単極性または双極性の電圧パルスを入力端子7に与えて、多値記憶回路に記憶されたデータ値を書き換える。

(もっと読む)

半導体装置およびその製造方法

【課題】量子ドット体として機能する微粒子の酸化がより確実に抑制された半導体装置およびその製造方法を提供する。

【解決手段】半導体装置20は、半導体基板1と、半導体基板1上に設けられたトンネル絶縁膜3と、トンネル絶縁膜3上に間隔を空けて配置された酸化数が増加しない酸化物半導体からなる微粒子4と、トンネル絶縁膜3上に設けられ、微粒子4を埋め込むSiO2からなる絶縁膜5と、絶縁膜5上に設けられたコントロールゲート6とを備えている。量子ドットとして機能する微粒子4が製造工程中あるいは製造後に酸化されて絶縁体となることがないので、半導体装置は歩留まり良く製造され、且つ信頼性が向上している。

(もっと読む)

半導体メモリ

【課題】 情報の保持時間を確保できる半導体メモリを提供する。

【解決手段】 半導体メモリは、第1面を有する半導体基板1を有する。第1絶縁膜4aは、第1面上に設けられ、第1面と離れた位置に第1面内の第1方向に広がりを持つ溝11を有する。第2絶縁膜4bは、溝の開口を塞ぐように第1絶縁膜上に形成される。複数の微粒子12が、溝内に設けられる。ゲート電極G1は、溝の上方において第2絶縁膜上に設けられる。チャネル領域は、溝の下方の半導体基板の表面に設けられ、溝の第1方向における長さより短い第1方向における長さを有する。1対のソース/ドレイン領域S/Dが、チャネル領域を挟むように半導体基板の表面に設けられる。

(もっと読む)

1 - 20 / 25

[ Back to top ]