Fターム[5F083GA10]の内容

Fターム[5F083GA10]に分類される特許

1,161 - 1,175 / 1,175

不揮発性メモリ

【課題】 対向する電極間に電気抵抗値が変化する金属酸化物を設け、低消費電力で駆動する低コスト、大記憶容量の低クロストークの特に携帯用機器のメモリとして最適な不揮発性メモリを提供する。

【解決手段】 本発明の不揮発性メモリは、クロスポイントメモリ構造または三次元構造を有する不揮発性メモリであって、対向する電極間に電気抵抗値が変化する金属酸化物を設け、前記対向する両電極のうち少なくとも一方の電極の金属酸化物と接触する面に電界集中部を設けたものである。

(もっと読む)

不揮発性メモリとその製造方法

【課題】 対向する電極間に電気抵抗値が変化する金属酸化物を設け、低消費電力で駆動する低コスト、大記憶容量の低クロストークの特に携帯用機器のメモリとして最適な不揮発性メモリとその製造方法を提供する。

【解決手段】 本発明の不揮発性メモリの製造方法は、対向する電極間に未結晶状態又は不完全な結晶化状態の金属酸化物を設け、前記電極間に高電界エネルギーを印加することにより、発生するジュール熱のエネルギーによって結晶化した金属酸化物からなるメモリ・セル(メモリ領域)を形成する。

(もっと読む)

抵抗変化機能体およびその製造方法

この発明の抵抗変化機能体は、第1電極111と第2電極112との間に挟まれた第1物質からなる物体101と、物体101中に、第1電極111と第2電極112との間に所定の電圧を印加した前後で、第1電極111と第2電極112との間の電気抵抗を変化させるように配置された、第2物質からなる複数の微粒子102を備える。上記第1物質は第2物質に対して電気的に障壁となる。この構成によれば、第1電極111と第2電極112との間に所定の電圧を印加することにより、第2物質からなる微粒子102の状態によって電気抵抗を変化させることができる。また、簡単な構造なので、小型の抵抗変化機能体が低コストで提供される。  (もっと読む)

(もっと読む)

3次元半導体装置

【課題】3次元半導体装置において、信号伝送路の3次元配線容量を減らして消費電力を削減する。

【解決手段】半導体回路チップ30を複数枚積層し、この半導体回路チップ間の信号伝送のためのチップ間配線50を複数本備えた3次元半導体装置において、信号伝送時に信号伝送の経路となる1つのチップ間配線50のみを選択し、それ以外のチップ間配線50をチップ間配線50と信号線との間に設けたスイッチによって電気的に切り離す。これによって、配線の充放電に関わるチップ間配線容量を最小限にする。

(もっと読む)

半導体不揮発性記憶装置の製造方法

【課題】消去電圧などの動作電圧について低電圧化が可能であり、低コスト化が可能である半導体不揮発性記憶装置の製造方法を提供する。

【解決手段】電荷蓄積層を有するメモリトランジスタが接続された半導体不揮発性記憶装置の製造方法であって、ガラスあるいはプラスチックからなる絶縁性基板上にチャネル形成領域を有する半導体層を形成する工程と、前記半導体層の上層に電荷蓄積層を形成する工程と、前記電荷蓄積層の上方にコントロールゲートを形成する工程と、前記チャネル形成領域に接続するソース・ドレイン領域を形成する工程とを有し、前記メモリトランジスタとなる薄膜トランジスタを形成する。

(もっと読む)

積層型半導体メモリ装置

【課題】 3次元半導体メモリ装置において、データ転送時の充放電に必要な配線容量を減らして低消費電力化する。

【解決手段】 第1の半導体チップ上に複数積層され、バンクメモリが分割されたサブバンクが入出力ビットに対応してまとめられて配置されたメモリセルアレイチップと、前記入出力ビットの数分設けられ、前記サブバンクを対応する入出力ビットが同じとなるように前記メモリセルアレイチップをその積層方向に貫通する形態で接続するチップ間配線とを有する。

(もっと読む)

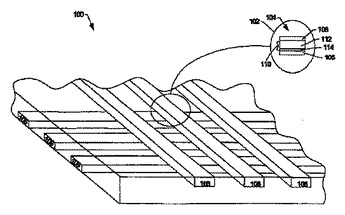

ナノワイヤによってコンタクトがとられる導電性材料の層を有する電子装置を製造する方法

本発明による電子装置(100)は、第1値と第2値との間で電気的にスイッチ可能な電気抵抗率を有するメモリ材料の層(107)を備える。メモリ材料は相変化材料でもよい。電子装置(100)は電子装置の第1端子(172)とメモリ材料の層(107)を電気的に接続する一組のナノワイヤ(NW)をさらに備え、それによって、第1端子からナノワイヤ(NW)及びメモリ材料の層(107)を介して電子装置の第2端子(272)への電流の伝導を可能にする。各ナノワイヤ(NW)は各々のコンタクト領域でメモリ材料の層(107)に電気的にコンタクトがとられる。全てのコンタクト領域ほぼ同一である。本発明による方法は、本発明による電子装置(100)を製造するのに適している。  (もっと読む)

(もっと読む)

相補型不揮発性メモリ素子、その動作方法、その製造方法、及びそれを含む論理素子、並びに半導体装置とその読み込み動作回路

【課題】 相補型不揮発性メモリ素子、その動作方法、その製造方法、及びそれを含む論理素子、並びに半導体装置とその読み込み動作回路を提供する。

【解決手段】 第1不揮発性メモリ素子と、前記第1不揮発性メモリ素子上に積層された、第1不揮発性メモリ素子と相補的関係にある第2不揮発性メモリ素子とを含む相補型不揮発性メモリ素子であって、さらに、前記第1及び第2不揮発性メモリ素子の間にボンディング材が備えられた不揮発性メモリ素子である。

(もっと読む)

不揮発性プログラマブルメモリ

【課題】

【解決手段】 メモリ(3700)が提供される。メモリは、不揮発性メモリセルアレイ(3720)を含み、各セルは、第1の書き込み電圧パルスを印加されると第1の抵抗状態から第2の抵抗状態へと切り替わるとともに第2の書き込み電圧パルスを印加されると第2の抵抗状態から第1の抵抗状態へと可逆的に切り替わる2端子メモリプラグを含む。

(もっと読む)

メモリエレメント配列を相互に接続するポリマー誘電体

ポリマー誘電体(103)を含む半導体デバイス(100)および有機半導体材料(112)と受動層(114)とを含む少なくとも1つのアクティブデバイス(104)が開示されている。導電性ポリマー(106および/または108)をさらに含む半導体デバイス(100)も開示されている。そのようなデバイスは、軽量であること、及び強固な信頼性により特徴づけられる。  (もっと読む)

(もっと読む)

表面上のレドックス活性ポリマーの製造方法

本発明は、基板上に結合されたレドックス活性ポリマーの形成のための新規な方法を提供する。ある実施形態において、該方法には、少なくとも第1反応性部位又は第1反応性基及び第2反応性部位又は第2反応性基を有するレドックス活性分子を用意する工程並びに表面をレドックス活性分子と接触させる工程が含まれ、ここで該接触は、該第1反応性部位又は第1反応性基による該表面への該レドックス活性分子の結合、そして第2反応性部位又は第2反応性基による、表面に結合したレドックス活性分子へのレドックス活性分子の結合となり、それにより、該表面に結合されたポリマーを形成する条件下で行われ、該ポリマーが、少なくとも2個の該レドックス活性分子を含む。  (もっと読む)

(もっと読む)

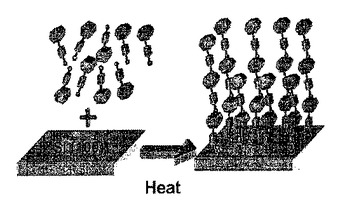

ポリマーメモリセルを形成するための導電性ポリマーのセルフアセンブル

本発明はメモリセルとして利用できる選択的導電性有機半導体(例えば、ポリマー)デバイスを提供する。導電性ポリマー(22)を含むポリマー溶液は導電性電極(26)に関してセルフアセンブルする。最短の導電性経路を実現できるように、処理はセルフアセンブルを行うことができる。方法において、導電面(26)に導電性ポリマー(23)の濃縮液を堆積し、熱と、任意に真空を与えて、導電性ポリマー(22)を有機半導体にセルフアセンブルさせる。有機半導体は、2つもしくはそれ以上の電極を有する構造を形成し、一方で各電極間のパッシブデバイスに沿って有機半導体を利用して、シングル及びマルチセルメモリデバイス内に用いられてよい。パーティションコンポーネントはメモリデバイスと一体化され、以前に形成されたセルに関連づけられた、または以前に形成されたセルの上部への付加的メモリ層の積層とそのプログラミングとを容易にする。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

メモリデバイス及びこのデバイスの使用方法ないし製造方法

2つの電極(106、206、108、204)間に制御可能な導電媒体(110)を備える2つの電極で作られるメモリセル(104)を開示する。制御可能な導電媒体(110)は、活性低導電層(112)及び受動層(114)を備える。制御可能な導電媒体(110)は、電界の印加のような外部刺激が供給されると、インピーダンスか変わる。メモリデバイス/セルの作製方法、メモリデバイス/セルの使用方法、及び、メモリテバイス/セルを含むコンピュータのようなテバイスの使用方法も開示する。  (もっと読む)

(もっと読む)

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

1,161 - 1,175 / 1,175

[ Back to top ]