Fターム[5F083GA15]の内容

Fターム[5F083GA15]に分類される特許

321 - 328 / 328

スピン注入を用いて磁気ラム素子を駆動させる方法、及び磁気ラム素子

【課題】 基板上の磁気トンネル接合構造体を有するメモリセルを備える磁気ラム素子の駆動方法を提供する。

【解決手段】 基板1上に磁気トンネル接合構造体41a、41bを有するメモリセルを備える磁気ラム素子を駆動させる方法であって、前記磁気トンネル接合構造体41a、41bを介して書込み電流パルスを印加する段階と、前記磁気トンネル接合構造体に書込み磁界パルスを印加する段階と、を含み、前記書込み磁界パルスの少なくとも一部は前記書込み電流パルスの少なくとも一部と時間的に重複することを特徴とする磁気ラム素子の駆動方法。

(もっと読む)

半導体装置

【課題】 半導体装置の性能を向上させ、製造歩留りを向上させる。

【解決手段】 メモリセル30が複数アレイ状に配置され、X方向に並ぶメモリセル30の選択ゲート電極8は選択ゲート線9によって接続され、メモリゲート電極13はメモリゲート線14によって接続される。ソース領域20を介して隣接するメモリセル30のメモリゲート電極13にそれぞれ接続されたメモリゲート線14同士は電気的に接続されていない。選択ゲート線9は、X方向に延在する第1の部分9aと、一端が第1の部分9aに接続してY方向に延在する第2の部分9bを有している。メモリゲート線14は、選択ゲート線9の側壁上に絶縁膜を介して形成され、選択ゲート線9の第2の部分9b上から素子分離領域上にかけてX方向に延在するコンタクト部14aを有し、コンタクト部14a上に形成されたコンタクトホール23dを埋めるプラグを介して配線に接続される。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】 誤書き込みを抑制しつつ、書き込み電流の低減を図る。

【解決手段】 磁気ランダムアクセスメモリは、記録層30と固定層10と記録層及び固定層間に設けられた中間非磁性層20とを有する磁気抵抗素子1を備えた磁気ランダムアクセスメモリである。記録層は、中間非磁性層上に形成された第1の強磁性層31と、第1の強磁性層上に形成された第1の非磁性層32と、第1の非磁性層上に形成され、第1の非磁性層を介して第1の強磁性層と第1の磁気結合により磁気的に結合する第2の強磁性層33と、第2の強磁性層上に形成された第2の非磁性層34と、第2の非磁性層上に形成され、第2の非磁性層を介して第2の強磁性層と第2の磁気結合により磁気的に結合する第3の強磁性層35とを具備する。第1の磁気結合が反強磁性結合であり、かつ第2の磁気結合が強磁性結合である場合、又は、第1の磁気結合が強磁性結合であり、かつ第2の磁気結合が反強磁性結合である場合のどちらかである。

(もっと読む)

半導体装置およびその製造方法

【課題】 MONOS型不揮発性半導体記憶装置の高性能化、高信頼性化を推進することのできる技術を提供する。

【解決手段】 MONOS型不揮発性メモリのメモリセル1は、コントロールゲート6を備えたコントロールトランジスタ4と、メモリゲート8を備えたメモリトランジスタ5とで構成され、それらトランジスタは、基板2の表面に形成されたドレイン拡散層23およびソース拡散層24を有している。メモリゲート8と基板2との間の電荷蓄積部である窒化シリコン膜13は、メモリゲート8のゲート長方向の長さが、メモリゲート8のゲート長より短い。

(もっと読む)

スプリットゲート型フラッシュメモリ素子及びその製造方法

【課題】ディスターバンス問題を防止できるスプリットゲート型フラッシュメモリ素子及びその製造方法を提供する。

【解決手段】バルクシリコン基板の活性領域に形成されているシリコンエピタキシャル層と、素子のソース及びドレイン間のバルクシリコン基板に形成されているディスターバンス防止用絶縁膜とを備えるスプリットゲート型フラッシュメモリ素子であり、該スプリットゲート型フラッシュメモリ素子では、ディスターバンス防止用絶縁膜は、STI形成工程を利用して形成される。

(もっと読む)

半導体装置

相変化メモリを低電圧動作および高温の動作又は放置させる場合に、記録保持信頼性を向上させること。

読み出し電圧をセット電圧およびリセット電圧以上として高速動作させ、読み出し後に読み出し前の状態を再書込みする、いわゆる破壊読出しを行う。または、複数個のセルを用いて1ビットの情報を記録する、いわゆるオアセルを用いて、高温時の動作又は放置のける信頼性を向上させる。破壊読出しおよびオアセルを用いた相変化メモリに必要な、回路構成および動作方法を用いる。

(もっと読む)

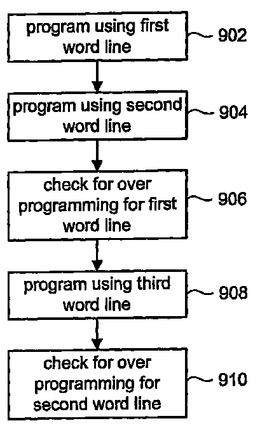

隣接するメモリセルのプログラミングの後にオーバー・プログラミングされたメモリセルを検出する技術

非揮発性半導体メモリシステム(又は他のタイプのメモリシステム)において、メモリセルは、その閾電圧を変更することによってプログラミングされる。システム内の様々なメモリセルに対するプログラミングのタイミングが異なることが原因で、いくつかのメモリセルは、オーバー・プログラミングされてしまう可能性がある。即ち、例えば、セルの閾電圧が、目的とされた値、又は、目的とされた範囲から外れてしまう可能性がある。本発明は、セルに対するプログラミングが原因で、それに隣接する行のメモリセルがオーバー・プログラミングされたか否かを判断することを含んでいる。

(もっと読む)

(もっと読む)

UVチャージングを減少するPECVDシリコンリッチ・シリコン酸化物層

メタライゼーションの前に、UV透過を低減するシリコンリッチ・シリコン酸化物層(500)をPECVDにより層間絶縁膜(300)上にたい積する。これによりVtが減少する。実施形態は、1.7から2.0のR.I.を有するUVを透過しないシリコンリッチ・シリコン酸化物層(500)をたい積するステップを含んでいる。  (もっと読む)

(もっと読む)

321 - 328 / 328

[ Back to top ]