Fターム[5F083GA15]の内容

Fターム[5F083GA15]に分類される特許

121 - 140 / 328

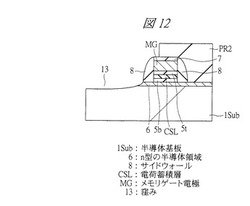

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

半導体装置

【課題】メモリブロックを含んだ半導体装置において、高速化を実現する。

【解決手段】例えば、メモリブロックMB1内に複数のメモリアレイARY[0]〜ARY[3]が備わった構成において、ARY[0]〜ARY[3]のサイズA[0]〜A[3]が段階的に異なるように形成される。具体的には、MB1への内部制御信号(例えばクロック信号CLK)の入力パッドPD_CLKや、MB1からのデータ信号の出力パッドPD_DOからの距離が、ARY[0]<ARY[1]<ARY[2]<ARY[3]の場合、例えば、A[0]>A[1]>A[2]>A[3]となるように形成される。これによって、このパッドからの距離の違いに伴う伝送遅延時間の差分を各メモリアレイの動作遅延時間の差分で相殺することができ、MB1全体として高速化が図れる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリトランジスタの特性が良好な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板11上に、それぞれ複数の絶縁膜及び電極膜14が交互に積層された積層体を設ける。電極膜14は、X方向に延びる複数本の制御ゲート電極CGに分断する。また、積層体内に、選択ゲート電極SGb、SGs、制御ゲート電極CGを貫き、一端がソース線SLに接続され、他端がビット線BLに接続されたU字ピラー30を設ける。そして、各制御ゲート電極CGは、Y方向において隣り合う2本のシリコンピラー31によって貫かれており、接続部材32によって相互に接続された2本のシリコンピラー31は、相互に異なる制御ゲート電極CGを貫いている。

(もっと読む)

不揮発性半導体記憶装置並びにその駆動方法

【課題】 注入効率が高く、書き込まれた情報が安定的に保持される不揮発性半導体記憶装置並びにその駆動方法を提供する。

【解決手段】 メモリセル1は、N型基板2上に、P型の不純物拡散領域3,4を離間して形成し、両領域間に係る前記基板上において、不純物拡散領域3に隣接して形成された第一積層部15と、不純物拡散領域4に隣接し前記第一積層部15と離間して形成された第二積層部16を備える。メモリセル1に対する書き込み処理時において、第一ゲート電極8に対し、同ゲート電極下方に位置する基板2の表面が弱反転状態となる条件の第一負電圧を印加し、第二ゲート電極10に対し、前記第一負電圧よりも絶対値の大きい第二負電圧を印加し、不純物拡散領域4に対して前記第一負電圧よりも絶対値の大きいドレイン電圧を印加し、不純物拡散領域3に対して、前記ドレイン電圧よりも電位の高いソース電圧をそれぞれ印加する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高信頼性かつ小型の不揮発性半導体記憶装置及びその製造方法を提供すること。

【解決手段】不揮発性半導体記憶装置1は、半導体基板2と、半導体基板2上に配された電荷蓄積膜5と、電荷蓄積膜5上に配された第1ゲート電極6と、半導体基板2上に配されたゲート絶縁膜7と、ゲート絶縁膜7上に配された第2ゲート電極8と、第1ゲート電極6と第2ゲート電極8間に配されたゲート間絶縁膜10,11と、を備える。第1ゲート電極6の長さL1は、第2ゲート電極8の長さL2より短い。第1ゲート電極6の上面は、曲面状又は半導体基板2に対して斜めになっていない。

(もっと読む)

半導体記憶装置

【課題】トランジスタの電圧転送能力の低下を抑制出来る半導体記憶装置を提供すること。

【解決手段】電荷蓄積層84を有する(N+1)個のメモリセルMTが直列接続されたメモリセルユニット11と、前記メモリセルMTの制御ゲート86に接続された(N+1)本のワード線WLと、電圧をワード線WLに転送する(N+1)個の転送トランジスタ43とを具備し、i番目の前記ワード線WLiに近接するM本の前記ワード線は、前記i番目のワード線WLiに前記電圧を転送する前記転送トランジスタ43−i上において、不純物拡散層112上を通過することなく、ゲート電極100上の領域を、第1層目の金属配線101によって通過する。

(もっと読む)

半導体記憶装置

【課題】チャージトラップ型フラッシュの書き込み・消去速度の向上および誤書き込みの抑制。

【解決手段】半導体記憶装置70には、半導体基板1の第1主面(表面)にメモリセルトランジスタのソース或いはドレインとなるN+層6が設けられ、メモリセルトランジスタのゲートとN+層6が交互に複数配置形成される。積層形成される電荷蓄積層3、電流遮断層4、及び制御電極5の両端部には、比誘電率が15の側壁膜7が設けられる。メモリセルトランジスタのゲートの側面部分には、底部がトンネル酸化膜2により周囲と分離され、側面が側壁膜7により周囲と分離され、上部が絶縁膜8により周囲と分離され、空気が充填された空隙部9が設けられる。絶縁膜8は、制御電極5、側壁膜7、及び空隙部9上に設けられる。

(もっと読む)

半導体記憶装置

【課題】メモリセルのコントロールゲートとして機能する電極層の電位が他領域に影響するのを抑制することができる半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置は、半導体基板11上におけるメモリセル領域及び周辺回路領域にわたって設けられ複数の電極層WL1〜WL5と複数の絶縁層24とが交互に積層された積層体と、メモリセル領域における積層体を貫通して形成されたホールの内部に設けられ積層体の積層方向に延びる半導体層21と、半導体層21と電極層WL1〜WL5との間に設けられた電荷蓄積層17と、周辺回路領域における積層体の下に設けられ、電極層WL1〜WL5に電位を転送する転送トランジスタと、転送トランジスタと最下層の電極層WL1との間に設けられ、転送トランジスタの拡散層の電位に応じたシールド電位が与えられる下部シールド配線層SL1とを備えている。

(もっと読む)

積層構造の不揮発性メモリ装置、メモリカード及び電子システム

【課題】積層構造のセルアレイと周辺回路との配置及び連結とを単純化して、集積度を高めた積層構造の不揮発性メモリ装置、メモリカード及びシステムを提供する。

【解決手段】不揮発性メモリ装置は、基板を含む。積層NANDセルアレイは、基板上に垂直に積層された複数のNANDストリングを含む少なくとも1つのNANDセットと、少なくとも1本の信号ラインとを有する。少なくとも1本の信号ラインは、少なくとも1つのNANDセットに共通結合するように、基板上に配される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】選択ゲートトランジスタの隣りに配置されたメモリセルの閾値電圧の上昇を防ぎ、選択ゲートトランジスタ間の側壁絶縁膜を薄膜化できる半導体記憶装置を提供する。

【解決手段】周辺トランジスタの第3側壁絶縁膜の膜厚は、選択ゲートトランジスタの第1側壁絶縁膜、及び隣接した選択ゲートトランジスタの第2側壁絶縁膜より膜厚が厚い。メモリセルのゲート電極MGと選択ゲートトランジスタの選択ゲート電極SG1との間隔はゲート電極MG間の間隔より広く、選択ゲート電極SG1と選択ゲートトランジスタの選択ゲート電極SG2との間隔はゲート電極MGと選択ゲート電極SG1との間隔より広い。

(もっと読む)

半導体記憶装置の製造方法

【課題】相変化メモリやReRAMなどの記憶素子と半導体デバイスの積層により構成される半導体記憶装置を製造する際、微細化に伴い素子分離幅のバラツキが書込みディスターブ耐性に大きな悪影響を与えるようになる。

【解決手段】半導体基板上に形成された被加工材料、若しくは複数の積層膜から構成される被加工材料を所望のダブルパターンニング法を用いて加工する製造方法において、パターンを形成する際、素子分離幅を規定する加工を2回行うことで解決できる

(もっと読む)

NAND型不揮発性半導体メモリ

【課題】書き込み動作時、メモリセルのチャネルを確実にカットオフさせる。

【解決手段】本発明の例に係わるNAND型不揮発性半導体メモリは、電荷蓄積層及び制御ゲート電極を有し、互いに直列接続される複数のメモリセルと、複数のメモリセルの一端とソース線との間に接続される第1のセレクトゲートトランジスタと、複数のメモリセルの他端とビット線との間に接続される第2のセレクトゲートトランジスタと、複数のメモリセルの制御ゲート電極それぞれに与える電圧を制御するドライバとを具備し、書き込み動作時、ドライバは、複数のメモリセルから選択された第1のメモリセルの制御ゲート電極に第1の電圧を印加し、第1のメモリセルからソース線側に複数個離れて並んだ3つ以上の第2のメモリセルの制御ゲート電極それぞれにメモリセルのチャネルをカットオフさせるカットオフ電圧を印加する。

(もっと読む)

半導体記憶装置の製造方法

【課題】GIDLが抑制できるメモリセルトランジスタと選択トランジスタからなるフラッシュEEPROMを製造する。

【解決手段】半導体基板の表面に対して斜め方向且つメモリセルトランジスタCT及び選択トランジスタSTのゲート長方向に対して平行する方向に不純物を導入し、水平方向に所定角度回転させた半導体基板の表面に対して斜め方向且つメモリセルトランジスタ及び選択トランジスタのゲート長方向に対して交差する方向に不純物を導入して、メモリセルトランジスタのゲート電極と選択トランジスタのゲート電極との間の基板表面における不純物濃度が、メモリセルトランジスタのゲート電極同士の間の基板表面における不純物濃度及び選択トランジスタのゲート電極同士の間の基板表面における不純物濃度よりも低くなるようにメモリセルトランジスタ及び選択トランジスタのソース、ドレイン拡散層を形成する。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明は、半導体素子及びその製造方法を提供するためのものである。

【解決手段】本発明に従う半導体素子は、半導体基板10上に形成された第1絶縁膜パターン(第1絶縁膜21)、上記第1絶縁膜パターン上に形成され、フルオリンを含む第2絶縁膜パターン(第2絶縁膜22)、上記第2絶縁膜パターン上に形成された第3絶縁膜パターン(第3絶縁膜23)、及び上記第3絶縁膜23パターン上に形成されたポリシリコン膜パターン(ポリシリコン膜30)を含む。本発明は、フラッシュメモリ素子でデータが格納される窒化膜にフルオリンを注入してキャパシタ特性に影響を与えず、且つデータリテンション及び信頼性を向上させることができる。

(もっと読む)

デプレッションタイプNANDフラッシュメモリ

【課題】デプレッションタイプNANDの読み出し時のセル閾値変動を防止する。

【解決手段】本発明の例に係わるデプレッションタイプNANDフラッシュメモリは、NANDストリングを構成する複数のデプレッションタイプFETの各々が、電荷蓄積層内の電荷量に応じて閾値が変化するトランジスタであり、隣接メモリセル記憶部が、選択されたデプレッションタイプFETのソース線側に隣接するソース線側デプレッションタイプFETの閾値を記憶する。制御回路は、読み出し時に、隣接メモリセル閾値記憶部に記憶された閾値に特定電位記憶部に記憶された特定電位を足した値を、ソース線側デプレッションタイプFETのゲート電位に加える。

(もっと読む)

EEPROM

【課題】2つのメモリトランジスタに同一のデータを確実に書き込むことができる、W(ダブル)セル方式のEEPROMを提供する。

【解決手段】半導体層には、第1不純物領域8、第2不純物領域9、第3不純物領域10、第4不純物領域11、第5不純物領域12および第6不純物領域13が形成されている。セレクトゲート15は、第1不純物領域8と第2不純物領域9との間の領域に、第1絶縁膜14を挟んで対向している。第1フローティングゲート16は、第2不純物領域9と第3不純物領域10との間の領域および第5不純物領域12に、第1絶縁膜14を挟んで対向している。第2フローティングゲート20は、第3不純物領域10と第4不純物領域11との間の領域および第6不純物領域13に、第1絶縁膜14を挟んで対向している。第5不純物領域12および第6不純物領域13は、第2不純物領域9と接続されている。

(もっと読む)

半導体装置、及びその製造方法

【課題】ショートの発生と面積の増大とを抑止しつつ、誤書き込みの防止が可能な半導体装置、及びその製造方法を提供すること

【解決手段】本発明にかかる半導体装置は、第1メモリセル領域40a内で、Y方向にソース拡散層を挟んで隣接する第1メモリセル80a及び第2メモリセル80bと、第2メモリセル領域40b内で、第2メモリセル80bのX方向側に配置された第3メモリセル80gと、第3メモリセル領域40c内で、第1メモリセル80aのX方向側に配置された第4メモリセル80hと、第1メモリセル80aと第3メモリセル80gのワードゲートWGを接続する第1接続部91aと、第2メモリセル80bと第4メモリセル80hのワードゲートWGを接続する第2接続部91bとを備え、4つのメモリセル80a、80b、80g、80hのコントロールゲートCGが、それぞれ分離して形成されているものである。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】シリコン基板11上に、それぞれ複数の絶縁膜及び電極膜14が交互に積層された積層体を設ける。電極膜14は、X方向に延びる複数本の制御ゲート電極CGに分断する。また、積層体内に、選択ゲート電極SGb、SGs、制御ゲート電極CG1〜CG4を貫き、一端がソース線SLに接続され、他端がビット線BLに接続されたU字ピラー30を設ける。そして、最上層の制御ゲート電極CG4に、他の制御ゲート電極CG1〜CG3とは異なる電位を印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 メモリセルにおけるショートチャネル効果の抑制と誤書き込みの防止の両方を実現し、不揮発性半導体記憶装置の高性能・低コスト化をはかる。

【解決手段】 半導体基板101上に複数の不揮発性メモリセルを配置して構成される不揮発性半導体記憶装置であって、メモリセルは、基板101の表面部に離間して設けられたソース・ドレイン領域120と、ソース・ドレイン領域120の直下の基板101内に設けられ、基板101よりも誘電率が低い埋め込み絶縁膜151と、ソース・ドレイン領域120の間に形成されるチャネル領域上に設けられた第1ゲート絶縁膜102と、第1ゲート絶縁膜102上に設けられた電荷蓄積層103と、電荷蓄積層103上に設けられた第2ゲート絶縁膜104と、第2ゲート絶縁膜104上に設けられた制御ゲート電極105とを備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体記憶装置(メモリ)を構成するスプリットゲート型トランジスタで発生するディスターブを抑制して、半導体装置の信頼性を向上することができる技術を提供する。

【解決手段】メモリセル領域に形成されているメモリセルには、コントロールゲート電極CGの側壁に電位障壁膜EV1、電荷蓄積膜ECおよび電位障壁膜EV2を介して、サイドウォール形状のメモリゲート電極MGが形成されている。このとき、メモリセルのコントロールゲート電極CGは矩形形状をしており、ゲート絶縁膜GOXに接する辺の端部に形成される角部が逆テーパ形状に加工されている点に特徴がある。

(もっと読む)

121 - 140 / 328

[ Back to top ]