Fターム[5F083GA15]の内容

Fターム[5F083GA15]に分類される特許

61 - 80 / 328

半導体記憶装置

【課題】微細化を図りつつ、書き込みおよび読み出し不良を抑制する。

【解決手段】メモリセルストリングで構成されるセルアレイとセルアレイの下部に配置される複数の電圧発生回路と電圧発生回路を制御する制御回路とを具備し、複数のメモリセルストリングは、一対の柱状部および一対の柱状部の下端を連結させるように形成された連結部を有する半導体層と柱状部と直交した複数のコントロールゲートと柱状部と複数のコントロールゲートとの各交差部に形成された複数のメモリセルトランジスタとを含み、制御回路は、書き込みおよび読み出し動作時に、複数の電圧発生回路のうち、複数のメモリセルストリングのうちの書き込みおよび読み出し対象のメモリストリングにノイズを与える電圧発生回路を駆動させず、複数のメモリセルストリングのうちの書き込みおよび読み出し対象のメモリストリングにノイズを与えない電圧発生回路を駆動させる。

(もっと読む)

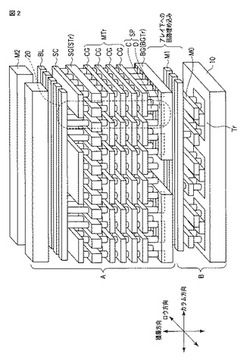

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼できる非常に小型の記憶素子を含む、3次元集積回路メモリ用の構造を低い製造コストで提供すること。

【解決手段】3次元メモリデバイスは、絶縁材料によって分離され、復号化回路を介してセンスアンプに結合可能なストリングとして配置された複数の隆起した形状スタック含む。ダイオードは、ストリングのストリング選択端部又は共通ソース選択端部のどちらか一方においてビット線構造に接続される。導電材料の帯片は、隆起した形状のスタックのサイドに側面を有する。ワード線として配列された複数の導電線は、行デコーダに結合することができ、複数の隆起した形状のスタックの上で直交して延びる。記憶素子は、スタック上の電導性帯片の側面と導電線との間の交点における界面領域の多層アレイに設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】フィールドシールド用トランジスタのゲート長を、背景技術と比べて長く取れるようにする。

【解決手段】半導体装置1は、底面並びに第1及び第2の側面を有するセル用ゲートトレンチ10と、トレンチ10より幅の狭いフィールドシールド用ゲートトレンチ11と、トレンチ10とトレンチ11の間に設けられた上部拡散層と、トレンチ10を挟んで第1の上部拡散層の反対側に設けられた第2の上部拡散層と、トレンチ11を挟んで第1の上部拡散層の反対側に設けられた第3の上部拡散層と、トレンチ10の底面に設けられた下部拡散層と、それぞれ第1及び第2の上部拡散層と電気的に接続された第1及び第2の記憶素子と、下部拡散層と電気的に接続されたビット線BLと、ゲート絶縁膜を介して第1及び第2の側面をそれぞれ覆うワード線WLと、ゲート絶縁膜を介してトレンチ11に埋め込まれたフィールドシールド用ゲート電極DWLとを備える。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】低消費電力で動作し、記憶情報の信頼性が高く、小型で軽量、安価な記憶装置と

その駆動方法を提供することを課題とする。さらに低消費電力で動作し、記憶情報の信頼

性が高く、無線通信距離の長い、小型で軽量、安価な半導体装置とその駆動方法を提供す

ることを課題とする。

【解決手段】記憶装置は、少なくとも記憶素子がマトリックス状に配置されたメモリセル

アレイと、書き込み回路とを有し、記憶素子は第一の導電層と、第二の導電層と第一の導

電層と第二の導電層とに挟まれて設けられた有機化合物層とを有し、書き込み回路は、複

数回印加する電圧を発生させる電圧発生回路と、電圧の出力時間を制御するタイミング制

御回路とを有することを特徴とする。

(もっと読む)

半導体記憶装置

【課題】誤書き込みの虞の小さい半導体記憶装置を提供する。

【解決手段】実施の形態の半導体記憶装置は、第1配線と第2配線との間に配置され且つ可変抵抗素子とスイッチング素子を直列接続してなるメモリセルを備える。可変抵抗素子は、低抵抗状態と高抵抗状態との間で抵抗値を変化させるように構成された可変抵抗層を備える。可変抵抗層は、遷移金属酸化物にて構成されている。遷移金属酸化物を構成する遷移金属に対する酸素の割合は、第1配線から第2配線へ向かう第1方向に沿って1:1から1:2までの間で変化する。

(もっと読む)

半導体記憶装置

【課題】動作信頼性を向上出来る半導体記憶装置を提供すること。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板10上に第1絶縁膜13を介在して形成された電荷蓄積層14と、電荷蓄積層14上に第2絶縁膜15を介在して形成された制御ゲート16とを具備し、制御ゲート16は、その少なくとも一部領域16−2において、その側面が外側に向かって膨らんだ形状を有し、制御ゲート16において側面が膨らみ始める部分から該制御ゲート16の頂上までの高さH1は、膨らみ始める部分より上の領域における制御ゲート16の最大幅W2_max2よりも大きい。

(もっと読む)

垂直的に集積された不揮発性記憶セルサブストリングを含む不揮発性記憶装置の形成方法、及び形成された不揮発性記憶装置

【課題】 セルの電気的特性の均一性を向上させ得る3次元不揮発性記憶装置及びその形成方法を提供する。

【解決手段】 本発明の不揮発性記憶装置の形成方法は不揮発性記憶セルが高集積化された垂直的積層を形成するための段階を含む。不揮発性記憶セルでは、直列に電気的に連結される複数の垂直サブストリングを使用して記憶セルが半導体基板上に垂直に積層される。このとき、記憶セルの垂直方向の積層は劣等に作用するメモリセルストリングが発生しないように、製造工程において補正するためにダミー記憶セルを利用する。

(もっと読む)

不揮発性半導体記憶装置

【課題】素子領域内に含まれる不純物の拡散を抑制する。

【解決手段】不揮発性半導体記憶装置は、基板101と、前記基板101内に形成されたウェル領域102とを備える。前記装置は、前記ウェル領域102内に形成された素子分離溝Tにより、前記基板の主面に平行な第1方向に延び、前記第1方向に垂直な第2方向に互いに隣接するよう区画された複数の素子領域103と、前記素子分離溝T内に埋め込まれ、前記素子領域103同士を分離する素子分離絶縁膜104とを備える。前記装置は、前記複数の素子領域103の内部に、前記複数の素子領域のそれぞれを上部素子領域103Aと下部素子領域103Bとに分断するよう形成され、前記ウェル領域102内に注入された不純物の拡散を抑制する第1の拡散抑制層111と、前記上部素子領域103Aの前記第2方向に垂直な側面に形成され、前記不純物の拡散を抑制する第2の拡散抑制層112とを備える。

(もっと読む)

半導体記憶装置

【課題】 セルアレイ面積を増大させることなく、書き込みディスターブを抑制可能な半導体記憶装置を提供する。

【解決手段】

二端子型の記憶素子Rと選択用のトランジスタQを直列に接続してなるメモリセルを複数、マトリクス状に配列させたメモリセルアレイ100と、書き換え電圧パルスを第1ビット線に印加する第1電圧印加回路101と、プリチャージ電圧を第1及び第2ビット線に印加する第2電圧印加回路102を有する半導体記憶装置であって、メモリセルの書き換え時において、予め第2電圧印加回路102がメモリセルの両端を同一電圧にプリチャージした後、第1電圧印加回路101が選択用のトランジスタに直接接続する第1ビット線を介して書き換え電圧パルスを印加するとともに、第2電圧印加回路102が記憶素子と直接接続する第2ビット線に当該プリチャージ電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】各メモリセルの書込消去特性を極力一定にできる不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルトランジスタMTは、活性領域Saが素子分離溝2によって互いに分離している。これらのメモリセルトランジスタMTは、それぞれ、活性領域Saの上面上または上方にトンネル絶縁膜3を介して電荷蓄積機能を有する電荷トラップ膜4を備えている。積層絶縁膜Bは、トンネル絶縁膜3および電荷トラップ膜4を少なくとも含んで構成され、トンネル絶縁膜3が素子分離溝2の内面に沿って形成されると共に電荷トラップ膜4がトンネル絶縁膜3の上面に沿って積層されており、素子分離溝2内の全領域に埋込まれている。

(もっと読む)

不揮発性半導体メモリ、及び不揮発性半導体メモリへの書込み方法

【課題】不揮発性半導体メモリの周辺回路を小さくし、集積回路の縮小化に寄与する。

【解決手段】p型基板10に形成され、ソース線430と接続するn型拡散層50と、p型基板10上に設けられ、ワード線400と接続するワード電極200と、p型基板10とワード電極200の間に設けられたワード絶縁層と、n型拡散層50上、及びワード電極200の側壁に設けられたトンネル絶縁層と、トンネル絶縁層上に設けられた電荷蓄積層と、電荷蓄積層上に設けられたコントロール絶縁層と、コントロール絶縁層上に設けられ、コントロール線420と接続するコントロール電極300と、を備え、制御部は、メモリ素子600に書込みを行うときに、ソース線430に正電圧を印加し、ワード線400に負電圧を印加し、かつコントロール線420に正電圧を印加する不揮発性半導体メモリ。

(もっと読む)

記憶装置、半導体装置

【課題】データの書き込み不良を抑えつつ、面積を小さく抑えることができる不揮発性の記憶装置、または当該不揮発性の記憶装置を用いた半導体装置の提供を目的の一とする。

【解決手段】不揮発性の記憶素子を有する第1の記憶部と、上記第1の記憶部へのデータの書き込みが正確に行われたかどうかを検証するベリファイ動作において、上記データを一時的に保存するための第2の記憶部(データバッファ)とを有する。そして、第2の記憶部が、記憶素子と、当該記憶素子における電荷の保持を制御するための、オフ電流またはリーク電流が極めて小さい絶縁ゲート電界効果型トランジスタとを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】電荷を蓄積可能な電荷蓄積膜を有する不揮発性メモリセルを含む半導体装置において、データ保持特性劣化を改善し、その信頼性を向上させることにある。

【解決手段】半導体基板の主面に不揮発性メモリセルを含む半導体装置であって、不揮発性メモリセルは、半導体基板上に第1絶縁膜と、導電膜と、第2絶縁膜と、電荷を蓄積可能な電荷蓄積膜とを有する。また、電荷蓄積膜上に第3絶縁膜と、第1ゲート電極と、第1絶縁膜から前記第1ゲート電極までの一連の積層膜と接するように第4絶縁膜と、第1絶縁膜と並ぶように前記半導体基板上に第5絶縁膜とを有する。さらに、第5絶縁膜上に形成され、第4絶縁膜の側面に前記第1ゲート電極と隣り合うように第2ゲート電極と、第1ゲート電極と第2ゲート電極を挟むように半導体基板にソース領域およびドレイン領域とを有する。半導体装置は、導電膜と電荷蓄積膜が平面的に重なり合うように形成されている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】メモリセルアレイの耐ストレス性を向上できるようにする。

【解決手段】局所選択ゲート電極CSGが、部分的にメモリセルトランジスタMTを選択(例えばメモリセルトランジスタMT0〜MT7)することで、その他のメモリセルトランジスタMT(例えばメモリセルトランジスタMT8〜MT63)を非選択状態にすることができ、当該非選択状態とされたメモリセルトランジスタMTに高電圧を与える必要がない。

(もっと読む)

メモリにおけるプログラムノイズ低減のための鋸形のマルチパルスプログラミング

不揮発性半導体記憶装置

【課題】誤書き込みを抑制する。

【解決手段】不揮発性半導体記憶装置は、第1セレクトゲートSGDおよび第1セレクトゲートの一方に隣接する第1ワード線WL31を有する第1ブロックと、第1セレクトゲートの他方にビット線に接続されるコンタクト配線DCを挟んで隣接する第2セレクトゲートSGDおよび第2セレクトゲートに隣接し第1ワード線と同一番号が割り当てられた第2ワード線WL31を有し、第1ブロックと隣接して配置される第2ブロックと、第1、第2セレクトゲートに印加される電圧に関する第1、第2データを記憶する記憶回路20と、第1、第2セレクトゲートに印加される電圧を制御する制御回路8と、を具備し、制御回路は書き込み動作時に第1データに基づいて第1セレクトゲートに第1電圧を印加し、第2データに基づいて第2セレクトゲートに第1電圧と異なる第2電圧を印加する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位変換回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体メモリ

【課題】 低消費電力、高集積化を図ることができる不揮発性メモリ装置を提供する。

【解決手段】 行列状に配置されたメモリセルを含み、メモリセルのゲートにワード線が接続され、ドレインにローカルビット線LBLdが接続され、ソースに第1または第2のローカルビット線LBLSが接続される。メモリセルMC2の読み出しを行うとき、ビット線選択トランジスタTRd1によって選択されたローカルビット線LBLd1に読出し電圧Vreadを印加し、第1の選択トランジスタTRs0によって選択された第1のローカルビット線LBLs0に0vを印加する。隣接するメモリセルMC3のソースは、第2の選択トランジスタTRs4によって一定電位にクランプされ、隣接するメモリセルMC1のソースは、ビット線選択トランジスタTRd0によって0vに印加される。

(もっと読む)

不揮発性半導体記憶装置

【課題】高効率的に書き込みを行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】直列接続された複数のメモリセルトランジスタMTと、メモリセルトランジスタの一端とソース線との間に接続された選択ゲートトランジスタST2と、メモリセルトランジスタの他端とビット線との間に接続された選択ゲートトランジスタST1と、ソース線に第1の電圧を印加し、ビット線に第1の電圧よりも高く且つ第1の電圧との差がトンネル絶縁膜のバリアハイトに対応する電圧よりも小さい第2の電圧を印加し、書き込み対象のメモリセルトランジスタMTとソース線との間に位置し、且つ書き込み対象のメモリセルトランジスタに隣接する隣接メモリセルトランジスタMTの導通状態を、他のメモリセルトランジスタMTの導通状態よりも弱くすることで書き込み対象のメモリセルトランジスタに書き込みを行う制御回路と、を具備する。

(もっと読む)

フラッシュメモリの製造方法

【課題】フラッシュメモリの製造工程において、エッチングによるSTI膜の膜減りを抑制することができる製造方法と、それを可能にするスプリットゲートタイプのMONOS型フラシュメモリ構造を提供する。

【解決手段】ワードゲートとコントロールゲートを含むスプリットゲートタイプのMONOS型フラシュメモリの製造方法であって、STIによって分離された半導体基板の不純物拡散層上に、酸化膜を挟んだワードゲートを形成する工程と、該STIとワードゲートが形成された半導体基板の表面全体に酸化膜、窒化膜、酸化膜の順に成膜されるONO層を形成する工程と、該ONO層の上にコントロールゲート用導電膜(10)を形成する工程と、該コントロールゲート用導電膜の表面全体にマスク用絶縁膜(26)を形成する工程と、を含む。

(もっと読む)

61 - 80 / 328

[ Back to top ]