Fターム[5F083GA15]の内容

Fターム[5F083GA15]に分類される特許

81 - 100 / 328

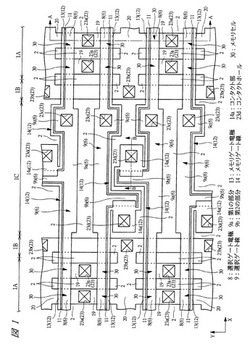

半導体装置

【課題】半導体装置の性能を向上させ、製造歩留りを向上させる。

【解決手段】メモリセル30が複数アレイ状に配置され、X方向に並ぶメモリセル30の選択ゲート電極8は選択ゲート線9によって接続され、メモリゲート電極13はメモリゲート線14によって接続される。ソース領域20を介して隣接するメモリセル30のメモリゲート電極13にそれぞれ接続されたメモリゲート線14同士は電気的に接続されていない。選択ゲート線9は、X方向に延在する第1の部分9aと、一端が第1の部分9aに接続してY方向に延在する第2の部分9bを有している。メモリゲート線14は、選択ゲート線9の側壁上に絶縁膜を介して形成され、選択ゲート線9の第2の部分9b上から素子分離領域上にかけてX方向に延在するコンタクト部14aを有し、コンタクト部14a上に形成されたコンタクトホール23dを埋めるプラグを介して配線に接続される。

(もっと読む)

不揮発性記憶装置

【課題】抵抗変化素子の保温性能を高め、抵抗変化素子の周囲の絶縁層との反応を防止するとともに、隣接する抵抗変化素子との間でのリークの発生を抑制することができる不揮発性記憶装置を提供する。

【解決手段】第1の方向に延在するワード線WLと、ワード線WLとは異なる高さに形成されるビット線BLと、ワード線WLとビット線BLとが交差する位置にワード線WLとビット線BLの間に挟持されるように配置される、抵抗変化素子VRと整流素子Dとを含む抵抗変化型メモリセルMCと、を備え、隣接する抵抗変化型メモリセルMC間のうち少なくとも抵抗変化素子VRの周囲は、真空にされ、またはガスによって満たされている。

(もっと読む)

半導体集積回路

【課題】 抵抗変化性のバイポーラ型メモリを、誤書き込みや誤動作を起こさずにFPGAに適用する。

【解決手段】 本発明の半導体集積回路は、一端が第一の電源105に接続され、他端が出力ノード108に接続される第一の抵抗変化性素子101と、一端が出力ノード108に接続される第二の抵抗変化性素子102と、第二の抵抗変化性素子102の他端と第一の端子が接続され、第二の電源106と第二の端子が接続される、第一のスイッチング素子103とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み/消去におけるディスターブを抑制し、かつ面積の増大を抑えた不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルMCを含む第1セルアレイ32が形成された第1導電型の第1のウェル領域と、複数のメモリセルMCを含む第2セルアレイ32が形成された第1導電型の第2のウェル領域と、第1、第2のウェル領域を含む第2導電型の第3のウェル領域とを備える。さらに、第1セルアレイ32が含むメモリセルと第2セルアレイ32が含むメモリセルとに共通に接続されたビット線BLと、ビット線BLに接続されたカラムデコーダ13とを備える。

(もっと読む)

不揮発性フラッシュメモリ

【課題】低消費電力、低減されたリーク問題、および単純なプロセスを伴った新規なフラッシュメモリ、新規なプログラミング方法、およびそのセンシングスキームを提供する。

【解決手段】ワード線218、第1のビット線204、および第2のビット線206を備えた不揮発性メモリセル200を動作させる方法は、メモリセル200をプログラミングする工程を有し、そのプログラミングする工程が、高い正電圧のバイアスを第1のビット線に印加し、接地バイアスを第2のビット線に印加し、高い負電圧のバイアスをワード線に印加することを備え、正帯電ホールが誘電体層212を介してトラッピング層214に突き抜けるようにする。

(もっと読む)

不揮発性半導体記憶装置

【課題】従来に比してメモリセルの積層数を抑えながら記憶密度を高めることができる不揮発性半導体記憶装置を提供する。

【解決手段】柱状の半導体膜131の側面に形成される電荷蓄積層133と、電荷蓄積層133上に形成されるゲート電極膜134とを備えるトランジスタを半導体膜131の高さ方向に複数有するメモリストリングスMSを有し、メモリストリングスMSは、第1の方向に配置されたメモリストリングスMSの同じ高さのトランジスタのゲート電極膜134間が接続されたメモリストリングス列を、第2の方向に隣接して2本並行配置したメモリストリングス群が第2の方向に所定の間隔で配置されるように、半導体基板101上に配置され、メモリストリングス群内で、第2の方向に隣接して2本並行配置したメモリストリングス列の間には絶縁膜124が形成されて電気的に離間されている。

(もっと読む)

不揮発性半導体記憶装置、および不揮発性半導体記憶装置の製造方法

【課題】ライトディスターブ(WDT)が発生しない不揮発性半導体記憶装置を提供する。

【解決手段】第1方向に延伸する第1素子分離絶縁領域42と、その第1素子分離絶縁領域42と異なる第2素子分離絶縁領域42と、第1メモリセル2と、第2メモリセル15とを具備する不揮発性半導体記憶装置1を構成する。ここで、その第1メモリセル2は、第2方向に延伸する第1コントロールゲート21を備える。その第2メモリセル15は、その第1コントロールゲート21に対向する第2コントロールゲート35を備える。その第1コントロールゲート21は、第1引き出し電極3に接続されている。その第1引き出し電極3は、その第2コントロールゲート35の側面から離れた位置のその第1素子分離絶縁領域42を掘り下げた第1掘り下げ領域7の内部に設けられるものである。

(もっと読む)

半導体記憶装置

【課題】スプリットゲート型のMONOSメモリセルを有する半導体記憶装置において、SSI方式による書込み時のディスターブ耐性を向上させる。また、非選択メモリセルのディスターブ耐性が向上することにより、メモリモジュールの面積を低減させる。

【解決手段】メモリゲート電極12の側面において、電荷蓄積膜9と絶縁膜11との間に絶縁膜10を形成し、メモリゲート電極12側面の絶縁膜10および11の合計の厚さを、メモリゲート電極12下部の絶縁膜11の厚さよりも厚く形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】従来に比してメモリセルの積層数を抑えながら記憶密度を高めることができる不揮発性半導体記憶装置を提供する。

【解決手段】柱状の半導体膜131の側面に形成される電荷蓄積層133、および電荷蓄積層133上に形成されるゲート電極膜134を備えるトランジスタが半導体膜131の高さ方向に複数設けられるメモリストリングスMSが、半導体基板101上に略垂直にマトリックス状に配置され、第1の方向に配置されたメモリストリングスMSの同じ高さのトランジスタのゲート電極膜134間が接続された不揮発性半導体記憶装置において、第1の方向に隣接するメモリストリングスMSの少なくとも最上層のトランジスタ形成位置における半導体膜131間の距離は、電荷蓄積層133の厚さの2倍よりも小さい。

(もっと読む)

スプリットゲート不揮発性メモリセルの作製に有用な半導体構造を形成する方法

半導体層(12)に半導体デバイス(10)を形成する方法が提供される。方法は、半導体層(12)の上方に選択ゲート誘電体層(14)を形成すること、選択ゲート誘電体層(14)の上方に選択ゲート層(16)を形成すること、選択ゲート層の少なくとも一部分を除去することによって、選択ゲート層(16)の側壁を形成することを含む。方法は、選択ゲート層(16)の側壁の少なくとも一部分に、および選択ゲート層(16)の少なくとも一部分の下に、犠牲層(22)を成長させること、犠牲層(22)を除去して、選択ゲート層の側壁の少なくとも一部分の表面および選択ゲート層の下の半導体層の表面を露出させることをさらに含む。方法は、制御ゲート誘電体層(28)、電荷蓄積層(32)、および制御ゲート層(34)を形成することをさらに含む。 (もっと読む)

不揮発性メモリセル、これを有するメモリアレイ、並びに、セル及びアレイの操作方法

【課題】自己収束消去動作を容易にすると共に保持状態の期間におけるメモリデバイスの電荷蓄積層内での電荷保持能力を保持してもいるトンネル誘電体構造を有する不揮発性メモリデバイスの提供。

【解決手段】半導体基板101であって、該基板の表面より下に配置され且つチャネル領域106によって分離されたソース領域102及びドレイン領域104を備えた半導体基板と、前記チャネル領域より上に配置されたトンネル誘電体構造102であって、低いホールトンネリング障壁高さを有する少なくとも1つの層を備えたトンネル誘電体構造と、前記トンネル誘電体構造より上に配置された電荷蓄積層130と、前記電荷蓄積層より上に配置された絶縁層140と、前記絶縁層より上に配置されたゲート電極150とを有するメモリセル、該メモリセルのアレイ及び操作方法と共に開示する。

(もっと読む)

半導体装置

【課題】書き換え可能な不揮発性メモリセルが多数配列されたメモリアレイを含む不揮発性記憶部を備えた半導体装置において、非選択メモリセルに生じる誤書き込みを低減することができる。

【解決手段】メモリアレイMARの第1方向の端部とp型ウェル4の給電部PVとの間に、メモリセル1つ分以上の間隔を設け、メモリアレイMARの第2方向の端部とp型ウェル4の給電部PVとの間に、データの記憶に寄与しない複数のダミーメモリセルから構成されるダミーメモリアレイDMYを設けることにより、メモリアレイMARの周辺部に位置する非選択メモリセルに注入される2次電子を低減する。

(もっと読む)

不揮発性半導体記憶装置

【課題】他のコントロールゲートからのディスターブを抑制するツインMONOS型フラッシュメモリを提供する。

【解決手段】第1の方向に延設された第1のワードゲートWG1と、第1のワードゲートWG1の一方の側壁に沿って形成された第1のコントロールゲートCGa1と、第1の方向に延設され、第1のワードゲートWG1と隣り合う第2のワードゲートWG2と、第2のワードゲートWG2の一方の側壁に沿って形成された第2のコントロールゲートCGa2と、を備える。第2のワードゲートWG2側に突出した2つの第1のワードゲートWG1の突出部の間に、第1のコントロールゲートCGa1は第1のコンタクト部12を備え、第1のワードゲートWG1側に突出した2つの第2のワードゲートWG2の突出部の間に、第2のコントロールゲートCGa2は第2のコンタクト部12を備え、両コンタクト部12が、電気的に絶縁されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】隣接メモリセル間の距離が縮小したときに、隣接メモリセル間で発生する問題を解決して信頼性を向上させる。

【解決手段】 半導体基板2上にゲート絶縁膜5を形成し、ゲート絶縁膜5上に電荷蓄積層6、中間絶縁膜7、および導電層8を順次形成し、導電層8、中間絶縁膜7および電荷蓄積層6に電極分離用の溝9を形成し、導電層8の上面及び側面、中間絶縁膜7の側面、電荷蓄積層6の側面、並びに、ゲート絶縁膜5の上面に窒化膜11を形成し、ゲート絶縁膜5の上面に形成された窒化膜11を除去し、電極分離用の溝9に絶縁膜10を埋め込むようにした。

(もっと読む)

半導体集積回路装置の製造方法

【課題】共通ゲートを有する複数のトランジスタセルをアレー状に配置する構成を持つ不揮発性半導体集積回路装置において、STI領域のパターニング工程でのパターンの変形を防ぐ製造方法を提供する。

【解決手段】半導体メモリ等のメモリセルアレー等の露光において、矩形形状のSTI溝領域エッチング用単位開口を行列状に配置したSTI溝領域エッチング用単位開口群をネガ型レジスト膜28上に露光するに際して、列方向に延びる第1の線状開口群を有する第1の光学マスクを用いた第1の露光ステップと、行方向に延びる第2の線状開口群を有する第2の光学マスクを用いた第2の露光ステップとを含む多重露光を適用する。直行する2方向において、それぞれの方向に対してマスクを用いて露光を行うことで、矩形形状48の端部における近接効果を回避することができ、矩形形状48の端部が丸みを帯びるのを回避することができる。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイ全体の消費電力を削減することが可能であり、且つ高集積化の可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ワード線1と、ワード線1と交差するように配置されたビット線2と、ワード線1とビット線2との各交差部に配置された絶縁膜3と、ワード線1の間及びビット線2の間を埋め込む層間絶縁膜と、ビット線1に接続され、低抵抗状態と高抵抗状態との間で遷移する抵抗変化材4とを備える。ワード線1、ビット線2、及び絶縁膜3はワード線1とビット線2との各交差部において電界効果トランジスタを構成する。電界効果トランジスタ及び抵抗変化材4はメモリセルを構成する。ビット線2は、絶縁膜を介してワード線1と対向する第1面と、この第1面とは反対側の第2面とを有する。抵抗変化材4は、第2面と接するように配置され、且つその一部が層間絶縁膜と接触している。

(もっと読む)

不揮発性半導体メモリデバイス

【課題】ダイナミック放電読み出しでセンスタイミングのずれを是正する。

【解決手段】センスアンプ7Bは、メモリセル抵抗Rcellの一方の電極が接続されたビット線BLの放電電位を参照電位Vrと比較して情報を読み出す。セット容量スイッチ18S、リセット容量スイッチ18Rおよび追加容量Coffsetとその制御手段によって、センスノード(電位Vo)の負荷容量、または、センスノードと参照電位Vrを入力する参照ノードの負荷容量との両方を、メモリセル抵抗Rcellの読み出す情報の論理(通常読み出し、書き込みまたは消去のヴェリファイ読み出しの相違)に応じて変化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを形成した半導体チップを充分に縮小化することができる技術を提供する。また、不揮発性メモリの信頼性を確保することができる技術を提供する。

【解決手段】本発明のメモリセルでは、コントロールゲート電極CG上に絶縁膜IF1を介してブーストゲート電極BGが形成されている。このブーストゲート電極BGは、メモリゲート電極MGとの間の容量カップリングにより、メモリゲート電極MGに印加される電圧を昇圧する機能を有している。つまり、メモリセルの書き込み動作や消去動作の際、メモリゲート電極MGに高電圧が印加されるが、本発明では、メモリゲート電極MGに高電圧を印加するために、ブーストゲート電極BGを使用した容量カップリングを補助的に使用する。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み動作と消去動作との干渉を防止し、誤書き込みの発生を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、互いに交差する複数の第1及び第2の配線の各交差部に設けられ同一極性の電圧印加によってデータの書き込みと消去を行う複数のメモリセルからなるメモリセルアレイと、選択された第1及び第2の配線を介してメモリセルに対してセットパルス/リセットパルスを供給する書き込み回路とを備え、リセットパルスの電圧の大きさ及び電圧印加時間の組み合わせの集合であるリセット領域は、電圧の大きさ及び電圧印加時間の関係が負の相関関係を持つ領域であり、書き込み回路は、消去動作時、リセットパルスを、その電圧の大きさ及び電圧印加時間をリセット領域の範囲内で増減させながら、選択メモリセルに対してデータが消去されるまで繰り返し供給する。

(もっと読む)

不揮発性半導体記憶装置及びその書き込み方法

【課題】書き込み速度の遅れや書き込み不良等を招くことなく、更なる微細化を実現し得る不揮発性半導体記憶装置及びその書き込み方法を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタとを有する複数のメモリセルと、選択トランジスタのドレインに接続されたビット線と、メモリセルトランジスタのコントロールゲートに接続された第1のワード線と、選択トランジスタのセレクトゲートに接続された第2のワード線と、メモリセルトランジスタのソースに接続されたソース線とを有し、第1の電圧Vstep(1)を第1のワード線に印加しながら、ソース線に第2の電圧Vpulse(1)をパルス状に印加する第1のステップと、第1の電圧より高い第3の電圧Vstep(2)を第1のワード線に印加しながら、ソース線に第2の電圧より低い第4の電圧Vpulse(2)をパルス状に印加する第2のステップとを少なくとも実行することにより、メモリセルに情報を書き込む。

(もっと読む)

81 - 100 / 328

[ Back to top ]