Fターム[5F083GA15]の内容

Fターム[5F083GA15]に分類される特許

41 - 60 / 328

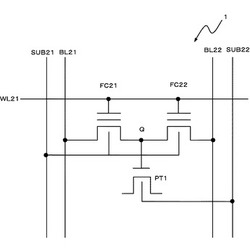

不揮発プログラマブルロジックスイッチ

【課題】 誤動作を防ぐとともに、サイズが小さい不揮発プログラマブルロジックスイッチを提供すること。

【解決手段】 本発明の実施形態による不揮発プログラマブルロジックスイッチは、制御ゲートが第1の配線に接続され、第1のソースドレイン端が第2の配線に接続され、電荷を蓄積する膜を有する第1のメモリセルトランジスタと、制御ゲートが前記第1の配線に接続され、第3のソースドレイン端が前記第1のメモリセルトランジスタの第2のソースドレイン端に接続され、第4のソースドレイン端が第3の配線に接続され、電荷を蓄積する膜を有する第2のメモリセルトランジスタと、前記第1のメモリセルトランジスタの前記第2のソースドレイン端と前記第2のメモリセルトランジスタの前記第3のソースドレイン端にゲート電極が接続されたパストランジスタと、前記パストランジスタのウェルに基板電圧を印加する第1の基板電極を有する。

(もっと読む)

記憶装置およびその製造方法

【課題】メモリセルの構造を最適化することにより、更なる微細化を可能にする記憶装置を提供する。

【解決手段】複数の第1の電極配線と、第1の電極配線と交差する複数の第2の電極配線と、1本の第2の電極配線と、互いに隣接する2本の第1の電極配線との間に形成される1個のビアプラグであって、前記第1の電極配線に対向する底面の、第1の電極配線の伸長方向に垂直な方向の最大径が、第1の電極配線幅の2倍と第1の電極配線間の幅を加えた長さよりも小さいビアプラグと、ビアプラグと2本の第1の電極配線の一方との間に形成される第1の記憶素子と、ビアプラグと2本の第1の電極配線の他方との間に形成される第2の記憶素子とを有する記憶装置。

(もっと読む)

半導体装置

【課題】相変化メモリを低電圧動作および高温の動作又は放置させる場合に、記録保持信頼性を向上させる技術を提供する。

【解決手段】読み出し電圧をセット電圧およびリセット電圧以上として高速動作させ、読み出し後に読み出し前の状態を再書込みする、いわゆる破壊読出しを行う。または、複数個のセルを用いて1ビットの情報を記録する、いわゆるオアセルを用いて、高温時の動作又は放置のける信頼性を向上させる。破壊読出しおよびオアセルを用いた相変化メモリに必要な、回路構成および動作方法を用いる。

(もっと読む)

半導体記憶装置の製造方法

【課題】隣接するメモリセル間およびメモリセルと選択トランジスタとの間に間隙を設けつつ、選択トランジスタおよび周辺回路における短絡を抑制する。

【解決手段】本実施形態による半導体記憶装置は、ゲートを有する複数のメモリセルが直列に接続されたメモリセルストリングを備える。選択トランジスタが、メモリセルストリングの一端にある端部メモリセルに接続されている。側壁膜が、端部メモリセルと選択トランジスタとの間において、端部メモリセルのゲートの側面および選択トランジスタのゲートの側面を被覆する。端部メモリセルの側壁膜と選択トランジスタの側壁膜との間に空隙がある。

(もっと読む)

記憶装置

【課題】誤書込みを防止することが可能な記憶装置を提供する。

【解決手段】複数のメモリセルが直列に接続されたNANDセルユニットと、NANDセルユニットの一方の端子に接続する第1の選択トランジスタと、NANDセルユニットの他方の端子に接続する第2の選択トランジスタと、第1の選択トランジスタと接続するソース線と、該ソース線と交差し、且つ第2の選択トランジスタと接続するビット線とを有し、第1の選択トランジスタ及び第2の選択トランジスタは、チャネル領域が酸化物半導体層で形成されたトランジスタである。

(もっと読む)

半導体記憶装置の製造方法

【課題】製造が容易なNAND型半導体記憶装置の製造方法を提供する。

【解決手段】製造方法は、基板101上に第1絶縁膜105及び第2絶縁膜106を交互に積層して積層体110を形成する工程と、第1絶縁膜105及び第2絶縁膜106の積層方向に延び、積層体110を貫通する貫通孔114を形成する工程と、貫通孔114の内面上に、MONOS116を構成するブロック絶縁膜、チャージトラップ膜及びトンネル誘電体膜の少なくとも一部を形成する工程と、トンネル誘電体膜上にチャネル半導体117を形成する工程と、積層体110にトレンチ121を形成する工程と、トレンチ121を介してエッチングを施すことにより、第2絶縁膜106を除去する工程と、第2絶縁膜106を除去した後の空間内に導電材料を埋め込む工程と、を備える。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】カーボンナノチューブを可変抵抗素子として用い消費電力の抑制とスイッチの誤作動の低減を両立した不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施形態の不揮発性半導体記憶装置の製造方法は、半導体基板9上に、下部電極を形成する工程と、前記下部電極の上にカーボンナノチューブを含む可変抵抗層11を形成する工程と、前記可変抵抗層に電子線或いは光子線を照射する照射工程と、前記照射工程の後に、前記可変抵抗層の上に上部電極を形成する工程とを含む。

(もっと読む)

磁性積層体、方法、およびメモリセル

【課題】フォノンブロック絶縁層を有する不揮発性メモリセルのための装置および関連の方法を提供する。

【解決手段】さまざまな実施形態に従うと、磁性積層体は、トンネル接合と、強磁性フリー層と、ピンド層と、少なくとも1つの導電性構造を通る電気的伝導を許しつつフォノンをブロックする電気絶縁性および断熱性の材料から構築される絶縁層とを有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】柱状のチャネル層となる半導体層に沿って、複数の浮遊ゲート型の不揮発性メモリセルが積層された構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、柱状の半導体膜131の側面にトンネル誘電体膜141、浮遊ゲート電極膜142、ゲート間絶縁膜143および制御ゲート電極膜144を備えるメモリセルMCが半導体膜131の延在方向に複数設けられるメモリセル列を、半導体基板101上に略垂直に複数配置した不揮発性半導体記憶装置が提供される。ここで、浮遊ゲート電極膜142と制御ゲート電極膜143は、柱状の半導体膜131の全周のうち特定の方向の側面にのみ形成されている。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

半導体記憶装置

【課題】

駆動回路からメモリセルへの寄生抵抗や寄生容量の影響により、非選択セルへの熱ディスターブ、印加電圧のばらつき、読み出し時の記憶素子の劣化等の課題があった。

【解決手段】

電流により記憶情報が書き込まれる記憶素子と、当該記憶素子に接続される選択素子と、を有するメモリセル(MC)の上方または下方にキャパシタ(C)を設け、当該キャパシタに蓄積された電荷によって記憶素子に書き込みを行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】 260℃付近の高温下でのデータ保持特性に優れた不揮発性半導体記憶装置を提供する。

【解決手段】 第1電極2と、第2電極3と、両電極の間に介装された金属酸化物からなる可変抵抗体4を備え、第1電極2が可変抵抗体4とオーミック接合を形成する導電性材料で形成され、第2電極3が可変抵抗体4と非オーミック接合を形成する導電性材料で形成され、両電極間に電圧を印加することにより抵抗状態が2以上の異なる抵抗状態間で遷移し、当該遷移後の抵抗状態を不揮発的に保持する可変抵抗素子を備えて構成されたメモリセルを複数配列して、ユーザデータの格納用としたメモリセルアレイを備えた不揮発性半導体記憶装置において、メモリセルアレイがユーザデータの格納用として使用される前の使用前状態において、メモリセルアレイ内の全てのメモリセルの可変抵抗素子を、2以上の異なる抵抗状態の内の最も高抵抗の抵抗状態に高抵抗化する。

(もっと読む)

半導体装置

【課題】 制御端子が浮遊状態になると、予期しないリーク電流などにより電極に電荷が蓄積され、電極の電位が変動し、スイッチが誤動作してしまう可能性がある。

【解決手段】 クーロン力により湾曲させることで第1の信号電極と第2の信号電極とを接触または分離することが可能な架橋部と、前記架橋部を制御するための制御端子とを有するスイッチ素子と、前記制御端子に接続された第1の不揮発性半導体素子と、前記制御端子および前記第1の不揮発性半導体素子に接続された第2の不揮発性半導体素子とを備える。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】不揮発性記憶装置およびその製造方法に関し、抵抗変化材料を利用したメモリの信頼性の向上を実現する。

【解決手段】積半導体素子を形成する基板の上方に、第1方向に延伸するように複数の金属配線層2を設け、金属配線層2のさら上方に、前記第1方向に直交する第2方向に延伸するように複数の金属配線層3を設ける。また、金属配線層2と金属配線層3とが交差する空間のそれぞれにメモリセルを設ける。前記メモリセルは、選択素子と相変化材料層7とが並列接続された構成とする。ここで、前記選択素子の前記第1方向の寸法が、相変化材料層7の前記第1方向の寸法よりも大きくなるように加工する。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去電圧を低減させることができる半導体記憶装置を提供することを課題とする。

【解決手段】チャネル形成領域を有する半導体膜と、半導体膜のチャネル形成領域上に、第1の絶縁層、浮遊ゲート電極、第2の絶縁層、制御ゲート電極を設ける。浮遊ゲート電極材料には、半導体基板よりも仕事関数があまり大きくならない窒化チタンとすることにより、消去電圧低減を図ったものである。なお、上記窒化チタンのチタン組成比は、低消費電力化及び誤書き換え耐性の観点から56atomic%以上75atomic%以下がよい。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 ダイオードとトランジスタとを直列接続した半導体メモリにおいて、ダイオードからトランジスタにキャリアが入ることで、トランジスタの特性が劣化する課題がある。

【解決手段】 半導体記憶装置において、ダイオード(PD)中のキャリアを生成するダイオード半導体層(40p)と、トランジスタのチャネル層(8p)との間に、当該キャリアを対消滅させる構造(61pと62p等)を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】不揮発性半導体記憶装置の高信頼性及び高集積化を図る。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1乃至第iのメモリストリング(iは、2以上の自然数)を有し、第2の方向に延び、第3の方向に隣接する第1及び第2のフィン型積層構造9−1,9−2と、第1のフィン型積層構造9−1の第2の方向の一端に接続され、第3の方向の幅が第1のフィン型積層構造9−1のそれよりも広い第1の部分7aと、第2のフィン型積層構造9−2の第2の方向の一端に接続され、第3の方向の幅が第2のフィン型積層構造9−2のそれよりも広い第2の部分7bとを備える。第1乃至第iのメモリストリングは、それぞれ、複数のメモリセルとアシストゲートトランジスタとを備える。アシストゲートトランジスタのアシストゲート電極AG1,AG2は、電気的に独立である。

(もっと読む)

半導体記憶装置

【課題】消去回数の増加を抑制し、書き込み速度の向上及びメモリセルの劣化を防止することが可能な半導体記憶装置を提供すること。

【解決手段】読み出しレベルに応じてデータを保持可能なセルMCが形成されたセルアレイ1と、前記セルMCに書き込まれた回数N(N:0以上の整数)をカウントし、その回数に応じて書込電圧Vpgm及び読出電圧Vcgrを前記セルに転送する制御部9と、前記書込電圧を用いてデータを書み込み、前記読出電圧を発生し、データを読み出す電圧発生回路とを具備し、書込要求があると、前記読出電圧を発生させ、前記データを読み出し、読み出された閾値電圧より高い閾値電圧に遷移させる前記書き込み電圧を前記電圧発生回路に発生させ、前記セルへの前記回数N回目(≧2)の書き込み要求が規定値に達していると、前記制御部は前記セルが保持する前記データを消去させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化が進展しても読み出し動作時の電流を維持する。

【解決手段】複数のメモリサブブロックの各々は、第1ノードと第2ノードとの間に並列接続された複数のメモリトランジスタを含む。メモリサブブロックは、第1導電層と、第2導電層と、半導体層と、第3導電層とを備える。第1導電層は、層間絶縁膜を貫通して半導体基板に対し垂直な第1方向に延びるように形成され第1ノードとして機能する。第2導電層は、層間絶縁膜を貫通して半導体基板に対し第1方向に延びるように形成され第2ノードとして機能する。半導体層は、第1導電層と第2導電層とを接続するように半導体基板と平行な第2方向に延びるように形成されメモリトランジスタのチャネル層として機能する。第3導電層は、半導体層上にゲート絶縁膜を介して形成される。ゲート絶縁膜は、電荷蓄積膜を一部に含み第3導電層を囲う閉ループ状に形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】データリテンションの特性を向上しつつ消去動作や書き込み動作に要する時間を短縮する。

【解決手段】

不揮発性半導体記憶装置は、第1書き込み領域と第2書き込み領域を有し、複数のメモリセルを含むメモリセルアレイを備える。制御回路は、複数のメモリセルに対して印加する電圧を制御する。制御回路は、複数のメモリセルに対し消去動作を実行する場合に、第2書き込み領域のメモリセルに隣接する第1書き込み領域のメモリセルを除いた第1書き込み領域のメモリセルに第1閾値電圧を与える一方、第2書き込み領域のメモリセル及び第2書き込み領域のメモリセルに隣接する第1書き込み領域のメモリセルに第1閾値電圧より電圧値が大きい消去状態を示す正の第2閾値電圧を与えるよう制御する。

(もっと読む)

41 - 60 / 328

[ Back to top ]