Fターム[5F083GA23]の内容

Fターム[5F083GA23]に分類される特許

1 - 20 / 24

ノードコンタクト構造体

【課題】ノードコンタクト構造体を有する半導体素子と、その製造方法を提供する。

【解決手段】半導体基板の上に形成されソース/ドレイン領域を有するバルクモストランジスタを備える。該バルクモストランジスタ上に層間絶縁膜が形成され、該層間絶縁膜上にソース/ドレイン領域を有する薄膜トランジスタが形成される。該バルクモストランジスタのソース/ドレイン領域上に半導体プラグが形成され、該半導体プラグは該層間絶縁膜の少なくとも一部を介して延長される。該薄膜トランジスタのソース/ドレイン領域及び該半導体プラグは金属プラグと接触し、該金属プラグは該層間絶縁膜の少なくとも一部を介して延長される。該半導体プラグ及び該金属プラグは多層のプラグを構成する。

(もっと読む)

半導体集積回路

【課題】ソフトエラー耐性やラッチアップ耐性の更なる向上が求められている。

【解決手段】CMOSレイアウトを有する半導体集積回路を以下のように構成する。その半導体集積回路(1)は、基板(2)と、基板(2)に、第1方向に沿って形成されたNウェル(5)と、基板(2)に、第1方向に沿って形成され、素子分離領域(7)を介してNウェル(5)の隣に形成されたPウェル(6)とを備えていることが好ましい。そして、素子分離領域(7)よりも下の基板(2)に形成され、第1方向と異なる第2方向に沿って形成されたディープNウェル(3)と、第2方向に沿って形成され、ディープNウェル(3)に隣接して形成されたディープPウェル(4)とを具備することが好ましい。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置

【課題】ソフトエラー耐性に優れた、微細構造を有する半導体装置を提供すること。

【解決手段】本発明は、複数のトランジスタを含むメモリセル領域Cellとメモリセル領域Cellに隣接して配置されたコア領域Coreとを備える。メモリセル領域Cell及びコア領域Coreは、基板1と、基板1上に形成されたp型ウェル領域2及びn型ウェル領域3を備える。また、メモリセル領域Cellは、基板1とp型ウェル領域2及びn型ウェル領域3の下に形成されたp型深ウェル領域5aを備える。p型深ウェル領域5aは、少なくともp型ウェル領域2と接している。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗素子の小型化と電界効果トランジスタのラッチアップ耐性の向上とを両立させた半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板11のNウェル抵抗素子形成領域にSTI12を形成する。次に、P型MOSトランジスタ形成領域に対してドナーを注入して、ドナー拡散領域21を形成する。次に、Nウェル抵抗素子形成領域及びP型MOSトランジスタ形成領域に対してドナーを注入して、Nウェル抵抗素子形成領域におけるSTI12の直下域にN型ウェル14を形成すると共に、P型MOSトランジスタ形成領域にドナー拡散領域20を形成する。ドナー拡散領域21及び20は重ね合わせられて、P型MOSトランジスタ7のチャネル領域を構成するN型ウェル19が形成される。このとき、N型ウェル14及びドナー拡散領域20を形成するための不純物注入量を、ドナー拡散領域21を形成するための不純物注入量よりも少なくする。

(もっと読む)

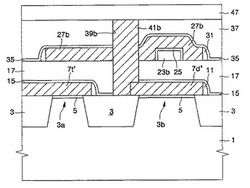

半導体記憶装置およびその製造方法

【課題】消費電力の増大に対して有利な半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルをそれぞれ備え、半導体基板35上に複数積層される三次元構造の複数のメモリセルアレイ10と、半導体基板35中に設けられる第1導電型の第1ウェル43と、第1ウェル43中において第1ウェル43の底面よりも浅い位置に底面を有し、半導体基板35中に埋め込み配置される素子分離絶縁膜STIと、第1ウェル43中において第1ウェル43の底面よりも浅い位置に底面を有し(DP<DN)、素子分離絶縁膜STIの少なくとも一部の底面に沿って設けられ、第2導電型の不純物によって形成される第2ウェル44と、第1ウェルと電気的に接続されるコンタクト配線CLとを具備する。

(もっと読む)

半導体記憶装置

【課題】スタンバイ電流が小さく、ラッチアップに強い半導体記憶装置を提供する。

【解決手段】このSRAMは、各行に対応して設けられて対応の行のメモリセル電源配線MVLの一方端と電源電位VDD′のラインとの間に接続され、比較的高い導通抵抗値を有するPチャネルMOSトランジスタ1を備える。したがって、スタンバイ電流を低減化し、ラッチアップ現象の発生を抑制することができる。

(もっと読む)

同軸のトランジスタ構造

【課題】 本発明は基板上での同軸トランジスタを開示する。

【解決手段】同軸構造のMOSFETであって、チップ或いは基板(Wafer Bonding)を積層し、軸心貫通孔により貫通し接続してより高い集積度及びラッチ効果のない同軸全対称のCMOSFETの集積回路を形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース/ドレイン領域における接合部の耐圧を向上でき、寄生バイポーラトランジスタ特性の影響を低減できる半導体装置を提供する。

【解決手段】(a)に示す低耐圧トランジスタは、ソース/ドレイン領域13,14間の基板11の第1領域上に形成されたゲート絶縁膜15及び第1ゲート電極16と、ソース/ドレイン領域13,14上のシリサイド層13A,14Aとを備える。(b)に示す高耐圧トランジスタは、ソース/ドレイン領域23,24間の基板11の表面が所定の深さ除去された第2領域上に形成された、ゲート絶縁膜15より膜厚が厚いゲート絶縁膜25、及び第2ゲート電極16と、ソース/ドレイン領域23,24上のシリサイド層23A,24Aとを備える。所定の深さはゲート絶縁膜25とゲート絶縁膜15との厚さの差に相当し、シリサイド層23A,24Aの上面は基板11の第2領域とゲート絶縁膜25との界面より高い構造を有する。

(もっと読む)

プログラマブルアンチヒューズトランジスタ及びそのプログラム方法

ゲート端子(12)を備える少なくとも1個のゲート(G)と、ソース端子(14)を備える少なくとも1個のソース(S)と、ドレイン端子(16)を備える少なくとも1個のドレイン(D)と、基板端子(18)を備える少なくとも1個の基板(10)とを備える、プログラマブルアンチヒューズトランジスタ(100)、特に、NチャネルMOSトランジスタ、及び少なくとも1個のそのようなアンチヒューズトランジスタ(100)をプログラムする方法を、能動回路/回路素子をアンチヒューズから著しく離れた場所に位置させる必要がなく、従って、処理ステップを全く追加せずに必要とする面積を最小化するように、更に改良するために、前記ソース端子(14)と前記基板端子(18)との間の電位差レベルが約0.5ボルト以下、特に、約0.3ボルト以下であり、ドレイン端子(16)とソース端子(14)とが異なる電位に置かれ、そしてドレイン−ソース電圧及び/又はゲート−ソース電圧を調節することによって、ソース(S)とドレイン(D)との間に荷電キャリアのフローを生じさせ、ソース(S)とドレイン(D)との間で半導体材料(20)を加熱して局所的に融解し、ソース(S)とドレイン(D)との間に少なくとも1個の固定伝導チャネルを形成することが提案される。  (もっと読む)

(もっと読む)

半導体装置

【課題】ラッチアップの発生を防止しつつ、構造の微細化が可能な半導体装置を提供する。

【解決手段】相補型電界効果型トランジスタを含む半導体装置において、寄生的に形成されるバイポーラトランジスタのエミッタ電極となるp型不純物拡散領域5aと、電源供給線14と電気的に接続されているn型不純物拡散領域3とを、n型不純物を有する高融点金属シリサイドからなる接続配線40により接続する。

(もっと読む)

スタティック型半導体記憶装置

【課題】スタティック型半導体記憶装置のメモリセルのトランジスタの基板電圧を、早いタイミングで所定電圧レベルに駆動し、スタティック・ノイズ・マージンを十分に確保し、安定にデータの読出を行なう。

【解決手段】メモリセルの負荷トランジスタ(PQ1,PQ2)の基板領域へ印加される基板電圧(VPS)の遷移を、遅くともワード線(WL)の選択状態への駆動タイミングまでのタイミングに設定する。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】 同一半導体基板上にメモリセルとショットキーバリアダイオードを混載した、ショットキーバリアダイオードのガードリング層によって形成される寄生バイポーラトランジスタによる電流損失を抑制した高信頼度の半導体装置を提供する。

【解決手段】 第1導電型の半導体基板1上に、メモリセルを形成するためのメモリセル領域と、ショットキーバリアダイオードを形成するためのショットキーバリアダイオード領域を相互に分離して備え、メモリセルを構成するトランジスタの閾値電圧を不純物濃度により調整するためのトランジスタのチャンネル領域に形成された第1導電型の不純物拡散層5と、ショットキーバリアダイオードのショットキーバリアを形成する第1導電型と異なる第2導電型の不純物拡散層4の表面の周囲に第1導電型の不純物拡散層で形成されたガードリング層6を、同一工程で同時に形成された不純物拡散層とする。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】寄生容量を低減化,カップリング容量比を向上し、書き込み/消去電圧を低圧化できる。

【解決手段】pウェル領域2と、n+領域5と6間のウェル領域に跨ってゲート絶縁膜12を介して形成された選択ゲート電極(SG)と、n+領域6と接するドレイン電極Dとからなる選択トランジスタと、n+領域1と、n+領域5と電気的に接続し、n+領域1と離間するn+領域4と、n+領域1の上のトンネル絶縁膜8と、n+領域1からn+領域4の上面に跨って形成されたゲート絶縁膜12と、ゲート絶縁膜よりも厚い選択絶縁膜10と、トンネル絶縁膜,ゲート絶縁膜,および選択絶縁膜上のフローティングゲート電極(FG)と、選択絶縁膜上に形成され、FGと側方で対向して形成されたコントロールゲート電極(CG)とからなるメモリトランジスタと、選択絶縁膜を挟んでFGと対向するフローティングのn+領域1が形成される不揮発性半導体記憶装置および製造方法。

(もっと読む)

半導体記憶装置

【課題】ソフトエラーを防止しつつ小型化を図ることが容易な半導体記憶装置を提供すること。

【解決手段】ボトムウェル3と、該ボトムウェルよりも不純物の注入深さが浅い複数のウェル5p,5nとを有する半導体記憶装置10を構成するにあたり、複数のウェルの各々はメモリセルアレイMCAを平面視上横切るようにして互いに平行に配置し、メモリセルアレイでのセル配列構造は、複数のバリューセルCvが配置されたバリューセル領域Vを複数のダミーセルCdが配置されたダミーセル領域Dで取り囲んだ構造とし、平面視したときに、バリューセル領域はボトムウェルに含まれ、かつボトムウェルの縁はダミーセル領域の下に位置するように、ボトムウェルの形状および大きさを選定する。

(もっと読む)

半導体装置

【課題】

寄生のサイリスタを有した半導体装置のラッチアップを防ぐ。

【解決手段】

ソース領域17と前記ドレイン領域14とを跨ぐ方向に直交する方向において、チャネル領域の幅Y2は、前記ドレイン領域14の幅Y1よりも狭く形成される。この場合、チャネル部分に流れる電流のみが抑制され、ドレイン領域14の抵抗値を大きくしないでラッチアップを防ぐことができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】寄生バイポーラとしての動作を防止でき、かつ高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】支持基板1と埋め込み絶縁層2と半導体層3とからSOI基板が構成されている。1poly型メモリセル10は、1対のソース/ドレイン領域11と、フローティングゲート電極層13と、コントロールゲート用不純物拡散領域14とを有している。分離絶縁層6は、半導体層3の表面から埋め込み絶縁層2に達しながらコントロールゲート用不純物拡散領域14の周囲を取り囲むことで、ソース/ドレイン領域11が形成された領域とコントロールゲート用不純物拡散領域14とを分け隔てている。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置のレイアウト効率を向上させる。

【解決手段】CMOS回路を構成する一方のトランジスタTpの配置されたn型ウエル2と電源電圧線Vddとをスイッチ用トランジスタTpsを介して電気的に接続し、かつ、CMOS回路を構成する他方のトランジスタTnの配置されたp型ウエル3と電源電圧線Vssとをスイッチ用トランジスタTnsを介して電気的に接続する構成とした。そして、半導体集積回路装置の試験時には、スイッチ用トランジスタTps,Tnsをオフし、n型ウエル2およびp型ウエル3に対して外部から試験に適した電位を供給してリーク電流に起因する熱暴走を抑制する一方、半導体集積回路装置の通常動作時には、スイッチ用トランジスタTps,Tnsをオンしてn型ウエル2およびp型ウエル3をそれぞれ電源電圧Vdd,Vssに設定してラッチアップを防止する。

(もっと読む)

半導体記憶装置

【課題】リークパスの形成を防止できる半導体記憶装置を提供する。

【解決手段】入力保護回路は、P型半導体基板711と、そのP型半導体基板711の表面に形成されたP+型ウェル領域720と、P+型ウェル領域720と電気的に接続するとともにP+型ウェル領域720よりも深くなるようにP型半導体基板711の表面に形成されたP-型ウェル領域713と、P-型ウェル領域713を覆うようにP型半導体基板711の表面に形成されたN-型ウェル領域714とを含んでいる。

(もっと読む)

CMOS半導体装置の製造方法

【課題】 微細化するCMOS半導体集積回路におけるラッチアップ耐性を向上させる。

【解決手段】 半導体基板1上にパターン化されたマスク層11を形成する工程と、マスク層11をマスクとし、半導体基板1の表面に対する垂線に対して所定の角度をもって入射する不純物イオン12を半導体基板1に注入してCMOS回路を構成するウエル2を形成する工程とを含み、不純物イオン注入は、半導体基板1に対して異なる方向から複数回行われる。これにより、レジストなどのマスク層11による注入イオン12の入射阻害に基づくシャドーイングを抑制することができ、ウエル端部に生じる不純物濃度不足による高抵抗層の発生をなくし、ラッチアップ耐性を改善することができる。また、その構成から明らかなように新たな工程を追加しないので製造コストを上昇させることがない。

(もっと読む)

1 - 20 / 24

[ Back to top ]