Fターム[5F083HA03]の内容

Fターム[5F083HA03]の下位に属するFターム

バイアス発生部

ポンピング部 (1)

Fターム[5F083HA03]に分類される特許

1 - 18 / 18

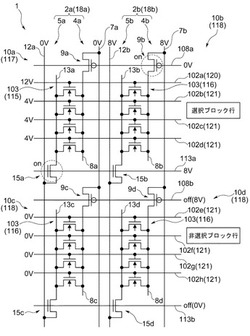

不揮発性半導体記憶装置

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減する。

【解決手段】内部回路(LK#2)の内部ノードに対応して対応の内部ノードの信号をラッチする複数のラッチ回路(F1−F7)をテストパス(302)に配置する。内部回路のMISトランジスタは、ラッチ回路のMISトランジスタよりスタンバイ状態時にゲートトンネル電流が低減される状態に設定される。

(もっと読む)

半導体装置およびそれを用いた半導体集積回路

【課題】バックゲートを有するMOSを、回路の動作特性に応じて使い分け、幅広い温度範囲にて高速かつ低電力なLSIを実現する。

【解決手段】薄膜埋め込み酸化膜層を持つFD−SOIを使用し、薄膜埋め込み酸化膜層の下層半導体領域をバックゲートとし、論理回路ブロックにおいてブロック中の負荷の軽い論理回路にはバックゲートの電圧をブロック活性化に合わせてブロック外から制御する。このバックゲート駆動信号を発生する回路、及び回路ブロック出力部など負荷の重い論理回路には、ゲートとバックゲートとを接続したトランジスタを用い、そのゲート入力信号でバックゲートを直接制御する。

(もっと読む)

3次元メモリー装置、及びそのプログラム方法

【課題】集積度の増加と共にプログラムディスターバンス問題を効果的に減らすことができる3次元メモリー装置、及びそのプログラム方法が提供される。

【解決手段】本発明の3次元メモリー装置は、複数のワードライン平面が積層されたメモリーセルアレイ、選択されたワードライン平面に具備された少なくとも2以上のページのメモリーセルを同時にプログラムする書込み読出し回路、そして前記書込み読出し回路のプログラム動作を制御する制御回路を含むことができる。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】信頼性の高い不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】メモリストリングMSは、基板Baに対して垂直方向に延びる柱状部35aを含むU字状半導体層35と、柱状部35aの側面を取り囲むようにブロック絶縁層34aを介して形成され、且つ積層方向に所定ピッチをもって複数形成された、メモリトランジスタMTrのフローティングゲートとして機能する浮遊電極層34baと、浮遊電極層34baを取り囲むようにトンネル絶縁層35cを介して形成され、メモリトランジスタMTrの制御電極として機能する複数の第1〜第4ワード線導電層31a〜31dとを備える。浮遊電極層34baの積層方向の長さは、第1〜第4導電層31a〜31dの積層方向の長さよりも短い。

(もっと読む)

スタティック型半導体記憶装置

【課題】スタティック型半導体記憶装置のメモリセルのトランジスタの基板電圧を、早いタイミングで所定電圧レベルに駆動し、スタティック・ノイズ・マージンを十分に確保し、安定にデータの読出を行なう。

【解決手段】メモリセルの負荷トランジスタ(PQ1,PQ2)の基板領域へ印加される基板電圧(VPS)の遷移を、遅くともワード線(WL)の選択状態への駆動タイミングまでのタイミングに設定する。

(もっと読む)

半導体回路

【課題】高速のスイッチング特性と小サブスレッショルド電流特性とが両立可能なMOS−FETで構成される半導体回路を提供する。

【解決手段】MOS−FETQ1,Q2により構成される論理回路1を有した半導体回路において、MOS−FETQ1,Q2のバックゲートバイアス電圧Vcc,VSSとは異なる電圧Vpp,Vbbを供給する電圧供給手段15,13と、MOS−FETQ1,Q2のバックゲートバイアス電圧を、電圧Vcc,VSSと電圧Vcc,VSSとは異なる電圧Vpp,Vbbとに切り換えるスイッチング手段10とを備えた構成となっている。

(もっと読む)

半導体装置および半導体装置の制御方法

【課題】薄膜BOX−SOI構造であり、ロジック回路の高速動作とメモリ回路の安定動作とを両立できる半導体装置を提供する。

【解決手段】 本発明に係る半導体装置は、半導体支持基板1、厚さ10nm以下の絶縁膜4、半導体層4を有している。半導体層4の上面内には、第一のゲート電極20を有し、ロジック回路を構成する第一の電界効果型トランジスタが形成されている。また、半導体層4の上面内には、第二のゲート電極を有し、メモリ回路を構成する第二の電界効果型トランジスタが形成されている。半導体支持基板1には、導電型の異なるウェル領域6,6T,7等が、少なくとも3以上形成されている。そして、当該ウェル領域により、第一のゲート電極の下方の半導体支持基板1の領域と、第二のゲート電極の下方の半導体支持基板1の領域とが、電気的に分離される。

(もっと読む)

不揮発性半導体メモリ及びデータプログラム/消去方法

【課題】電荷トラップ型の不揮発性半導体メモリにおいて、消費電流を低減すること。

【解決手段】不揮発性半導体メモリは、半導体基板1、第1ゲート電極WG、第2ゲート電極CG、電荷トラップ膜22、及びトンネル絶縁膜23を備える。第1ゲート電極WGは、半導体基板1の表面上に第1ゲート絶縁膜10を介して形成される。第2ゲート電極CGは、半導体基板1の表面上に第2ゲート絶縁膜20を介して形成され、第1ゲート電極WGと絶縁膜20を介して隣接する。電荷トラップ膜22は、半導体基板1と第1ゲート電極WGと第2ゲート電極CGとに囲まれたトラップ領域RT中に少なくとも形成される。トンネル絶縁膜23は、電荷トラップ膜22と第2ゲート電極CGとの間に形成される。プログラムあるいは消去において、FNトンネル方式により、第2ゲート電極CGから電荷トラップ膜22へトンネル絶縁膜23を通して電子が注入される

(もっと読む)

不揮発性メモリ素子のプログラム方法

【課題】不揮発性メモリ素子のプログラム方法を提供する。

【解決手段】(イ)メモリセルにプログラム電圧を印加し、次いで、第1検証電圧で検証する第1プログラミングステップと、(ロ)第1検証電圧を利用した検証を通過したメモリセルに電荷の安定化を促進するための摂動パルスを印加するステップと、

(ハ)摂動パルスの印加後に第1検証電圧より高い第2検証電圧で検証するステップと、を含むことを特徴とする不揮発性メモリ素子のプログラム方法である。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】バリッドビットにおける無効化処理において、電源投入時に無効化処理を行うことができる半導体記憶装置を提供する。

【解決手段】第1のトランジスタと、第2のトランジスタと、を有する第1のインバータ回路と、入力部が前記第1のインバータ回路の出力部に接続され、出力部が前記第1のインバータの入力部に接続され、第3のトランジスタと、第4のトランジスタと、を有する第2のインバータ回路と、を含む初期化用メモリセルを有し、第3のトランジスタのしきい値電圧の絶対値は、第1のトランジスタのしきい値電圧の絶対値より低い構成とする。

(もっと読む)

不揮発性半導体メモリ

【課題】ゲート間絶縁膜に発生するリーク電流の増大なく、カップリング比を向上させる。

【解決手段】本発明の例に係る不揮発性半導体メモリは、第1及び第2拡散層12,13と、第1及び第2拡散層12,13の間に形成されるチャネルと、チャネル上に形成されるゲート絶縁膜14と、ゲート絶縁膜14上に形成されるフローティングゲート電極15と、フローティングゲート電極15上に形成されるゲート間絶縁膜16と、ゲート間絶縁膜16上に形成されるコントロールゲート電極17とを備え、ゲート間絶縁膜16のチャネル長方向の端部がフローティングゲート電極15の側面又はコントロールゲート電極17の側面よりも内側に存在する。

(もっと読む)

半導体集積回路とその製造方法

【課題】高い製造歩留を可能とすると伴に、CMOS・SRAMのMOSトランジスタのしきい値電圧のバラツキを補償すること。

【解決手段】SRAMの情報保持動作と書き込み動作と読み出し動作のいずれかのアクティブモードで基板バイアス電圧Vbp、VbnがSRAMメモリセルのMOSトランジスタの基板(ウェル)に印加される。まず、SRAMのPMOSとNMOSのトランジスタのしきい値電圧が測定される。測定結果に応じて、制御メモリCnt_MM1、2の制御情報Cnt_Sg1、2がプログラムされる。プログラムにより基板バイアス電圧Vbp、Vbnのレベルが調整されて、CMOS・SRAMのMOSトランジスタのしきい値電圧のバラツキは、所定の誤差範囲に制御される。MOSトランジスタのソースに印加される動作電圧に対してMOSトランジスタの基板には、逆バイアスまたは極めて浅い順バイアスの基板バイアス電圧が印加される。

(もっと読む)

垂直ナノチューブを用いる不揮発性スイッチング装置及びメモリ装置とそれらの形成方法

【課題】不揮発性で輻射堅牢なスイッチング及びメモリ装置(225)と、この装置を製造する方法とを提供する。

【解決手段】装置は、垂直ナノチューブ(155)を使用し、ファンデルワールス力により可逆的に状態が保持される。装置の状態を検知するための手段は、キャパシタンス、及びトンネル電流及び電界放出電流を測定することを含む。

(もっと読む)

半導体メモリデバイス

【課題】 広い温度範囲に亘り高速で操作可能な半導体デバイスを提供すること、半導体メモリデバイスが温度変化の影響を受けなくなるよう半導体デバイスを操作する方法を提供することである。

【解決手段】 本発明においては、半導体メモリデバイスが、その半導体メモリデバイスで測定された上昇した温度に依存する上昇した電圧を出力する温度依存電圧源を備える。少なくとも一つのメモリセルには少なくとも一つの第1のトランジスタが設けられており、第1のトランジスタが第1のトランジスタ本体を含む。第1のトランジスタ本体は温度依存電圧源の出力に接続されている。

(もっと読む)

半導体装置およびそれを用いた半導体集積回路

【課題】バックゲートを有するMOSを、回路の動作特性に応じて使い分け、幅広い温度範囲にて高速かつ低電力なLSIを実現する。

【解決手段】薄膜埋め込み酸化膜層を持つFD-SOIを使用し、薄膜埋め込み酸化膜層の下層半導体領域をバックゲートとし、論理回路ブロックにおいてブロック中の負荷の軽い論理回路にはバックゲートの電圧をブロック活性化に合わせてブロック外から制御する。このバックゲート駆動信号を発生する回路、及び回路ブロック出力部など負荷の重い論理回路には、ゲートとバックゲートとを接続したトランジスタを用い、そのゲート入力信号でバックゲートを直接制御する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 微細化に有利な、二重ウェル、及びこの二重ウェルから離れたウェルを備えた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1導電型の半導体基板1内に形成された第1導電型の第1ウェル10と、第1ウェル10に形成された複数のメモリセルトランジスタQ5−1、Q5−2と、第1ウェル10の側面領域を囲む第1部分7、及び第1ウェル10の下部領域を囲む第2部分9を有し、第1ウェル10を半導体基板1から電気的に分離する第2導電型の第2ウェルと、半導体基板1内に形成された第2導電型の第3ウェル領域5と、を備える。そして、第3ウェル5の深さL1を、第2ウェルの第2部分9の深さL2よりも浅くする。

(もっと読む)

半導体記憶装置及び半導体集積回路

【課題】安定な動作が可能な半導体記憶装置を提供する。

【解決手段】本発明に係る半導体記憶装置は、FBC1と、NFET2及びPFET3を有する周辺回路4とをSOI基板5上に、絶縁層6で分離して形成したものである。SOI基板5は、N基板7上に形成されるN拡散層8と、N拡散層8の一部に形成されるP拡散層9と、N拡散層8及びP拡散層9の上面に形成される薄膜状の埋め込み酸化膜10とを有する。PFET3の下方にN拡散層14を、NFET2の下方にP拡散層12を配置するため、NFET2やPFET3のバックチャネルを確実にオフでき、埋め込み酸化膜10が薄いPD-SOI上にFBC1を配置する場合にも周辺回路4を安定に動作させることができる。

(もっと読む)

1 - 18 / 18

[ Back to top ]