Fターム[5F083LA12]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019) | ビット線 (1,534)

Fターム[5F083LA12]の下位に属するFターム

オープンビット線 (46)

折り返し(フォールディッド)ビット線 (43)

交差型(ツイスティッド)ビット線 (22)

Fターム[5F083LA12]に分類される特許

1,421 - 1,423 / 1,423

半導体記憶装置

【課題】 多ビットのデータを入出力可能であって、動作速度の遅延や消費電力の増大を抑えたDRAMを提供する。

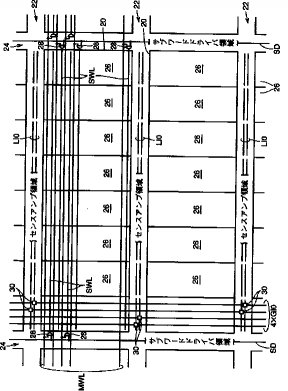

【解決手段】 このDRAMでは、多数のグローバル入出力線対GIOがサブワードドライバ領域24間のメモリセルアレイ上を走る。ローカル入出力線対LIOはメモリサブブロック26ごとに複数に分割される。グローバル入出力線対GIOとローカル入出力線対LIOを接続するスイッチング素子30はセンスアンプ領域22上に分散して配置される。1つのローカル入出力線対LIOには複数のビット線対が共通に接続される。

(もっと読む)

不揮発性半導体記憶装置

【課題】NANDセル型EEPROMのデータ消去後に、ビット線コンタクト部とセルPウエルとの接合の順方向電流によるラッチアップを防止する。

【解決手段】NANDセル型EEPROMにおいて、浮遊ゲートおよび制御ゲートを有する不揮発性のメモリセルを少なくとも1つ含むメモリセルユニットと、メモリセルユニットが形成されるメモリセルウエルCPWELL、CNWELLと、メモリセルユニットの一端に接続された第1の信号線BLi と、メモリセルユニットの他端に接続された第2の信号線CELSRCと、メモリセルの記憶データを消去する際、メモリセルウエルに消去電圧を所定期間印加して消去動作を行わせた後、第1の信号線および第2の信号線をフローティング状態にして、メモリセルウエルの消去電圧を放電させるように制御する制御回路を具備する。

(もっと読む)

半導体メモリーセル

【課題】 データに応じた電荷が、ランダムアクセス等に起因する干渉によってリークしないようする。

【解決手段】 書込ワード線WWrdの指示によって書込ビット線WBitのレベルに対応して電荷を蓄積する一方、読出ワード線RWrdの指示によって蓄積した電荷に応じて読出ビット線RBitのレベルを遷移させる半導体メモリーセルにおいて、書込ワード線WWrdを、接地線GNDと読出ワード線RWrdとの間に配列させる。

(もっと読む)

1,421 - 1,423 / 1,423

[ Back to top ]