Fターム[5F083LA14]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019) | ビット線 (1,534) | 折り返し(フォールディッド)ビット線 (43)

Fターム[5F083LA14]に分類される特許

1 - 20 / 43

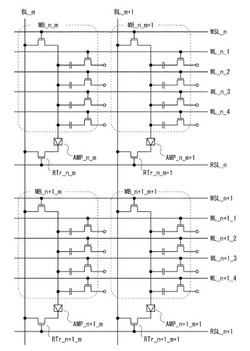

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。第n行のメモリブロックはサブビット線SBL_n_mと複数のメモリセルを有する。メモリセルはトランジスタと容量素子を直列に接続し、容量素子の電極の一をサブビット線SBL_n_mに接続する。さらに第n行のメモリブロックは書き込みトランジスタWTr_n_mと読み出しトランジスタRTr_n_mを有し、また、読み出しトランジスタRTr_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの電位変動を増幅回路AMP_n_mで増幅する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

高速OTP感知スキーム

【課題】不揮発性メモリアレイのための高速感知スキームを提供する。

【解決手段】メモリアレイは、ビット線をVSSなどの第1電圧レベルまで予備充電するための予備充電回路を備えた、相補形ビット線構成で配置された不揮発性メモリセルと、相補形ビット線対の基準ビット線に基準電荷を印加するための基準回路と、相補形ビット線対の間の電圧差を感知するためのビット線感知増幅器とを備えている。データビット線の電圧は、起動されたワード線に接続されたプログラム済みの不揮発性メモリセルがワード線電圧をデータビット線に結合すると変化する。

(もっと読む)

半導体記憶装置

【課題】半導体集積回路の面積を節約するために、複数の拡散層を共有化すると、それらの拡散層に接続された配線に対する寄生容量が変化する。それでも、複数の拡散層に接続された対となる配線のそれぞれにおける容量負荷のバランスが保たれる半導体レイアウトを提供する。

【解決手段】対となる配線のそれぞれが接続される拡散層を交互または互い違いに配置することで、対となる配線のそれぞれにおける容量負荷の総量のバランスを保つ。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

半導体記憶装置

【課題】CMOSプロセスで、ダイナミック型半導体記憶装置を形成し、ロジックとの混載に適したダイナミック型半導体記憶装置を実現する。

【解決手段】メモリセル(MC)のワード線(WL)を形成する導電線(3)とメモリセルセルプレート電極(CP)を形成する導電線(5)とを、異なる配線層に形成する。対をなすビット線に並行してメモリセルを接続し、2つのメモリセルで1ビットのデータを記憶する。

(もっと読む)

半導体装置

【課題】ビット線が階層構造を有する半導体装置を改良する。

【解決手段】同時にアクセスされる2つのメモリセルMC(a),MC(b)に対するセンス動作を2つのセンスアンプSA0,SA0Aを用いて時分割で行い、その後、リストア動作を同時に行う。これにより、グローバルビット線GBLT0,GBLB0の途中にスイッチを介在させる必要がなくなるとともに、時分割でリストア動作を行う場合の問題が生じない。また、センスアンプSA0とセンスアンプSA0Aの寄生CRモデルが互いに同じとなることから、高いセンス感度を確保することも可能となる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ノイズに対して強い耐性を有するメモリ回路を含む半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1及び第2の方向に沿って行列状に配置された複数のメモリセルと、複数のセンスアンプと、第2の方向に延在する複数のワード線と、第1の方向に延在する複数のビット線とを有し、複数のメモリセルは、第2の方向に沿って延在する第1の補助ワード線をゲート電極として共有する第1のメモリセル群と、第1のメモリセル群と第2の方向に隣接して配置され、第2の方向に沿って延在する第2の補助ワード線をゲート電極として共有する第2のメモリセル群とを含み、第1及び第2のワード線が、それぞれ、第1及び第2の補助ワード線の一端に配置されたワード線コンタクト領域で、第1及び第2の補助ワード線に接続され、第1及び第2のビット線が、ワード線コンタクト領域を挟んで隣接し共通のセンスアンプに接続されている。

(もっと読む)

半導体集積回路装置

【課題】雑音特性が優れ、かつサイズが小さいメモリアレイ及びそのメモリアレイを備えた半導体集積回路装置を提供する。

【解決手段】ビット線と定電圧との間に、順番に直列に接続された2つのトランジスタと1つの記憶蓄積素子とを備えたメモリセルは、2つのトランジスタのゲート電極に第1のワード線、第2のワード線がそれぞれ接続され、メモリアレイは、メモリセルがビット線と第1のワード線が交差する全ての交点に配置されたマットと、同一マット内のビット線対を入力とするセンスアンプと、第1及び第2のワード線を出力する第1及び第2のワードドライバと、を備える。

(もっと読む)

半導体装置とその製造方法

【課題】

ロジックプロセスと適合性が高く、ノイズに対して強い耐性を有するメモリ回路を含む半導体装置とその製造方法を提供する。

【解決手段】

半導体装置は、複数のメモリセルが第1および第2の方向に沿って行列状に配置されたメモリセルアレイ、および第1および第2のセンスアンプを含む複数のセンスアンプ、を形成した半導体基板を含み、メモリセルの各々は絶縁ゲート電極とその両側に形成されたビット線コンタクト領域と他のソース/ドレイン領域を備えたトランジスタと、他のソース/ドレイン領域に接続されたキャパシタとによって構成される。メモリセルアレイ上方に、第1の方向に沿って延在し、複数のビット線コンタクト了以金に接続され、第2の方向に並んで配置された複数のビット線を含む。第1のセンスアンプに接続される第1対のビット線は、第1配線層で形成され、第2のセンスアンプに接続される第2対のビット線は、第1の配線層と異層の第2配線層で形成される。

(もっと読む)

半導体装置

【課題】信号配線領域の大幅な増大をともなうことなく、信号配間に生じるカップリングノイズの低減を実現した半導体装置を提供する。

【解決手段】信号線が並行配置される場合において、当該信号線の全てが片側の信号線だけからのみカップリングノイズを受ける構成とするため、当該複数の信号線の両側において他の信号線と対向しないように、その信号線の片側一方にのみ電源電位、接地電位又は当該信号線がカップリングノイズを受ける期間において一定電位に維持される配線を配置する。

(もっと読む)

半導体集積回路および半導体記憶装置

【課題】チップの内部バスやチップ間を接続する外部バスにおける消費電力の低減や、データ転送速度の向上を実現する。

【解決手段】論理レベル‘H’か‘L’かその中間レベルとなる‘M’を採り得る複数本のバスDB[0]〜DB[n−1]と、データD[0]〜D[m−1]を符号化し、これに基づいて複数本のバスのそれぞれを論理レベル‘H’、‘L’、‘M’のいずれかに駆動する送信回路TXと、複数本のバスを互いにショートするバスイコライズ回路BEQを設ける。送信回路TXは、データの符号化を行う際に、論理レベル‘H’に駆動するバスの本数(k本)と論理レベル‘L’に駆動するバスの本数(k本)が同数となるような組み合わせを用いる。バスイコライズ回路BEQは、データが送信された後にショート動作を行うことで、各バスを論理レベル‘M’にプリチャージする。

(もっと読む)

半導体記憶装置

【課題】微細化しても信号量の差を低下させず、データの誤検出を抑制することができる半導体記憶装置を提供する。

【解決手段】強誘電体メモリは、互いに並列に接続された強誘電体キャパシタおよびセルトランジスタを含むメモリセルが複数個直列に接続されて構成されたセルブロックと、セルトランジスタのゲートに接続されたワード線と、セルブロックの一端に接続されたブロック選択部と、ブロック選択部を介してセルブロックの一端に接続された複数のビット線と、セルブロックの他端に接続されたプレート線とを備え、ワード線を共有する第1および第2のセルブロックの各一端は、互いに異なるブロック選択部を介して、同一のビット線に接続されており、第1および前記第2のセルブロックの各他端は、互いに異なるプレート線に接続されている。

(もっと読む)

半導体記憶装置

【課題】メモリセルに含まれる選択トランジスタのゲート配線のピッチに対する上層の杭打用金属配線ピッチの影響を低減する。

【解決手段】メモリセルアレイ(1)の両側にワード線ドライブ回路(2R,2L)を対向して配置し、各ワード線ドライブ回路には、ワード線ドライバをメモリセル行に対して交互に配置する。メモリセルの選択トランジスタのゲート配線(PGo,PGe)は、各メモリセル行に対応して配置される。杭打用の上層の金属配線(MLo,MLe)は、対向配置されるワード線ドライブ回路からメモリセルアレイの中央部の接続領域(10)まで延在させ、接続領域においてゲート配線に交互に電気的に接続する。金属配線は、ゲート配線の2倍のピッチで対向して配置する。

(もっと読む)

半導体装置

【課題】電源電圧の変化、温度変化に対してタイミング変動の小さいタイミング制御回路、及び該回路を備えた半導体装置の提供。

【解決手段】入力クロックを用いた第1のクロック生成回路、及び第2のクロック生成回路と、前記第1のクロック信号と、前記第2のクロック信号と、コマンドデコーダから活性化信号と、タイミングレジスタから遅延時間を選択する選択信号とを受け、前記活性化信号の活性化から、前記選択信号によって規定される、前記第1の周期の所定倍(m)の時間と、前記第2の周期の所定倍(n)の時間とを合成した時間に対応したタイミング生成回路とを備え、タイミングレジスタはm、nの値を記憶し、タイミングレジスタに記憶するのは、モードレジスタセットコマンドの時の初期化シーケンスで実施する。動作状態では、前記のタイミングレジスタに記憶した情報をもとに、タイミング生成回路から所望のタイミングで、タイミング信号を出力する。

(もっと読む)

半導体装置

【課題】極めて微細なピッチで配列される回路ブロックにおいてレイアウト面積を低減することができる半導体装置を提供する。

【解決手段】一定のピッチにて配列された複数のビット線BL,/BLと、ビット線BL,/BLに接続されたものであって、互いに直列接続された第1及び第2のMOSトランジスタQn1及びQn3と、第1及び第2のMOSトランジスタを直列に接続する節点を形成するものであって、第1及び第2のMOSトランジスタのドレイン・ソース領域を絶縁層に設けられたコンタクト開口部102を介して導電層にて接続する島状のタングステン配線N1とを備えた半導体装置。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】スタンバイリークを低減できる半導体記憶装置(SRAM)を提供する。

【解決手段】1つのメモリセルが、第1及び第2ドライバトランジスタ、第1及び第2ロードトランジスタ、第1及び第2転送トランジスタの6個のトランジスタを有し、第1記憶ノードNDに第1転送トランジスタTTr1を介してビットラインBLが接続され、第2記憶ノードNDに第2転送トランジスタTTr2を介して反転ビットラインBLが接続された構成において、ビットライン印加電圧がロードトランジスタに印加される電源電圧より低く、少なくとも、第1及び第2ドライバトランジスタDTr1,DTr2を構成するゲート絶縁膜の記憶ノード側端部、第1及び第2ロードトランジスタLTr1,LTr2を構成するゲート絶縁膜の記憶ノード側端部が他の部分のゲート絶縁膜より厚膜化されている構成とする。

(もっと読む)

半導体記憶装置

【課題】配線ピッチが微細化した場合などでも読み出し電圧を確保する。

【解決手段】サブビット線SBL00〜SBLn3等は、第1メタル(第1金属配線層)で形成されている。一方、メインビット線は、第2、第3メタル(第2、第3金属配線層)に分散して形成されている。これにより、メインビット線のカップリング容量やオーバラップ容量が小さく抑えられ、カップリングノイズの影響も低減される。

(もっと読む)

半導体素子及びその製造方法

【課題】高い信頼性を有するDRAMの半導体素子、及びその製造方法を提供する。

【解決手段】半導体素子は、基板100上のワードラインとなるゲート電極115と、ゲート電極115の側壁スペーサ118と、側壁スペーサ118によってゲート電極115から分離され、基板の不純物領域120と電気的に連結されたコンタクト160と、コンタクト160に電気的に連結されたコンタクトパッド165と、コンタクトパッド165の側面と接し、コンタクトパッド165の間に配置された保護パターン145と、コンタクトパッド165上のストレージノード170と、を含む。コンタクトパッド165は、対向するストレージノード170の底表面170bsより広い面積を有する上部表面165tsを有するように形成できるので、コンタクトパッド165の上部表面165tsは、ストレージノード170に対して十分なアライメントマージン。

(もっと読む)

半導体集積回路装置及びそのレイアウト方法

【課題】ノイズによる誤動作を従来よりも低減すること。

【解決手段】メモリマクロ1は、複数のメモリセル3を含むメモリセルアレイ2と、メモリセル3に接続された相補デジット線対DTj、DBjと、相補デジット線対DTj、DBjに接続されたカラム系周辺回路6とを備えている。通過配線20−1〜20−Mは、メモリマクロ1上の相補デジット線対DTj、DBjに対して垂直に交差する方向に設けられる。メモリマクロ1の相補デジット線対DTj、DBjに水平な部分の長さをYとし、部分Yのうちの、メモリセルアレイ2、カラム系周辺回路6の幅に対応する長さをそれぞれYa、Ybとしたとき、Mが(Ya+Yb)/Yb以上である場合、カラム系周辺回路6上に設けられる通過配線を禁止するために、通過配線20−1〜20−Mの全てがメモリセルアレイ2上に均等に配置される。

(もっと読む)

半導体記憶装置

【課題】通常のCMOSプロセスにおいてDRAMを作製でき、低い製造コストで製造可能なDRAMの混載した半導体記憶装置を提供する。

【解決手段】半導体基板上に形成された第1及び第2のトランジスタT1、T2と、セルデータ電荷を保持するための2つのノードSNt、SNcと、周囲に形成されたシールド電極により構成される1ビットのメモリセル11領域であって、各々のノードSNt、SNcは第1、第2のトランジスタT1、T2のドレインに接続されており、第1及び第2のトランジスタT1、T2のゲートはともに同一のワード線WL0に接続されており、第1及び第2のトランジスタT1、T2のソースは第1、第2のビット線BLt0、BLc0に接続され、第1及び第2のビット線BLt0、BLc0は、同一のセンスアンプSA12に接続され、1ビットのメモリセル領域が2次元的にアレイ状に形成される。

(もっと読む)

1 - 20 / 43

[ Back to top ]