Fターム[5F083LA15]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019) | ビット線 (1,534) | 交差型(ツイスティッド)ビット線 (22)

Fターム[5F083LA15]に分類される特許

1 - 20 / 22

半導体メモリ装置およびその駆動方法

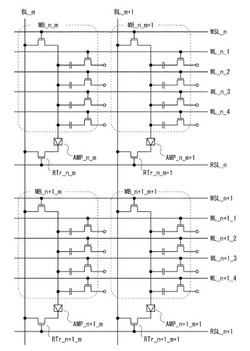

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。第n行のメモリブロックはサブビット線SBL_n_mと複数のメモリセルを有する。メモリセルはトランジスタと容量素子を直列に接続し、容量素子の電極の一をサブビット線SBL_n_mに接続する。さらに第n行のメモリブロックは書き込みトランジスタWTr_n_mと読み出しトランジスタRTr_n_mを有し、また、読み出しトランジスタRTr_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの電位変動を増幅回路AMP_n_mで増幅する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

スタティックランダムアクセスメモリ

【課題】第1の導電型の共通ウェルが形成された半導体基板と、前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成するメモリセルアレイからなるスタティックランダムアクセスメモリにおいて、隣接カラム群間のソフトエラーの伝搬を抑制する。

【解決手段】隣接する第1および第2のカラム群において、前記第1のカラム群CG1で選択される一のメモリセルカラムの第1導電型ウェルPW(01)と、第2カラム群CG2で同時に選択されるメモリセルカラムの第1導電型ウェルPW(05)は、いずれか一方が、共通ウェル11から、第2導電型の深いウェルDNW1により遮断されており、前記第2導電型の深いウェルDNW1は、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

(もっと読む)

半導体装置

【課題】ビット線が階層構造を有する半導体装置を改良する。

【解決手段】同時にアクセスされる2つのメモリセルMC(a),MC(b)に対するセンス動作を2つのセンスアンプSA0,SA0Aを用いて時分割で行い、その後、リストア動作を同時に行う。これにより、グローバルビット線GBLT0,GBLB0の途中にスイッチを介在させる必要がなくなるとともに、時分割でリストア動作を行う場合の問題が生じない。また、センスアンプSA0とセンスアンプSA0Aの寄生CRモデルが互いに同じとなることから、高いセンス感度を確保することも可能となる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ノイズに対して強い耐性を有するメモリ回路を含む半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1及び第2の方向に沿って行列状に配置された複数のメモリセルと、複数のセンスアンプと、第2の方向に延在する複数のワード線と、第1の方向に延在する複数のビット線とを有し、複数のメモリセルは、第2の方向に沿って延在する第1の補助ワード線をゲート電極として共有する第1のメモリセル群と、第1のメモリセル群と第2の方向に隣接して配置され、第2の方向に沿って延在する第2の補助ワード線をゲート電極として共有する第2のメモリセル群とを含み、第1及び第2のワード線が、それぞれ、第1及び第2の補助ワード線の一端に配置されたワード線コンタクト領域で、第1及び第2の補助ワード線に接続され、第1及び第2のビット線が、ワード線コンタクト領域を挟んで隣接し共通のセンスアンプに接続されている。

(もっと読む)

半導体装置とその製造方法

【課題】

ロジックプロセスと適合性が高く、ノイズに対して強い耐性を有するメモリ回路を含む半導体装置とその製造方法を提供する。

【解決手段】

半導体装置は、複数のメモリセルが第1および第2の方向に沿って行列状に配置されたメモリセルアレイ、および第1および第2のセンスアンプを含む複数のセンスアンプ、を形成した半導体基板を含み、メモリセルの各々は絶縁ゲート電極とその両側に形成されたビット線コンタクト領域と他のソース/ドレイン領域を備えたトランジスタと、他のソース/ドレイン領域に接続されたキャパシタとによって構成される。メモリセルアレイ上方に、第1の方向に沿って延在し、複数のビット線コンタクト了以金に接続され、第2の方向に並んで配置された複数のビット線を含む。第1のセンスアンプに接続される第1対のビット線は、第1配線層で形成され、第2のセンスアンプに接続される第2対のビット線は、第1の配線層と異層の第2配線層で形成される。

(もっと読む)

半導体集積回路

【課題】同時に読み書きを行うデュアルポートSRAMにおいて、データの読み出し速度を改善する。

【解決手段】各々のメモリセルは、第1及び第2のストアノードにデータを保持する第1及び第2のインバータと、第1のビット線対と第1及び第2のストアノードとの間にそれぞれ接続された第1及び第2のNチャネルトランジスタによって構成される書き込み/読み出しポートと、第1のストアノードのデータをゲートに受ける第1のPチャネルトランジスタ、第2のビット線対の一方と第1のPチャネルトランジスタのドレインとの間に接続された第2のPチャネルトランジスタ、第2のストアノードのデータをゲートに受ける第3のPチャネルトランジスタ、第2のビット線対の他方と第3のPチャネルトランジスタのドレインとの間に接続された第4のPチャネルトランジスタによって構成される読み出しポートとを具備する。

(もっと読む)

ブースト電圧クランプを改善するためのペアビットラインプログラミング

プログラミング技法は、プログラム外乱を回避するために阻止されたチャネルのクランプブースト電位を上昇させる選択ビットラインパターンを使用してプログラミングすることによって、不揮発性記憶素子のセットでのプログラム外乱を削減する。1つの態様では、隣接するビットラインの交互のペアを第1のセット及び第2のセットにグループ化する。二重プログラミングパルスが、選択されたワードラインに印加される。ビットラインの第1のセットは、第1のパルスの間にプログラミングされ、ビットラインの第2のセットは、第2のパルスの間にプログラミングされる。次に、全てのビットラインに検証動作が実行される。ある特定のビットラインが阻止されると、その隣接ビットラインの少なくとも1つも阻止され、その特定のビットラインのチャネルが十分にブーストされる。別の態様は、2ビットラインおきに別々にプログラミングする。修正されたレイアウトによって、ビットラインの隣接するペアは、奇数−偶数検出回路を使用して検出できる。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】

メモリセルを複数のメモリブロックに分ける分割プリチャージ方式の半導体記憶装置では、データ線DL、反データ線DLBが長くなり、クロストークの影響が大きかった。

【解決手段】

データ線DL、又は反データ線DLBのみからなる列は、相補関係にあるデータ線DLと反データ線DLBとの複合列が隣り合うように配置されることを特徴とする。この場合、各データ線DL、各反データ線DLBの間隔を大きくすることなく、クロストークの影響を半分に減らすことができる。

(もっと読む)

半導体記憶装置

【課題】レイアウトパターンの均一性を高めて製造時の加工バラツキを抑制した半導体記憶装置を提供する。

【解決手段】半導体基板上に形成された1箇所のN型の拡散層ODごとに、ワード線WLまたはビット線選択線KSとの交差位置に、2つのメモリセルゲートTG、またはビット線接続ゲートSWが形成され、N型の拡散層ODの中央部付近は、2つのゲートに共通のソース/ドレイン領域とされる一方、両端部付近は、各ゲートに個別のソース/ドレイン領域とされる。ソース/ドレイン領域は、ストレージコンタクトCAを介して、メモリセルキャパシタのストレージ電極に接続され、またはサブビット線コンタクトCHおよびメタル配線のビアを介して、サブビット線、またはメインビット線に接続される。メモリセルゲートTGおよびビット線接続ゲートSWは、4つ単位で同一のパターンを繰り返すように配置される。

(もっと読む)

半導体装置及びその動作方法

【課題】メモリセルのしきい値電圧のばらつきを減少することができ、誤動作を防止することができる不揮発性記憶回路を備えた半導体装置及びその動作方法を提供する。

【解決手段】3値以上の正数のM値のデータの書き込みが可能なメモリセルが行列状に複数配列されたメモリセルアレイと、メモリセルに接続され、メモリセルアレイ上を第1の方向に延在し、第2の方向に複数本配列されたワード線と、メモリセルに接続され、メモリセルアレイ上を第2の方向に延在し、第1の方向に複数本配列されたビット線と、複数本のビット線毎にそれぞれ配設された複数のセンスアンプ回路と、センスアンプ回路毎にそれぞれ配設されたラッチ回路とを備える。

(もっと読む)

半導体記憶装置

【課題】 微細化された半導体記憶装置のセンスアンプにおいて、トランスファーゲートを使ったクロッキング方式にてセンスアンプ動作させた場合、センスアンプ内部の隣接ノイズが発生し、センススピードの低下、さらには誤動作するという問題がある。

【解決手段】 本発明の半導体記憶装置のセンスアンプは、左右のトランスファーゲート間のほぼ中央位置にあるセンスアンプ内で、ビット線対をツイストさせる。1組おきのビット線対をツイストさせることで、隣接カップリングノイズが相殺される。このようにレイアウト面積の増大を伴うことなく、ビット線対をツイストさせ、センスアンプ内の隣接カップリングノイズの影響を受けなくすることができる高速、安定動作するセンスアンプ、及びこのセンスアンプを備えた半導体記憶装置が得られる。

(もっと読む)

半導体記憶装置

【課題】半導体メモリの階層ビット線構造における階層間の結合容量および隣接配線間の結合容量ノイズを低減することができ、読み出しの高速化、読み出しマージンの向上を図る。

【解決手段】複数の基本単位ブロック1からなる基本単位ブロック列10に対応して設けられたグローバルビット線対GBL,GBLBの電位差を差動型のセンスアンプ11で検知増幅するメモリ回路を備えた半導体記憶装置において、各基本単位ブロック1は、複数のメモリセル2に共通にローカルビット線対LBL、LBLBが接続され、LBL、LBLB対はビット線プリチャージ素子3に接続され、LBL、LBLB対とGBL、GBLB対との接続を制御する転送ゲート用スイッチ素子4を有する。LBL、LBLB対およびGBL、GBLB対は、LBL、LBLB対の上層の配線層でGBL,GBLB対が構成された階層ビット線構造を有し、平行してレイアウトされており、GBL,GBLB対は1回以上交差している。

(もっと読む)

半導体記憶装置

【課題】読出し電流と参照電流との間のマージンを十分な大きさに保つことができ大きな読出し速度を維持することができる。

【解決手段】メモリセルアレイMCAは、複数のワード線WLsと複数のビット線BLsの交点に設けられる複数のメモリセルMCを含んでいる。メモリセルMCの制御ゲートはワード線WLに接続され、メモリセルMCのドレインはビット線BLに接続されている。浮遊ゲートに電子が注入され閾値電圧が高くなった状態が“0”データ、逆に低い状態が“1”データとされる。“1”データの場合には、ビット線BLに電流が流れる。カラムゲート340は、カラムデコーダからのカラムアドレス信号に基づき複数のビット線BLsを同時にデータ線DLsに接続するためのものである。また、カラムゲート340は、複数のビット線BLsのうち隣接するビット線同士を、それぞれ複数のデータ線DLsのうち互いに隣接していないデータ線に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】 ヴィアホールを形成する際にマスクパターンのあわせずれが生じても配線間の寄生容量を抑制できるようにする。

【解決手段】 層間絶縁膜4の面に形成されたシリコン窒化膜6よりも上面が下方に位置するよう配線層5を形成する。これにより、あわせずれが生じても、ヴィアプラグ8と隣接配線層11との間の距離を長く保つことができる。

(もっと読む)

256Megダイナミックランダムアクセスメモリ

【課題】ピンの配置に制約が有る中でのチップの最適レイアウトの実現と、最短の時間でデバイスが適切な動作を行える電源アーキテクチャの提供。

【解決手段】本発明は、複数のアレイブロックと、複数のアレイブロックの中央に配置された複数のパッドとを具えるダイナミックランダムアクセスメモリ用の電源であって、複数のパッドの近傍に配置され、複数のアレイブロックへの供給電圧を生成するための複数の電圧源を具えている。複数の電圧源は、複数の電力増幅器を有する電圧レギュレータを具えており、少なくとも1つの電力増幅器は、複数のアレイブロックの各々と関連付けられている。複数の電圧源は、設定された出力電力レベルを達成するために、別個の又は同時の何れかの動作を行なうために複数のグループに分割された複数の電圧ポンプ回路を有する電圧ポンプを含んでいる。

(もっと読む)

256Megダイナミックランダムアクセスメモリ

【課題】大型メモリチップに対して、動作に応じて最適な内部電圧を供給する。

【解決手段】本発明のダイナミックランダムアクセスメモリは、メモリセルからなる複数の独立アレイを有し、独立アレイはアレイを通って延びるディジット線を有しており、独立アレイは、行と列に配置されて複数のアレイブロックを形成しており、ディジット線を用いて、メモリセルについてデータの書込みとデータの読出しを行なう複数の周辺装置を有しており、複数の供給電圧を生成する電源を有し、該電源は、ディジット線をバイアスするバイアス電圧を生成する複数の発生器を有しており、該発生器の数はアレイブロックの数と同じであり、複数の供給電圧を、複数のアレイブロック及び周辺装置に送給する電力分配バスを有している。

(もっと読む)

半導体記憶装置

【課題】 特にDRAMの微細化に有益となる半導体記憶装置を提供する。

【解決手段】 外部からライトコマンドWRTが入力され、ビット線BLT,BLBの電圧がVDL,VSSとなり、メモリセルトランジスタを介してキャパシタの蓄積ノードSNにそのメモリセルトランジスタのしきい値電圧(LVT:低しきい値電圧、MVT:中しきい値電圧、HVT:高しきい値電圧)に応じた電圧が書き込まれ、その後、キャパシタのプレート側に接続されたプレート線PLが電圧VPLから電圧VPHに駆動され、カップリングによって蓄積ノードSNの電圧が上昇した段階で、ビット線BLTを電圧VDLから電圧VDPに下げ、蓄積ノードSNに過剰に書き込まれた電圧をメモリセルトランジスタのしきい値電圧の大きさに応じて低下させ、しきい値電圧のばらつきに起因した蓄積ノードSNの電圧のばらつきを低減する。

(もっと読む)

半導体記憶装置

【課題】製造時のパターンの合わせずれ等により、メモリセルの特性にばらつきが生じても、正しくデータを読み出すことが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、センスアンプ(S/A)1の両側に配置されたメモリセルアレイ2を有し、メモリセルアレイ2は、複数のワード線WL0,WL1と、ダミーワード線DWLLo,DWLLe,DWLRo,DWLReと、これらワード線およびダミーワード線に交差する方向に配置される複数のビット線BL0〜BL3と、ワード線およびビット線の交点付近に形成されるFBC3,4とを有する。読み出し対象のメモリセル4と対応するダミーセル3のビット線コンタクト21、ゲート22およびソース線コンタクト23の配置順序を揃える。これにより、読み出し対象メモリセル4とダミーセル3とで、電気特性を合わせることができ、メモリセル4のデータを正しく読み出すことができる。

(もっと読む)

半導体メモリ

【課題】セルアレイの増大なく、ビット線ツイスト構造を実現する。

【解決手段】本発明の例に関わる半導体メモリは、第1及び第2ビット線BL0,bBL0と、第1カラム01内に配置される第1セルブロックBKと、第1ビット線BLと第1セルブロックBKとの間に接続される第1ブロックセレクトトランジスタBSTと、第2カラム02内に配置される第2セルブロックBKと、第2ビット線bBLと第2セルブロックBKとの間に接続される第2ブロックセレクトトランジスタBSTとを備える。第1及び第2ビット線BL,bBLは、ビット線ツイスト構造を有し、かつ、第1及び第2ビット線BL,bBLの入れ替えは、ブロックセレクタ領域BSで行われる。

(もっと読む)

半導体メモリ装置

【課題】半導体メモリ装置及びこの装置の信号ライン配置方法を提供する。

【解決手段】サブワードラインとビットライン対との間に接続されるメモリセルを備えたサブメモリセルアレイを備え、ビットライン対とローカルデータラインLIO対、グローバルデータラインGIO対との間にデータを伝送するメモリセルアレイ、及びメモリセルアレイを全体的に覆ってメモリセルに必要な電圧を印加する電極を備えて、ローカルデータラインLIO対が電極の上部の1層にサブワードラインと同じ方向に配置され、コラム選択信号ラインCSL及びグローバルデータラインGIO対が電極の上部の第2層にビットラインと同じ方向に配置され、ワード選択信号ライン及びメインワードラインNWLiが電極の上部の第3層にサブワードラインと同じ方向に配置される。これによって、電極からワードラインに流れる漏洩電流が防げられて電極の電圧レベルの降下を防止できる。

(もっと読む)

1 - 20 / 22

[ Back to top ]