Fターム[5F083LA13]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019) | ビット線 (1,534) | オープンビット線 (46)

Fターム[5F083LA13]に分類される特許

1 - 20 / 46

半導体メモリ装置およびその駆動方法

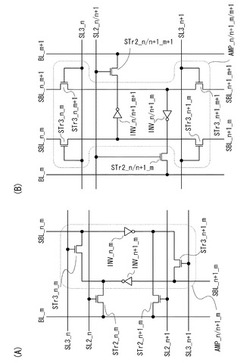

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。メモリブロックMB_n_mはサブビット線SBL_n_mと書き込みスイッチと複数のメモリセルを有する。サブビット線SBL_n_mと隣接するサブビット線SBL_n+1_mは2つのインバータと2つの選択スイッチよりなる増幅回路AMP_n/n+1_mに接続し、増幅回路は選択スイッチによりその回路構成を変更できる。また、増幅回路は読み出しスイッチを介してビット線BL_mに接続する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n/n+1_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。第n行のメモリブロックはサブビット線SBL_n_mと複数のメモリセルを有する。メモリセルはトランジスタと容量素子を直列に接続し、容量素子の電極の一をサブビット線SBL_n_mに接続する。さらに第n行のメモリブロックは書き込みトランジスタWTr_n_mと読み出しトランジスタRTr_n_mを有し、また、読み出しトランジスタRTr_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの電位変動を増幅回路AMP_n_mで増幅する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体記憶装置

【課題】半導体集積回路の面積を節約するために、複数の拡散層を共有化すると、それらの拡散層に接続された配線に対する寄生容量が変化する。それでも、複数の拡散層に接続された対となる配線のそれぞれにおける容量負荷のバランスが保たれる半導体レイアウトを提供する。

【解決手段】対となる配線のそれぞれが接続される拡散層を交互または互い違いに配置することで、対となる配線のそれぞれにおける容量負荷の総量のバランスを保つ。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の作製方法

【課題】高度に集積化したDRAMを提供する。

【解決手段】第1絶縁体101上にビット線102b、ビット線102b上に第2絶縁体103、第2絶縁体103上にストライプ状の第3絶縁体106a乃至106c等を形成し、第3絶縁体106bを覆って、半導体領域109bとゲート絶縁体110を形成する。ビット線102bと半導体領域109bは第1のコンタクトプラグ105a、105bで接続される。その後、導電性膜を形成し、これを異方性エッチングすることで、第3絶縁体106a乃至106cの側面にワード線111a乃至111dを形成し、第3絶縁体106bの頂部にキャパシタへ接続するための第2コンタクトプラグ115bを形成する。ワード線111b、111cを同期させることで、キャパシタに電荷を出入りさせる。このような構造でメモリセルの面積を4F2とできる。

(もっと読む)

半導体メモリ装置

【課題】高度に集積化したDRAMを提供する。

【解決手段】基板201上にメモリセルアレイを駆動するための回路202を形成し、その上にビット線205を形成し、ビット線205上に半導体領域208とワード線210a、210b、キャパシタを形成する。ビット線が半導体領域208の下に位置し、ワード線210a、210b、キャパシタが半導体領域208の上に位置するため、ビット線205の配置の自由度が高まり、オープンビット線型のDRAMとすることで6F2以下、あるいはセルトランジスタの構造を特殊なものとすることで4F2以下とできる。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

半導体装置

【課題】センスアンプのセンスマージンを拡大する。

【解決手段】2つの素子分離領域3に隣接して各ウェル1,2にドライバトランジスタ4a,5a,4b,5bをそれぞれ配置し、各ウェル1,2にドライバトランジスタ4a,5a,4b,5bよりも素子分離領域3a,3bから離れた位置にクロスカップルされた2つの一対のセンストランジスタ6a乃至9a、6b乃至9bをそれぞれ配置する。これにより、センストランジスタ6a乃至9a、6b乃至9bと夫々対応する素子分離領域3a,3bと間に一定以上の距離が確保されることから、素子分離領域3a,3bからの距離によってトランジスタのしきい値が変化する現象の影響が低減され、その結果、夫々クロスカップルされた一対のトランジスタの特性を正確に一致させることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域におけるイオン濃度のばらつきを抑制すること。

【解決手段】半導体装置の製造方法は、半導体基板にイオンを注入するための第1開口を有し、第1層ウェルを形成するための第1マスクを半導体基板上に形成する工程と、第1マスクを用いて半導体基板に第1イオンを注入して、第1領域及び第2領域を有する第1層ウェルを形成する工程と、半導体基板にイオンを注入するための第2開口を有し、第2層ウェルを形成するための第2マスクを半導体基板上に形成する工程と、第2マスクを用いて半導体基板に第2イオンを注入して、第1層ウェルより下方に位置する第2層ウェルを形成する工程と、を含む。第1領域を第2領域より第1層ウェルの外縁寄りに形成する。第1イオンを注入する際に、第1マスクの第1内壁面で反射した第1イオンを第1領域に供給する。第2イオンを注入する際に、第2マスクの第2内壁面で反射した第2イオンを第2領域に供給する。

(もっと読む)

半導体装置及びその製造方法

【課題】更なる微細化に対応した高集積度のDRAMを得ることが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2の表層に、第1の方向Yに延在する第1の溝部3と、第2の方向Xに延在し且つ第1の溝部3よりも深くなる第2の溝部5と、第1の溝部3と第2の溝部5との交差部分において第2の溝部5よりも深くなる第3の溝部7と、第1の溝部3と第2の溝部5との間から突出されたピラー部8と、ピラー部8に形成された下部拡散層9、チャネル領域10及び上部拡散層11と、第2の溝部5の内側において第2の方向Xに延在するビット配線層と、第1の溝部3の内側においてピラー部8の側面を覆うゲート絶縁膜と、第1の溝部3の内側においてゲート絶縁膜を介してピラー部8の側面を横切るように第1の方向Yに延在するワード配線層とを備える。

(もっと読む)

半導体記憶装置

【課題】従来の強誘電体メモリと比べてメモリセルのサイズを縮小し、かつ、メモリ容量を増大させることができる半導体記憶装置を提供する。

【解決手段】メモリは、半導体基板の表面に形成された第1の拡散層と、第1の拡散層上に設けられたボディ領域と、ボディ領域上に設けられた第2の拡散層と、ボディ領域の第1の側面に設けられた強誘電体膜を含む第1のゲート絶縁膜と、ボディ領域の第2の側面に設けられた強誘電体膜を含む第2のゲート絶縁膜と、ボディ領域の第1の側面に第1のゲート絶縁膜を介して設けられている第1のゲート電極と、ボディ領域の第2の側面に第2のゲート絶縁膜を介して設けられている第2のゲート電極とを備え、第1および第2の拡散層、ボディ領域、第1および第2のゲート絶縁膜、並びに、第1および第2のゲート電極はメモリセルを構成し、各メモリセルは、第1および第2のゲート絶縁膜の分極状態によって複数の論理データを記憶する。

(もっと読む)

エッジ・ダミーメモリセル・ブロックを除去した半導体メモリ装置

【課題】エッジ・ダミーメモリセル・ブロックを除去したオープン・ビットライン構造の半導体メモリ装置を提供する。

【解決手段】メモリセル配列を含むメモリセル・ブロックと、一つ以上の第1センスアンプを具備し、それぞれの第1センスアンプは、第1ビットライン、第1相補ビットライン及び第1サイズの第1トランジスタを有する第1増幅回路を具備するエッジ・センスアンプ・ブロックと、一つ以上の第2センスアンプを具備し、それぞれの第2センスアンプは、第2ビットライン、第2相補ビットライン、及び前記第1サイズと互いに異なる第2サイズの第2トランジスタを有する第2増幅回路を具備するセントラル・センスアンプ・ブロックと、エッジ・センスアンプ・ブロックと電気的に連結され、少なくとも1つのキャパシタを含むキャパシタ・ブロックと、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】メモリセル領域の配線容量を低減し、かつ、周辺回路領域の配線抵抗を低減した半導体装置とその製造方法の提供。

【解決手段】本発明の半導体装置の製造方法は、メモリセル領域に縦型MOSトランジスタを、周辺回路領域にプレーナ型MOSトランジスタを形成し、前記縦型MOSトランジスタ上に深孔型立体キャパシタ素子10を形成する第1工程と、キャパシタ素子10上にメモリセル領域全体を覆うようにキャパシタ上部電極層31を形成し、前記メモリセル領域の上面の位置を、前記周辺回路領域の上面の位置よりも高く設定する第2工程と、前記周辺回路領域に第2コンタクトプラグ35を形成する第3工程と、前記メモリセル領域のキャパシタ上部電極層31上にセル部上部配線38を形成し、前記周辺回路領域に第2コンタクトプラグ35と接続し、セル部上部配線38よりも鉛直方向の膜厚が厚い周辺部上部配線39を形成する第4工程とを備える。

(もっと読む)

半導体装置及びこれを備えるシステム

【課題】ビット線が階層化された半導体装置においてセンス感度を向上させる。

【解決手段】グローバルビット線GBL1,BGL2の電位差を増幅するセンスアンプSAと、グローバルビット線GBL1,BGL2に接続された複数の階層スイッチSWと、階層スイッチSWを介してグローバルビット線GBL1,GBL2にそれぞれ接続される複数のローカルビット線を含むメモリマットMAT1,MAT2と、階層スイッチSWを活性化させる制御回路と、を備える。制御回路は、グローバルビット線GBL1,GBL2に沿ったセンスアンプSAからの距離が互いに等しい階層スイッチSWを活性化させる。本発明によれば、どのローカルビット線が選択された場合であっても、寄生CR分布定数に差が生じないことから、センス感度の低下を防止することが可能となる。

(もっと読む)

半導体装置及びこれを備えるシステム

【課題】ビット線が階層化された半導体装置において、端部に位置するメモリマットを他のメモリマットと同様に扱えるよう構成する。

【解決手段】グローバルビット線GBL及びそれより短いダミーグローバルビット線DGBLと、これらの電位差を増幅するセンスアンプSAと、階層スイッチSWを介してグローバルビット線GBLに接続されるローカルビット線LBLをそれぞれ含む複数のメモリブロックMBと、ダミー階層スイッチDSWを介してダミーグローバルビット線DGBLに接続されるLBLと同じ長さのダミーローカルビット線DLBLを含むダミーメモリブロックDMBと、階層スイッチSWのいずれか及びダミー階層スイッチDSWを活性化させる制御回路100とを備える。これにより、端部に位置するメモリマットと他のメモリマットとを同じ記憶容量とすることが可能となる。

(もっと読む)

半導体装置

【課題】高速アクセス動作を実現する半導体記憶装置を提供する。

【解決手段】複数の正規メモリセルを含むメモリセルアレイと複数のセンスアンプ回路からなる半導体記憶装置において、メモリセルアレイには、所望のデータの書込み及び読出し動作に利用する正規メモリセルMCと、電源ノイズを低減するための平滑容量(具体的には平滑容量に利用するダミーセルDMC)を有する。また、ダミーセルDMCのワード線は、正規メモリセルMCのワード線と同じタイミングで活性化する。また、データ線のプリチャージレベルはVDDとし、ダミーセルDMCの一部を参照レベル発生用のメモリセルとして利用しても良い。この場合、正規メモリセルMCのワード線の非活性化をダミーセルDMCのワード線の非活性化よりも先行的に実施する。さらに、隣接データ線同士を短絡するための回路を付加しても良い。

(もっと読む)

半導体記憶装置及び半導体記憶装置の製造方法

【課題】メモリセルアレイ領域間のサブワードドライバ形成領域を、各ドライバを構成する各トランジスタが必要とする能力を確保しつつ、小さくする。

【解決手段】サブワード線SWLを駆動するサブワード線ドライバを構成する各トランジスタのドレイン領域16b,16d又はソース領域16a,16c,16eと接続するための複数のコンタクトプラグが、各トランジスタのコンタクトプラグを形成すべき部分に跨って設けられたライン形状の開口部を有するマスクを用いて各トランジスタを覆う絶縁層を選択エッチングするラインSAC技術を用いて形成される。

(もっと読む)

半導体装置

【課題】信号配線領域の大幅な増大をともなうことなく、信号配間に生じるカップリングノイズの低減を実現した半導体装置を提供する。

【解決手段】信号線が並行配置される場合において、当該信号線の全てが片側の信号線だけからのみカップリングノイズを受ける構成とするため、当該複数の信号線の両側において他の信号線と対向しないように、その信号線の片側一方にのみ電源電位、接地電位又は当該信号線がカップリングノイズを受ける期間において一定電位に維持される配線を配置する。

(もっと読む)

半導体集積回路および半導体記憶装置

【課題】チップの内部バスやチップ間を接続する外部バスにおける消費電力の低減や、データ転送速度の向上を実現する。

【解決手段】論理レベル‘H’か‘L’かその中間レベルとなる‘M’を採り得る複数本のバスDB[0]〜DB[n−1]と、データD[0]〜D[m−1]を符号化し、これに基づいて複数本のバスのそれぞれを論理レベル‘H’、‘L’、‘M’のいずれかに駆動する送信回路TXと、複数本のバスを互いにショートするバスイコライズ回路BEQを設ける。送信回路TXは、データの符号化を行う際に、論理レベル‘H’に駆動するバスの本数(k本)と論理レベル‘L’に駆動するバスの本数(k本)が同数となるような組み合わせを用いる。バスイコライズ回路BEQは、データが送信された後にショート動作を行うことで、各バスを論理レベル‘M’にプリチャージする。

(もっと読む)

ダイナミック連想メモリセル

【課題】2値または3値保存性能を有するダイナミック連想メモリを提供する。

【解決手段】ダイナミック連想メモリは、ビット・ラインとワード・ラインの交差部に位置する複数のダイナミック連想メモリセルを備える。各セルは、ワード・ラインに接続されるゲート端子およびビット・ラインに接続される第1ソース/ドレイン端子を有するアクセス・トランジスタと、アクセス・トランジスタの第2ソース/ドレイン端子に接続される第1プレートを有する第1メモリセル・キャパシタと、ポリシリコン相互接続層だけを介してアクセス・トランジスタの第2ソース/ドレイン端子に接続されるゲート端子を有する、マッチ・ラインの整合結果または不整合結果を示すための比較トランジスタとを含む。

(もっと読む)

半導体記憶装置

【課題】微細化しても信号量の差を低下させず、データの誤検出を抑制することができる半導体記憶装置を提供する。

【解決手段】強誘電体メモリは、互いに並列に接続された強誘電体キャパシタおよびセルトランジスタを含むメモリセルが複数個直列に接続されて構成されたセルブロックと、セルトランジスタのゲートに接続されたワード線と、セルブロックの一端に接続されたブロック選択部と、ブロック選択部を介してセルブロックの一端に接続された複数のビット線と、セルブロックの他端に接続されたプレート線とを備え、ワード線を共有する第1および第2のセルブロックの各一端は、互いに異なるブロック選択部を介して、同一のビット線に接続されており、第1および前記第2のセルブロックの各他端は、互いに異なるプレート線に接続されている。

(もっと読む)

1 - 20 / 46

[ Back to top ]