Fターム[5F083NA01]の内容

Fターム[5F083NA01]に分類される特許

3,461 - 3,470 / 3,470

2−トランジスタメモリセル及びその製造方法

本発明は、メモリゲートスタック(1)を有する記憶トランジスタ(1)及び選択トランジスタを有する2-トランジスタメモリセルを基板(50)上に製造する方法であって、トンネル誘電層(51)が前記基板(50)と前記メモリゲートスタック(1)との間にもたらされる方法を提供する。前記方法は、第一の導電層(52)及び第二の導電層(54)をもたらし、前記第二の導電層(54)をエッチし、それによってコントロールゲートを形成し、前記第一の導電層(52)をエッチし、それによってフローティングゲートを形成することによって前記メモリゲートスタック(1)を形成するステップを有する。前記方法は更に、前記第一の導電層(52)がエッチされる前に、前記トンネル誘電層(51)の下に形成されるべきチャネルの方向で前記コントロールゲートに対してスペーサ(81)を形成するステップと、その後、前記第一の導電層(52)をエッチするために前記スペーサ(81)をハードマスクとして使用し、それによって前記フローティングゲートを形成し、それによってフローティングゲートをコントロールゲートに自己整合させるステップとを有することを特徴とする。本発明は、前記コントロールゲート(54)は前記フローティングゲート(52)よりも小さくなり、スペーサ(81)が、前記コントロールゲート(54)に隣接してもたらされるメモリセルも提供する。  (もっと読む)

(もっと読む)

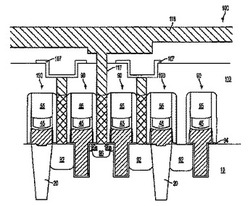

DRAMアクセス・トランジスタ及び形成方法

【構成】自己整列リセス・ゲート構造及び形成方法が開示されている。最初に,絶縁用のフィールド酸化物領域を半導体基板内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。 (もっと読む)

不揮発性半導体記憶装置、その製造方法、電子カード及び電子装置

【課題】 カップリング比のばらつきを小さくできるNAND型EEPROMを提供する。

【解決手段】 メモリセルの電荷蓄積層17の上層導電部23は、互いに間を設けて形成された一対の立上り部27により構成される内側面29及び外側面31を有する。内側面29側には底面高さ調節層43があり、外側面31側には素子分離絶縁層5がある。このため、半導体基板9の位置(A)のメモリセルと位置(B)のメモリセルとで、立上り部27の高さが異なっていても、電荷蓄積層17と制御ゲートCGとが対向する領域の面積を同じにできる。

(もっと読む)

電気試験データに基づいてゲート絶縁層の特性および特徴を制御するための方法、これを実施するためのシステム

本発明は、一般に、電気試験データ(46)に基づいてゲート絶縁層(16)の特性および特徴を制御する各種方法、ならびにこれを実施するためのシステムを対象としている。例示的な一実施形態では、上記方法は、少なくとも1つの半導体デバイスに少なくとも1つの電気試験を実施するステップと、以降形成する半導体デバイスに少なくとも1つのゲート絶縁層(16)を形成するために実施する少なくとも1つのプロセス操作の少なくとも1つのパラメータを、電気試験から得られた電気データに基づいて決定するステップと、決定されたパラメータを含む少なくとも1つのプロセス操作を実施して、ゲート絶縁層(16)を形成するステップとを有する。  (もっと読む)

(もっと読む)

ビア開口部中に形成されるポリマーメモリデバイス

本発明は、ビア内にポリマーメモリデバイスを製造する方法に関する。この方法は、少なくとも1つの金属を含む層をその上に備える半導体基板を提供するステップと、この金属を含む層中に少なくとも1つの銅コンタクトを形成するステップと、銅コンタクト上に少なくとも1つの絶縁層を形成するステップと、絶縁層に少なくとも1つのビアを形成し、銅コンタクトの少なくとも一部を露出するステップと、ビアの下側部分にポリマー材料を形成するステップと、ビアの上側部分にトップ電極材料層を形成するステップとを含む。  (もっと読む)

(もっと読む)

垂直方向の突起部を有するフローティングゲート構造

基板面から離れて延在する突起部を有するフローティングゲート構造を開示する。この突起部によって、フローティングゲートとコントロールゲートとを結合するための増加した表面積をフローティングゲートに提供することが可能となる。1つの実施形態では、フローティングゲートの個々の側面でワードラインが下方へ延在して、同じ列の隣接するフローティングゲートを遮蔽する。別の実施形態では、突起部を有するフローティングゲートの組立て製造処理工程を開示する。残りのフローティングゲートに対して自己位置合せを行うために突起部を形成してもよい。  (もっと読む)

(もっと読む)

昇圧電位発生回路及び制御方法

【課題】 半導体メモリにおいて、外部電源電圧が低下しても、半導体メモリ内部では、高速動作を可能にすると共に、小型化をも可能にする昇圧電位発生回路を提供する。

【解決手段】 容量MOSトランジスタとトランスファMOSトランジスタとを備え、メモリセルを含むDRAMに使用される昇圧電位発生回路において、容量MOSトランジスタのゲート絶縁膜を、メモリセルを構成するMOSトランジスタのゲート絶縁膜の膜厚よりも薄い膜厚にすることにより、小面積で大容量の昇圧電位発生回路を実現する。この場合、トランスファMOSトランジスタのゲート絶縁膜の厚さを容量MOSトランジスタのゲート絶縁膜の厚さを同等以上に厚くすることが好ましい。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線とセルコンタクト部の容量接続用コンタクトとのショートを防止し、容量接続用コンタクトとビット線とのマージンを大きくすることができる半導体記憶装置及びその製造方法の提供。

【解決手段】STIにより活性領域が分離形成された半導体基板上の第1の層間絶縁膜4に活性領域まで貫通するコンタクト孔5を設け、その内部に第1の層間絶縁膜上面よりも低い位置まで多結晶シリコン6を充填した後、多結晶シリコン上部にシリサイド膜12を形成し、第1の層間絶縁膜上の所定領域にポリサイド膜又はメタル膜を含むビット線7とビット線の上面及び側面にシリコン窒化膜を形成した後、ビット線で覆われていないコンタクト孔内部のシリサイド膜を除去することにより、シリンダ型容量と接続されるコンタクト孔内部の導電体とそのコンタクト孔に隣接するビット線とを分離する。その後、第2の層間絶縁膜10を堆積し、シリサイド膜を除去したコンタクト孔まで貫通するシリンダ型容量パターンを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 実効的な素子特性を向上させ、または素子領域の基板表面が露出することを防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板101の表面上にシリコン酸化膜102を形成し、この表面上に埋め込み酸化膜の平坦化ストッパー材となるシリコン窒化膜103を形成する。半導体基板101にトレンチ105を形成した後、シリコン酸化膜102の側面にエッチングを行って後退させる。半導体基板101の露出している表面に酸化を行って素子領域の表面に丸みを付ける。これにより、素子領域の実効寸法を実寸法よりも大きくすることができる。

(もっと読む)

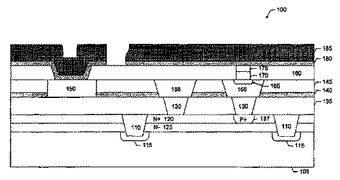

半導体装置および半導体記憶装置

【課題】本発明は、素子間分離にSTI構造を採用する不揮発性半導体記憶装置において、ソース領域をより確実に接続できるようにすることを最も主要な特徴とする。

【解決手段】たとえば、P型シリコン基板11の表面部に、浅い第一の埋め込み素子分離絶縁膜22と、この第一の埋め込み素子分離絶縁膜22よりも深い、第二の埋め込み素子分離絶縁膜23とからなる素子分離領域24を形成する。そして、第一の埋め込み素子分離絶縁膜22を除去した後に、その底部とメモリセルトランジスタのソース領域とに不純物をイオン注入する。こうして、第一の埋め込み素子分離絶縁膜22のアスペクト比を下げ、トレンチ溝の側壁部分に対しても十分に拡散層を形成できるようにすることで、ソース線SLとなる、連続したN+ 型ソース領域19の形成を可能とする構成となっている。

(もっと読む)

3,461 - 3,470 / 3,470

[ Back to top ]