Fターム[5F083PR22]の内容

Fターム[5F083PR22]に分類される特許

941 - 950 / 950

不揮発性プログラマブルメモリ

【課題】

【解決手段】 メモリ(3700)が提供される。メモリは、不揮発性メモリセルアレイ(3720)を含み、各セルは、第1の書き込み電圧パルスを印加されると第1の抵抗状態から第2の抵抗状態へと切り替わるとともに第2の書き込み電圧パルスを印加されると第2の抵抗状態から第1の抵抗状態へと可逆的に切り替わる2端子メモリプラグを含む。

(もっと読む)

ポリマーメモリ装置の金属窒化物電極及び金属酸化物電極内への電子トラップ生成

本発明の一実施形態は、ポリマー強誘電体メモリ装置のポリマー強誘電体層に引き起こされるダメージを、金属電極とポリマー強誘電体層との間の絶縁性の金属窒化物及び/又は金属酸化物層に過剰正孔を生成することによって低減する。交流バイアスの下で金属電極から注入される電子はポリマー強誘電体層にダメージを与えるものであるが、金属窒化物及び/又は金属酸化物における過剰正孔がこのような電子をトラップする。 (もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

スイッチング素子

転移確率を高くしてスイッチング特性を安定化した、双安定特性を持つスイッチング素子を提供する。

少なくとも2つの電極間に、印加される電圧に対して2種類の安定な抵抗値を持つ有機双安定化合物を含む有機双安定材料層30を配置してなるスイッチング素子であって、基板10上に、第1電極層20a、電荷注入抑制層40、有機双安定材料層30、第2電極層20bの順に薄膜として形成され、電荷注入抑制層40が、第1電極層20aから有機双安定材料層30への電荷注入量を、電荷注入抑制層40を設けずに第1電極層20aから有機双安定材料層30へ直接電荷注入する場合に比べて小さくする導電層からなる。

(もっと読む)

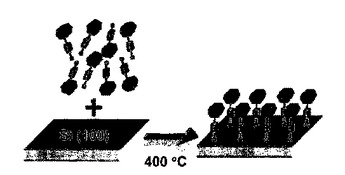

基板への有機分子の高温付着

本発明は、半導体表面、特にシリコンに分子を付着させるための新規手順を提供するものである。ポルフィリンおよびフェロセンを含む(しかし、これらに限定されない)分子が分子ベースの情報記憶のための魅力的な候補であることは、以前に示されてきた。この新規付着手順は、単純であり、短時間に完了させることができ、最少量の材料しか必要とせず、様々な分子官能基と両立でき、場合によっては従来にない付着モチーフを生じる。これらの特徴は、ハイブリッド分子/半導体情報記憶デバイスを作るために必要な加工段階への分子材料の組込みを非常に向上させる。  (もっと読む)

(もっと読む)

素子間分離のための半導体構造中の素子間のボイドの使用

記憶素子間の静電結合レベルを低減するために、隣接する電荷記憶素子を有するフラッシュEEPROMまたは他のタイプのメモリセルアレイを素子間にガスが充填されているボイドとともに形成し、これにより電荷記憶素子間の漏れ結合およびアレイから読み出されるデータ中に結果として生じるエラーを低減する。  (もっと読む)

(もっと読む)

磁気抵抗効果型素子ならびにこれを用いた磁気記憶素子および磁気ヘッド

【課題】 ペロブスカイト型酸化物を用いて良好なトンネル接合を実現し、低磁場でも大きな磁気抵抗効果を発現する磁気抵抗効果型素子を提供する。

【解決手段】 式L2(A1-zRz)2An-1MnO3n+3+xにより表される組成を有し、結晶構造内に(L-O)2層を有する層状ペロブスカイト型酸化物と、この酸化物を挟むようにこれに接して形成された一対の強磁性体と、を含む磁気抵抗効果型素子とする。ただし、AはCa、SrおよびBaから選ばれる少なくとも1種の元素を、LはBi、TlおよびPbから選ばれる少なくとも1種の元素を、MはTi、V、Cu、Ru、Ni、Mn、Co、FeおよびCrから選ばれる少なくとも1種の元素を、Rは希土類元素をそれぞれ示し、nは1、2または3であり、x、zは、それぞれ、−1≦x≦1、0≦z<1により示される範囲内の数値である。

(もっと読む)

強誘電体膜を有する半導体装置の製造方法

【課題】強誘電体膜をエッチングする際に生じる反応副生成物を形成される素子に悪影響を与えることなく除去する。

【解決手段】強誘電体膜をエッチングしたあと、燐酸水溶液を用いてウェット処理をする。レジストをマスクとして強誘電体膜をエッチングしたあと、レジストアッシング後またはアッシング前後の両方に燐酸水溶液を用いてウェット処理をする。

(もっと読む)

半導体装置およびその製造方法

【課題】 強誘電体キャパシタに保護膜を設け、強誘電体膜の還元を抑制する。

【解決手段】 前記保護膜としてAl2 O3 膜を、3.0〜3.1g/cm3 、あるいはそれ以上の密度に形成する。

(もっと読む)

半導体装置の製造方法、強誘電体キャパシタ、およびその製造方法

【課題】 強誘電体キャパシタを有する半導体装置の製造において、強誘電体膜の自発分極を最大化する。

【解決手段】 下側電極を形成後、強誘電体膜を堆積する前に、前記下側電極を不活性雰囲気中において急速熱処理する。

(もっと読む)

941 - 950 / 950

[ Back to top ]