Fターム[5F083ZA14]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ部+メモリ部(異種) (302)

Fターム[5F083ZA14]に分類される特許

301 - 302 / 302

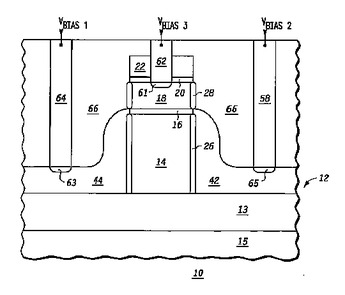

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

301 - 302 / 302

[ Back to top ]