Fターム[5F083ZA14]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ部+メモリ部(異種) (302)

Fターム[5F083ZA14]に分類される特許

161 - 180 / 302

不揮発性メモリ及びマイクロコンピュータ

【課題】不揮発性メモリの消去動作における基板電流の最大値を低減すること。

【解決手段】本発明の不揮発性メモリ(2)は、半導体基板(30)に形成されたソース電極(53)及びドレイン電極(54)と、ソース電極とドレイン電極間の前記半導体基板上に形成された電荷トラップ層(52)と、電荷トラップ層上に配置されたゲート電極(50)とを有する不揮発性メモリセルがアレイ状に複数配列されて成る。不揮発性メモリは、ソース電極とゲート電極とに消去に必要な電圧を印加する消去モードを有する制御回路(33)を備える。前記消去モードにおいて、ゲート電極に電圧の印加を開始してから前記ゲート電極の電圧が消去に必要な所定電圧に達するまでの期間(63)が、ソース電極に電圧の印加を開始してから前記ソース電極の電圧が前記所定電圧に達するまでの期間(64)よりも長くされる。これによって、消去動作における基板電流の最大値が抑えられる。

(もっと読む)

メモリ及び半導体装置

【課題】書き込んだデータの改ざんを防止したメモリ及び半導体装置を提供する。

【解決手段】「第1の状態」、「第2の状態」、又は「第3の状態」から選ばれた一の状態を有するアンチフューズを備えるメモリである。アンチフューズは、「第1の状態」である場合は、書き込みを行うことにより「第2の状態」又は「第3の状態」に変化する。「第2の状態」であるアンチフューズ、又は「第3の状態」であるアンチフューズは、書き込みを行うかによらず状態が変化しない特性を有する。そして、アンチフューズの「第2の状態」及び「第3の状態」を、2値データの”0”及び”1”、又は”1”及び”0”に対応させる。

(もっと読む)

不揮発性半導体記憶素子、及び不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置が備える不揮発性半導体記憶素子を標準的なCMOSプロセスで製造するトランジスタを用いて構成する。

【解決手段】標準的なCMOSプロセスによるトランジスタ二個を一組とし備える記憶部200は、ソース・半導体基板間に発生するバンド間トンネル電流が流れる際に発生する正孔と電子を、半導体基板とゲート酸化膜の境界付近にある結晶欠陥にトラップさせる。結晶欠陥に正孔又は電子をトラップしたトランジスタは閾値が変化するので、記憶部200が備えるNMOSトランジスタ201とNMOSトランジスタ202の閾値の変化によるドレイン電流の差をSRAM部100が備えるセンスアンプ回路で検出することにより記憶されたデータの読み出しを行う。

(もっと読む)

半導体集積回路

【課題】降圧回路の出力電位に対するトリミング効率を向上させる。

【解決手段】第1及び第2外部電圧を受け内部電圧(VDL)を発生する降圧回路と、降圧回路に結合され、上記内部電圧の電圧レベルを調整する為の情報を格納する揮発性格納回路(31DR)と、上記内部電圧と上記第2外部電圧とを受け、内部電圧と上記第2外部電圧との間で動作される中央処理装置(10)と、上記中央処理装置によってアクセス可能な不揮発性記憶素子とを有する。上記不揮発性記憶素子に格納された上記情報は半導体集積回路の初期化に応答して読み出され、上記揮発性格納回路は上記不揮発性記憶素子から読み出された上記情報を上記半導体集積回路の初期化に応答して格納することにより、上記情報によって調整された内部電圧が上記降圧回路から上記中央処理装置へ供給される。

(もっと読む)

半導体装置

【課題】配線層にスイッチ素子を有するプログラム可能な半導体装置の提供。

【解決手段】第1の配線層101の配線と第2の配線層102の配線を接続するビア103の内部、ビアの第1の配線との接触部、第2の配線との接触部のうちの少なくとも1つに、電解質材料104等導電率が可変の部材が配設され、ビア103は、第1の配線との接触部を第1の端子、第2の配線との接触部を第2の端子とする導電率が可変型のスイッチ素子又は可変抵抗素子として用いられ、スイッチ素子の導電率を変えることで、第1の

端子と第2の端子との接触部との接続状態を、短絡、開放、又はその中間状態に可変に設定自在とされる。金属イオンの酸化還元反応によって、第1の電極と第2の電極間の導電率が変化する2端子スイッチ素子を備え、第1の電極に接続された逆極性の第1、第2のトランジスタと、第2の電極に接続された逆極性の第3、第4のトランジスタを備えている。

(もっと読む)

可変結合を有する不揮発性プログラマブルメモリに組み込まれた集積回路

マルチプログラマブル不揮発性デバイスは、ソース/ドレイン領域の一部分に重なるFETゲートとして機能する浮遊ゲートで動作し、ジオメトリ及び/又はバイアス条件によって可変結合を可能にする。これにより、デバイス用のプログラム供給電圧が可変容量結合によって浮遊ゲートに付与され、デバイスの状態を変更する。本発明は、データ暗号化、リファレンス調整、製造ID、セキュリティID及び他の多くのアプリケーションなどの各環境において使用できる。  (もっと読む)

(もっと読む)

半導体装置

【課題】SoCにDRAMを混載する場合に、プロセス、特性に影響することなく十分な容量のキャパシタを形成することが可能な半導体装置を提供する。

【解決手段】半導体基板11に形成され、素子分離されたトランジスタ領域と、半導体基板11上に形成された第1の層間膜19と、第1の層間膜19に形成され、それぞれトランジスタ領域に接続される第1および第2のコンタクトプラグ20、21と、第1のコンタクトプラグ20中に形成され、電極層22a/絶縁層22b/Cu層22cより構成されるMIM構造を有する第1のキャパシタと、第2のコンタクトプラグ21と接続されるビット線29を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】容量素子を含む半導体装置において、容量素子の信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板10に形成された素子分離領域11上に容量素子を形成する。この容量素子は、下部電極16と、下部電極16上に容量絶縁膜27を介して形成された上部電極23とを有している。基本的に、下部電極16と上部電極23は、ポリシリコン膜14、20とこのポリシリコン膜14、20の表面に形成されたコバルトシリサイド膜33から形成する。ここで、上部電極23に形成されるコバルトシリサイド膜33の端部を上部電極23の端部から距離L1だけ離間するように構成する。その上、下部電極16に形成されるコバルトシリサイド膜33の端部を、上部電極23と下部電極16の境界から距離L2だけ離間するように構成する。

(もっと読む)

情報処理システム

【課題】記憶装置の高速性及び高信頼性を確保しつつ大容量化を図る。

【解決手段】データを記憶するメインメモリと、このメインメモリに対してデータをアクセスする制御回路とを有する。メインメモリは、可変抵抗素子を使用した電気的に書き換え可能な不揮発性のメモリセルを有する不揮発性半導体記憶装置と、制御回路と不揮発性半導体記憶装置との間にキャッシュメモリとして配置されるDRAMとを備える。不揮発性半導体記憶装置は、記憶されたデータを再書き込みするリフレッシュモードを有し、制御回路は、不揮発性半導体記憶装置に対するアクセス回数に基づいて不揮発性半導体記憶装置のリフレッシュモードを起動する。

(もっと読む)

マスクROM

【課題】容易に多値マスクROMを実現すること。

【解決手段】本発明に係るマスクROM(100)は、複数のメモリセル(MC)を備える。複数のメモリセル(MC)の各々は、第1端子(T1)と、第2端子(T2)と、第1端子(T1)及び第2端子(T2)のそれぞれにソース及びドレインが接続されたトランジスタ(TR)とを含む。複数のメモリセル(MC)のうち第1メモリセル(MC2)は、更に、第1端子(T1)と第2端子(T2)との間を電気的に接続する第1抵抗配線(21)を含む。第1抵抗配線(21)の抵抗値は、第1メモリセル(MC2)のデータに依存する。

(もっと読む)

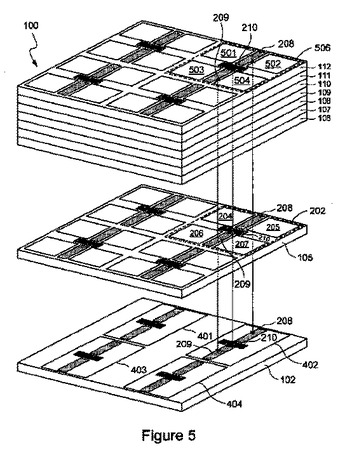

3次元メモリモジュールアーキテクチャ

本発明の様々な実施形態は、スタックされたメモリモジュールに向けられている。本発明の一実施形態において、メモリモジュール(100,600,1200,1400)は、少なくとも1つのメモリ層がスタックされた少なくとも1つのメモリコントローラ層(102,602,1204,1402)を備える。ファインピッチのスルー複数バイア(例えば、スルーシリコン複数バイア)(114,116)が、前記少なくとも1つのメモリコントローラ(401〜404)と、前記少なくとも1つのメモリ層との間の電気的な伝達を提供する前記スタックを通じて、前記少なくとも1つのメモリコントローラの表面に対してほぼ垂直に延在する。追加的には、前記メモリコントローラ層は、前記メモリモジュールに対して双方向にデータを伝達するよう構成された少なくとも1つの外部インターフェースを含む。更にまた、前記メモリモジュールには、光学層(602,1202)を含めることができる。該光学層を、前記スタック内に含めることができ、及び、該光学層は、前記少なくとも1つのメモリコントローラに対して双方向にデータを伝達するバス導波路を有する。前記外部インターフェースは、前記光学層とインターフェースする光学的な外部インターフェースとすることができる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】設計、製造および検査の各工程において作業効率を向上し得る不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性メモリでは、第1配線層LY2に形成されるビット線BL1によりコンタクトホールCH1,CH3,CH5を介してセルトランジスタ21〜25の各ドレインD21〜D25を共通に接続し、このビット線BL1にバイアホールVH1,VH3,VH5を介して接続可能に配置したビット線BL2を第2配線層LY4に形成する。また、第1配線層LY2に形成されるソース線SL1によりコンタクトホールCH2,CH4,CH6を介してセルトランジスタ21〜25の各ソースS21〜S25を共通に接続し、このソース線SL1にバイアホールVH2,VH4,VH6を介して接続可能に配置したソース線SL2を第2配線層LY4に形成する。

(もっと読む)

半導体装置、半導体装置の製造方法並びにデータ処理システム

【課題】特別なプロセス、構造、工程を必要とせずに各種使用電圧に対応することのできる縦型SGT構造を備えた半導体装置とその製造方法を提供する。

【解決手段】本発明の半導体装置は、同一基板上に高耐圧トランジスタと低耐圧トランジスタとを混載してなる半導体装置であって、低耐圧トランジスタは、基板1上に立設された半導体の基柱5と、基柱5の外周面に設けられたゲート電極11と、基柱5の上下に設けられたソース拡散層16及びドレイン拡散層9と、を備えた単一の単位トランジスタ50によって形成され、高耐圧トランジスタは、低耐圧トランジスタを構成する単位トランジスタ50の基柱5の高さと同じ高さの半導体の基柱5を有する複数の単位トランジスタ50のソース拡散層16とドレイン拡散層9を直列に接続し、且つ複数の単位トランジスタ50のゲート電極11同士を電気的に接続することによって形成されている。

(もっと読む)

抵抗変化素子とその製造方法ならびに抵抗変化型メモリ

【課題】抵抗変化部の形成プロセスの負荷が低減されながら、素子のさらなる微細化および高集積化に対応できる新たな構造を有する抵抗変化素子を提供する。

【解決手段】基板10と、基板10上に配置された第1の電極11および第2の電極13と、第1および第2の電極の間に配置された抵抗変化部12とを含み、第1および第2の電極の間の電気抵抗値が異なる2以上の状態が存在し、第1および第2の電極を介して抵抗変化部12に駆動電圧または電流を印加することにより、上記2以上の状態から選ばれる1つの状態から他の状態へと変化する抵抗変化素子1であって、第1の電極11と絶縁膜14との積層構造を有する積層体15が基板10上に配置され、抵抗変化部12は、その側面が第1の電極11および絶縁膜14の双方の側面に接するように積層体15と接しており、抵抗変化部12と第2の電極13とが、各々の側面において互いに接している素子とする。

(もっと読む)

エミュレートされるコンビネーションメモリデバイス

【課題】集積回路メモリデバイス、および、単一の集積回路メモリデバイス内における複数のメモリタイプへのアクセスを提供する。

【解決手段】メモリデバイスは、エミュレートされる第1のメモリ領域およびエミュレートされる第2のメモリ領域を有する不揮発性メモリアレイと、インターフェースを有するコントローラとを備えている。メモリデバイスは、エミュレートされる第1のメモリタイプ、およびエミュレートされる第2のメモリタイプをエミュレートするように構成されている。メモリデバイスはさらに、メモリデバイスがエミュレートされる第1のメモリタイプをエミュレートする時にエミュレートされる第1のメモリ領域内にデータを記憶するように構成されており、また、メモリデバイスがエミュレートされる第2のメモリタイプをエミュレートする時にエミュレートされる第2のメモリ領域内にデータを記憶するように構成されている。

(もっと読む)

記憶装置、半導体装置、及び電子機器

【課題】記憶素子の記憶特性が経時劣化した場合においても、正確なデータの維持が可能な記憶装置を提供する。

【解決手段】抵抗値が変化する記憶素子108を有し、記憶素子108の抵抗値の状態を利用してデータ保持を行うメモリセル100と、メモリセル100に保持されたデータを読み出す読み出し回路103と、電源線104と、第1の信号線105と、第2の信号線102と、記憶素子108の抵抗値の状態に従って電源線104の電位またはメモリセル100に保持されたデータに対応する電位を出力する出力端子106と、を有し、読み出し回路103は、第1端子乃至第4端子を有するトランジスタ109を有し、トランジスタ109のしきい値電圧は、第4端子を介してチャネル領域に電位が与えられることにより制御が可能である。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】メモリセルの電気特性が良好で、高集積化に適した不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】まずメモリゲート電極MGの一方の側壁側に犠牲層ILのパターンが位置する配置状態が形成される。その配置状態から、メモリゲート電極MGの他方の側壁による段差部を覆うようにコントロールゲート用導電層CGが形成される。コントロールゲート用導電層CGに異方性エッチングを施してメモリゲート電極MGの他方の側壁に沿ってコントロールゲート用導電層CGを残存させることにより、コントロールゲート用導電層CGからコントロールゲート電極CGが形成される。

(もっと読む)

不揮発性半導体メモリ・デバイスにおける欠陥を修復するための方法および装置

欠陥をなくすように不揮発性半導体メモリ・デバイスを修復する方法が、半導体パッケージ内に含まれる不揮発性半導体メモリ・デバイスに関するメモリ耐久性インジケータを監視するステップを含む。前記メモリ耐久性インジケータが規定の限度を超えているかどうか判断される。最後に、メモリ耐久性インジケータが規定の限度を超えているという判断に応答して、デバイスがアニール処理される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリ回路のデータ保持特性を向上させる。

【解決手段】半導体基板1Sの主面のメモリセルアレイMRには情報電荷蓄積用の浮遊ゲート電極FGが配置されている。浮遊ゲート電極FGは、キャップ絶縁膜3aと、その上に形成された絶縁膜4aのパターンにより覆われている。さらに、半導体基板1Sの主面上全面には、絶縁膜4aのパターンおよびゲート電極Gを覆うように絶縁膜2aが堆積されている。絶縁膜2aは、プラズマCVD法により成膜された窒化シリコン膜により形成されている。上記絶縁膜4aは、低圧CVD法により成膜された窒化シリコン膜により形成されている。このような絶縁膜4aを設けたことにより、水や水素イオン等が浮遊ゲート電極FGに拡散するのを抑制または防止できるので、フラッシュメモリのデータ保持特性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】フィン型FETのみを製造する工程に比べて大幅に工程数を増やすことなく、フィン型FETと絶縁破壊の容易な経路を持つ電気ヒューズあるいは不揮発性メモリとをバルクシリコン基板上に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板をエッチングしてフィン部を形成する。フィン部の側面を絶縁膜で覆う。不揮発性メモリ領域側において、絶縁膜をエッチングしてフィン部側面を一部露出させる。露出させたフィン部側面に酸化膜71を形成し除去する。不揮発性メモリ領域とDRAM領域とにおいて、フィン部側面を覆う絶縁膜をエッチングしてフィン部の側面をさらに露出させる。フィン部の露出部分にゲート絶縁膜を形成する。

(もっと読む)

161 - 180 / 302

[ Back to top ]