Fターム[5F083ZA14]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ部+メモリ部(異種) (302)

Fターム[5F083ZA14]に分類される特許

141 - 160 / 302

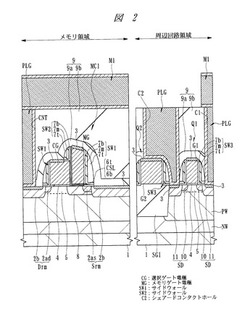

半導体装置およびその製造方法

【課題】スプリットゲート構造のMONOS型不揮発性メモリセルを有する半導体装置において、信頼度を低減することなく高集積化を実現する。

【解決手段】メモリ用nMISのメモリゲート電極MGの高さを選択用nMISの選択ゲート電極CGの高さよりも20〜100nm高く形成することにより、メモリゲート電極MGの片側面(ソース領域Srm側の側面)に形成されるサイドウォールSW1の幅を、所望するメモリセルMC1のディスターブ特性を得るために必要とする大きさとする。また、周辺用第2nMIS(Q2)のゲート電極G2の高さを選択用nMISの選択ゲート電極CGの高さ以下とすることにより、ゲート電極G2の側面に形成されるサイドウォールSW3の幅を小さくして、シェアードコンタクトホールC2の内部がサイドウォールSW3により埋め込まれるのを防ぐ。

(もっと読む)

半導体記憶装置及び情報処理システム

【課題】DRAMメモリセルアレイを自在に不揮発性メモリセルアレイに変更可能な半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置のメモリセルアレイには、誘電体材料を2つの電極で挟んだ構造をそれぞれ有する複数の第1メモリセルMCがアレイ状に配置され、指定可能な複数の領域に区分されている。メモリセルアレイの中から選択的に指定された領域において第1メモリセルMCに対するフォーミングが実行され、不揮発性の第2メモリセルMCaに変更される。これにより、DRAMメモリセルアレイと不揮発性のRRAMメモリセルアレイを混載し、製造後に任意に領域を設定可能な半導体記憶装置を実現することができる。

(もっと読む)

半導体記憶装置の製造方法および半導体記憶装置

【課題】ROMを形成する強誘電体メモリのダイナミック/スタティック・インプリント現象に対するデータ読み出しマージンを改善することのできる半導体記憶装置の製造方法および半導体記憶装置を提供する。

【解決手段】ROMを形成する強誘電体メモリに対し、ROMデータと逆極性のデータを書き込みを行って(工程S01)、所定時間のベーク処理を実行し(工程S02)、その後、ROMデータを書き込む(工程S03)。

(もっと読む)

半導体装置およびその製造方法

【課題】スクリーニングを実施しなくてもMOS容量の不良率を低減できる技術を提供することにある。

【解決手段】高電位と低電位の間にMOS容量MOS1とMOS容量MOS2とを直列に接続して直列容量素子を形成する。そして、この直列容量素子と並列にポリシリコン容量PIP1とポリシリコン容量PIP2を接続する。具体的に、MOS容量MOS1の下部電極を構成する高濃度半導体領域HS1とMOS容量MOS2の下部電極を構成する高濃度半導体領域HS2とを接続する。さらに、MOS容量MOS1の上部電極を構成する電極E1を低電位(例えば、GND)に接続し、MOS容量MOS2の上部電極を構成する電極E3を高電位(例えば、電源電位)に接続する。

(もっと読む)

半導体装置

【課題】内部電源回路においてレーザアタックの有無を精度良く判定するための技術を提供する。

【解決手段】半導体装置は不揮発性メモリを含み、上記不揮発性メモリは内部電源回路を含む。上記内部電源回路は、電圧生成回路と、その出力電圧を分圧する分圧回路(100)とを含む。さらに、上記内部電源回路は、上記分圧回路の第1タップからの出力電圧と基準電圧とを比較する第1コンパレータ(105)と、上記分圧回路の第2タップからの出力電圧と上記基準電圧とを比較する第2コンパレータ(104)と、上記第2コンパレータの出力に基づいてレーザアタックの有無を判定する判定回路(106)とを含む。上記判定回路は、上記電圧検知信号に基づいて、上記レーザアタックの有無の判定開始タイミングを決定することによりレーザアタックの有無を精度良く判定可能にする。

(もっと読む)

不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置

【課題】低電圧かつ高速動作が可能で、しかも可逆的に安定した書き換え特性を有する不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置の提供。

【解決手段】第1電極103と、第2電極108との間に介在され、両電極103,108間に与えられる極性の異なる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層107とを備え、この抵抗変化層107は、ZrOx(但し、0.9≦x≦1.4)で表される組成を有する第1のジルコニウム酸化物層と、ZrOy(但し、1.9<y<2.0)で表される組成を有する第2のジルコニウム酸化物層とが積層された積層構造を少なくとも有している。

(もっと読む)

混載メモリ装置及び半導体装置

【課題】メモリセル領域の面積を削減できる混載メモリ装置を提供する。

【解決手段】本発明に係る混載メモリ装置は、SRAMと、ROMとを備える混載メモリ装置100であって、行列状に配置された複数の第1のメモリセル110及び複数の第2のメモリセル111とを備え、複数の第1のメモリセル110はそれぞれ、SRAMセル120とROMセル130とを含み、複数の第2のメモリセル111はそれぞれ、SRAMセル120を含み、かつROMセル130を含まず、複数の第1のメモリセル110はそれぞれ、少なくとも一つの第2のメモリセル111と隣接して配置される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】不揮発性メモリを有する半導体装置の特性を向上させる。

【解決手段】シリコン基板1上のメモリ領域Rmに不揮発性メモリを形成する工程であって、シリコン基板1の主面に選択ゲート電極CGを形成し、いずれか一方の側壁面に隣り合うダミーゲートDGを形成する。その後、ダミーゲートDGをイオン注入マスクとしたイオン注入D01によって、メモリソース・ドレイン領域SDmを形成する。その後ダミーゲートDGを除去し、ダミーゲートDGが配置されていた箇所に、電荷蓄積膜とメモリゲート電極とを順に形成することで、メモリゲート電極の側方下部にメモリソース・ドレイン領域SDmが配置された構造を形成する。本工程では、メモリソース・ドレイン領域SDmを形成するためのイオン注入D01を施した後に、電荷蓄積膜とメモリゲート電極とを形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】書換え速度の低下を招くことなく、書換えストレス印加前だけでなく書換えストレス印加後のリテンション寿命を長くできる不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板SUBとゲート電極層GEとの間のゲート絶縁膜GIは、第1のシリコン酸化膜OX1と、第1のシリコン窒化膜NI1と、第2のシリコン酸化膜OX2と、第2のシリコン窒化膜NI2と、第3のシリコン酸化膜OX3とからなっている。第2のシリコン酸化膜OX2は1nm以下の厚みを有している。第2のシリコン窒化膜NI2は第1のシリコン窒化膜NI1よりも厚い厚みを有している。

(もっと読む)

半導体記憶装置、及び半導体装置

【課題】トランジスタを絶縁破壊させることなく、記憶素子において確実にデータの書き込みを行うことを課題とする。

【解決手段】半導体記憶装置は、電位制御回路100と、ゲート端子、ソース端子、及びドレイン端子を有するトランジスタ101と、電位供給端子102と、第1端子及び第2端子を有する記憶素子103と、を有する。データ書き込み時において、記憶素子103の第2端子には負電位が与えられる。また、トランジスタ101のゲート端子とソース端子の電位差が、トランジスタ101の閾値電圧以上であり、且つトランジスタ101の絶縁耐圧以下である。また、記憶素子103の第1端子と第2端子の電位差が、トランジスタ101の絶縁耐圧より高く、且つ記憶素子103の書き込みに必要な電圧以上である。

(もっと読む)

半導体記憶装置

【課題】不揮発性メモリの高速化を小面積で実現する。

【解決手段】例えば、SRAMに代表される低集積で高速なメモリアレイ53を半導体基板上に形成し、その上層にフラッシュメモリに代表される高集積で低速なメモリアレイ54を形成する。メモリアレイ54は、各メモリセルのチャネルが縦方向に形成され、小面積での大容量化が図られている。メモリアレイ53とメモリアレイ54は、データ線等が適宜共通化されており、外部からメモリアレイ54に書き込みを行う際には、メモリアレイ53に書き込みを行い、メモリアレイ53からメモリアレイ54に転送を行う。

(もっと読む)

半導体集積回路装置およびその設計方法、半導体集積回路装置の製造方法

【課題】基板上に形成される、ワード線長およびビット線長が異なるSRAMの動作速度を、簡単な構成により最適化する半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、基板上の第1の領域に形成された第1のSRAM20Aと、基板上の第2の領域に形成された第2のSRAM20Bと、を備え、第1のSRAM20Aでは、ワード線WLの方がビット線BLよりも長く、第2のSRAM20Bでは、ビット線BLの方がワード線WLよりも長く、第1のSRAM20Aでは、ワード線WLが、ビット線BLを構成する配線層よりも下の配線層に形成され、第2のSRAM20Bでは、ビット線BLが、ワード線WLを構成する配線層よりも下の配線層に形成される。

(もっと読む)

マイクロコンピュータ及びデータプロセッサ

【課題】不揮発性メモリセルから記憶情報を高速に読み出すことができる半導体装置を提供する。

【解決手段】マイクロコンピュータは、内部バス68と、前記内部バスに結合されている中央演算部61と、前記内部バスに結合された不揮発性メモリ63とを含む。前記不揮発性メモリは、第1ゲートと第2ゲートとを含む複数の不揮発メモリセルと、前記複数の不揮発メモリセルの一つの前記第1ゲートに結合された第1回路21と、前記複数の不揮発メモリセルの一つの前記第2ゲートに結合された第2回路22と、前記第1回路に供給する第1電圧と前記第2回路に供給する第2電圧とを生成する電圧生成回路VS,77と、を含む。前記第1回路のゲート耐圧は前記第2回路のゲート耐圧より低い。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の性能を向上させる。

【解決手段】同一のシリコン基板1上に、制御ゲート電極CGsおよび側壁メモリゲート電極MGsを有するスプリットゲート型メモリセルM1Aと、シングルメモリゲート電極MGuを有するシングルゲート型メモリセルM2とを備える不揮発性半導体記憶装置において、第1領域R1に制御ゲート絶縁膜ICsを介して制御ゲート電極CGsを形成し、第1領域R1には電荷蓄積膜IMsを介して側壁メモリゲート電極MGsを形成し、同時に、第2領域R2には電荷蓄積膜IMuを介してシングルメモリゲート電極MGuを形成する。その際、側壁メモリゲート電極MGsとシングルメモリゲート電極MGuとは同一の工程で形成し、制御ゲート電極CGsと側壁メモリゲート電極MGsとは、互いに電気的に絶縁された状態で、互いに隣り合って配置されるようにして形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】リテンション耐性の良好な不揮発性半導体記憶装置を提供する。

【解決手段】1つのメモリセルMCが導電性電荷蓄積層と絶縁性電荷蓄積層ECSとを有している。導電性電荷蓄積層はフローティング電位を有する第1のゲート電極層GE1であり、1対のソース/ドレイン領域SDに挟まれる半導体基板SUBの主表面上に第1のゲート絶縁層GI1を介して形成されている。絶縁性電荷蓄積層ECSは第2のゲート絶縁層GI2に含まれ、1対のソース/ドレイン領域SDに挟まれる半導体基板SUBの主表面上に形成されている。第1のゲート電極層GE1上のコントロールゲート部分CGと第2のゲート絶縁層GI2上のメモリゲート部分MGとは電気的に接続されている。

(もっと読む)

電気ヒューズ回路

【課題】電気ヒューズ回路の省面積化を達成し、かつ電気ヒューズ誤切断防止回路を構築する。

【解決手段】独立した1つの電源スイッチ回路300に加えて、一端が該電源スイッチ回路の出力に接続されたヒューズ素子201と、該ヒューズ素子の他端に接続された第1のMOSトランジスタ202とから構成されるヒューズビットセル200を複数有し、更にESD対策として接地電位と電源スイッチ回路の出力VGBとの間にダイオード400が接続されている。ヒューズビットセル200を構成するトランジスタのゲート酸化膜厚は、高電圧I/O系トランジスタではなく、低電圧ロジック系トランジスタのゲート酸化膜厚と等しくする。

(もっと読む)

不揮発性半導体記憶素子及びその製造方法並びに表示装置

【課題】複雑な工程を経ることなく不揮発性半導体記憶素子を製造する。

【解決手段】不揮発性半導体記憶素子10は、絶縁基板11と、絶縁基板11上に設けられ、ソース領域13s、チャネル領域13c、及びドレイン領域13dが形成された半導体層13と、半導体層13を覆うように設けられたゲート絶縁膜14と、ゲート絶縁膜14内に、半導体層13のチャネル領域13cに対応するように埋設されたメモリ用金属粒子層15と、ゲート絶縁膜14上に、半導体層13のチャネル領域13cに対応するように設けられたゲート電極16と、を備える。

(もっと読む)

半導体装置

【課題】メモリセル領域とその周辺回路領域とを含んで構成される半導体装置において、メモリを構成するMOSFETのしきい値のばらつきを小さくできる半導体装置を提供する。

【解決手段】それぞれMOSFETを有してなる複数のメモリセルが形成されたメモリセル領域とMOSFETを回路が形成された周辺回路領域を備えた半導体装置において、メモリセル領域のMOSFETは、周辺回路領域の少なくとも一部のMOSFETとは異なるゲート構造を有し、ゲート絶縁膜及びゲート電極のうちの少なくとも一方の組成が一部のMOSFETとは異なる。

(もっと読む)

半導体装置及びメモリのデータ書き込み方法

【課題】書き込んだデータの改ざんを防止したメモリ及び半導体装置を提供する。

【解決手段】メモリ回路と、書き込み回路と、読み出し回路と、を具備する構成とする。メモリ回路は、2値データ”0”及び”1”を書き込み可能なメモリセルが複数配置されたメモリセルアレイを含む構成とする。書き込み回路は、メモリ回路に含まれるメモリセルの一に2値データ”0”又は”1”の一方を書き込む第1の書き込み回路と、2値データ”0”又は”1”の他方を書き込む第2の書き込み回路と、を含む構成とする。

(もっと読む)

不揮発性メモリ及びマイクロコンピュータ

【課題】不揮発性メモリの消去動作における基板電流の最大値を低減すること。

【解決手段】本発明の不揮発性メモリ(2)は、半導体基板(30)に形成されたソース電極(53)及びドレイン電極(54)と、ソース電極とドレイン電極間の前記半導体基板上に形成された電荷トラップ層(52)と、電荷トラップ層上に配置されたゲート電極(50)とを有する不揮発性メモリセルがアレイ状に複数配列されて成る。不揮発性メモリは、ソース電極とゲート電極とに消去に必要な電圧を印加する消去モードを有する制御回路(33)を備える。前記消去モードにおいて、ゲート電極に電圧の印加を開始してから前記ゲート電極の電圧が消去に必要な所定電圧に達するまでの期間(63)が、ソース電極に電圧の印加を開始してから前記ソース電極の電圧が前記所定電圧に達するまでの期間(64)よりも長くされる。これによって、消去動作における基板電流の最大値が抑えられる。

(もっと読む)

141 - 160 / 302

[ Back to top ]